++++++++++++++++++++++++++++++++++++++++++

本文系本站原创,欢迎转载! 转载请注明出处:

http://blog.csdn.net/mr_raptor/article/details/6556258

++++++++++++++++++++++++++++++++++++++++++

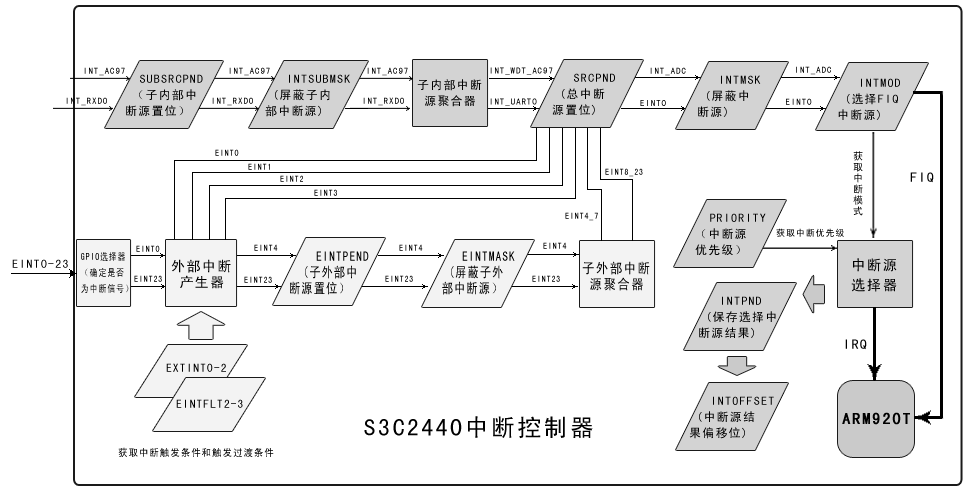

中断源按照硬件位置分为外部中断源和内部中断源,外部中断源和内部中断源又包含子外部中断源和子内部中断源,如上图所示(画了一整天)。

1. 子内部中断源的产生

以UART0接收数据产生INT_RXD0中断为例,INT_RXD0产生后进入SUBSRCPND子中断源暂存寄存器,设置INT_RXD0对应的中断位,中断信号经过INTSUBMSK子中断屏蔽寄存器,如果INT_RXD0信号对应位没有被置位(屏蔽掉),中断信号继续向前传递,经过子内部中断源聚合器,将INT_RXD0聚合成对应的中断源信号INT_UART0,设置SRCPND中断源暂存寄存器里INT_UART0位,经过INTMSK中断屏蔽寄存器,如果INT_UART0信号没有被屏蔽掉,中断信号进入INTMOD中断模式寄存器判断是否为快速中断,如果被编程为快速中断,直接打断ARM内核,进入中断处理,如果中断信号为一般中断,进入中断优先级仲裁器进入优先级仲裁,如果INT_UART0信号为最高优先级或只有INT_UART0中断信号产生,则该中断信号被记录到INTPND最高优先级中断暂存寄存器,同时设置INTOFFSET的值为中断号28,最终将中断信号打断ARM内核进行中断处理。如果同时产生多个中断且INT_UART0不是最高优先级,则该中断信号不会被处理,等最高优先级信号处理完后,再次进行优先级仲裁,也就是说中断信号不消失,一直保存在SRCPND里,只到被处理为止。

2. 内部中断源的产生

该过程在子内部中断处理过程中已经包含,中断信号产生后直接进入SRCPND里,然后经历上述子内部中断后期处理过程。

3. 子外部中断的产生

外部中断源共有24个,其中EINT0~EINT3为外部中断源,EINT4_7,EINT8_23为复合中断源,他们包含有子外部中断源。

由于外部硬件直接挂接到I/O Ports(详见S3C2440A硬件手册第9章)上的,我们要想让外设硬件中断得到处理,要先从EINT0~EINT23里选择中断信号,我们以EINT11为例,介绍子外部中断处理过程。

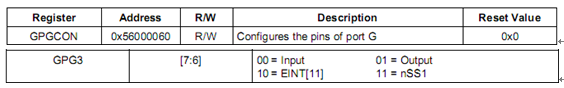

通常CPU内部引出引脚都是复用的,也就是说一根CPU引脚可以有多种功能,可以设置其为输入信号线,输出信号线或中断信号线,要想让硬件产生中断,首先要对可以产生中断的引脚进行编程,设置该引脚为中断信号线。EINT11中断信号对应CPU引脚为GPG3,通过设置GPGCON[7:6] = 0b10,可以设置该引脚为中断信号线。

表3-14 GPGCON寄存器

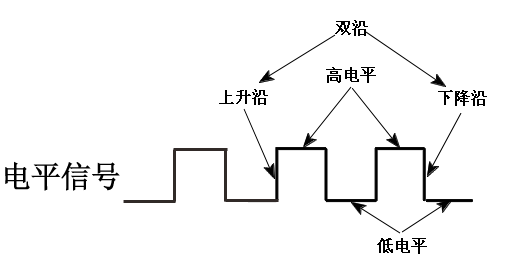

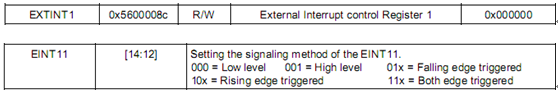

设置了CPU管脚为中断信号线之后,还要通过设置EXTINT0寄存器来指定中断信号的触发方式:高电平触发,低电平触发,电平上升沿,下除沿,双沿触发。

图3-9 电平信号触发示意图

由于按键按下时让它产生中断,也就是从高电平变为低电平时产生(上节按键中断原理),因此我们设置EINT11中断信号的触发方式为下降沿触发,EXTINT1[14:12] = 0b01x

表3-15 EXTINT1寄存器

设置完触发方式之后,当外设中断信号线上的电平达到触发条件时,通过外部中断产生器产生中断信号,然后将子外部中断暂存寄存器EINTPND中对应的EINT11位置1,中断信号再进入EINTMSK子外部中断屏蔽寄存器,如果EINT11中断源信号没有被屏蔽,则EINT11中断信号进入子外部中断聚合器,复合成EINT8_23中断信号,然后再经历与前面子内部中断信号一样的处理机制。

(1)EINTPEND外部中断暂存寄存器

表3-16外部中断暂存寄存器(EINTPEND)

| 寄存器名 |

地址 |

是否读写 |

描述 |

复位默认值 |

| EINTPEND |

0x560000A8 |

R/W |

外部中断信号暂存寄存器 0:没有中断请求信号 1:中断请求信号产生 |

0x0000000 |

| EINTPEND |

位 |

描述 |

初始值 |

| EINT23 |

[23] |

0 = 未产生中断 1 = 产生中断 |

0 |

| … |

… |

… |

… |

| EINT4 |

[4] |

0 = 未产生中断 1 = 产生中断 |

0 |

| 保留位 |

[3:0] |

无 |

0000 |

(2)EINTMASK外部中断屏蔽寄存器

表3-17外部中断屏蔽寄存器(EINTMASK)

| 寄存器名 |

地址 |

是否读写 |

描述 |

复位默认值 |

本文详细介绍了ARM系统中断的产生流程,包括子内部中断源、内部中断源和子外部中断源的处理过程。从中断源触发到中断处理,涉及中断暂存寄存器、中断屏蔽寄存器和中断模式寄存器等多个环节。并通过按键控制LED灯实验展示了中断在实际应用中的操作步骤。

本文详细介绍了ARM系统中断的产生流程,包括子内部中断源、内部中断源和子外部中断源的处理过程。从中断源触发到中断处理,涉及中断暂存寄存器、中断屏蔽寄存器和中断模式寄存器等多个环节。并通过按键控制LED灯实验展示了中断在实际应用中的操作步骤。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1455

1455

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?