并口通信是最常用基础功能,实现ARM9与FPGA的并口通信有两种方式,一种颇为巧妙,利用SMC(Static Memory Controllor),其中的使能点都通过寄存器可以轻松控制;另一种方式就是通过GPIO来完成。

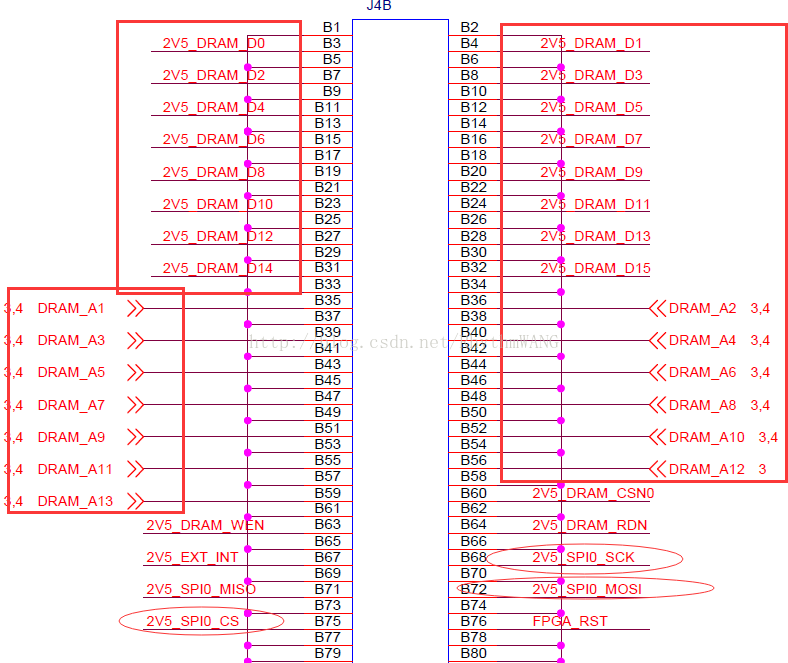

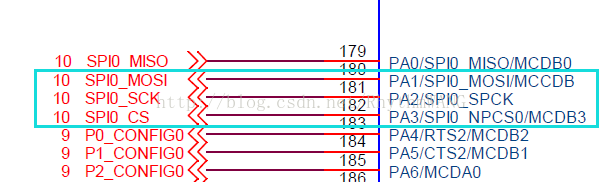

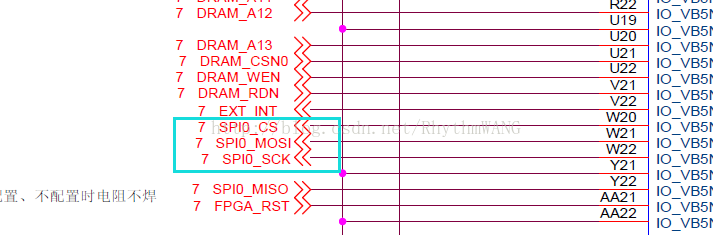

由于我拿到板子硬件的DRAM_CSN0、DRAM_WEN和DRAM_RDN在前期PCB设计时没有充分考虑过SMC可能被使用,故使用接插件上其他引脚进行代替,使用了图1中画圈的三根引脚SPI0_MOSI、SPI0_SCK、SPI0_CS。因为这三根引脚可以复用为GPIO,所以在并口调试中将这三根引脚当作GPIO来使用。

图1

图2

图3

表1

| 原SPI功能 |

GPIO |

FPGA引脚 |

功能 |

| SPI0_MOSI |

PA1 |

W21 |

写使能 |

本文介绍了ARM9与FPGA之间的并口通信实现,包括通过SMC和GPIO方式,着重讨论了GPIO模式下的初始化配置和数据读写的详细步骤,提供了寄存器配置及信号时序分析。

本文介绍了ARM9与FPGA之间的并口通信实现,包括通过SMC和GPIO方式,着重讨论了GPIO模式下的初始化配置和数据读写的详细步骤,提供了寄存器配置及信号时序分析。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

924

924

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?