设计该开发板的初衷是为了学习,但也希望今后能扩展其功能,看到大家都在diy示波器,自己也非常冲动的想DIY一把,于是呼选了arm+fpga的方案,fpga主要用来实现数据的高速采样,而ARM则提供数据的显示,以及一些人机交互的功能。那么该方案中最重要的地方就是ARM和FPGA之间的通信如何实现了。在网上查了很多的资料,有说将FPGA作为ARM的一个外设,可以通过DMA的方式来直接访问;也有说把FPGA当做arm的一个存储设备,可以通过总线的方式将FPGA挂载到ARM的一个bank,这样就可以通过向访问存储器那样来访问FPGA,在linux系统中应该是通过ioremap这个函数来访问存储器,那么也就是说可以用ioremap来访问FPGA。

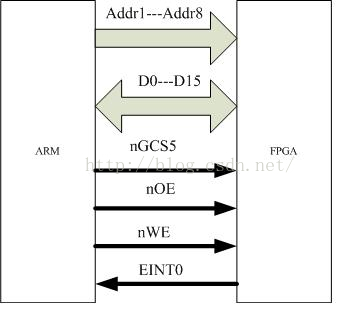

ARM 和FPGA之间连接的功能图如下所示:

如上图所示,Addr1---Addr8为地址总线,D0---D15为数据总线,nGCS5为ARM的bank片选,nOE为读使能信号,nWE为写使能信号,EINT0为中断信号。

s3c2440的 bank0-

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1532

1532

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?