引言

如果把SOC比作一个人的话,那么clock系统就是人的脉搏,起着至关重要的作用。本小节就简单分析一下,ORPSoC的时钟系统。

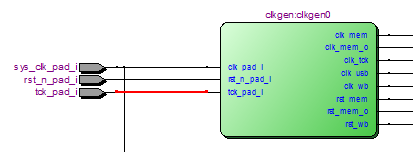

分为三部分:clk,rst,tck

1,clk部分

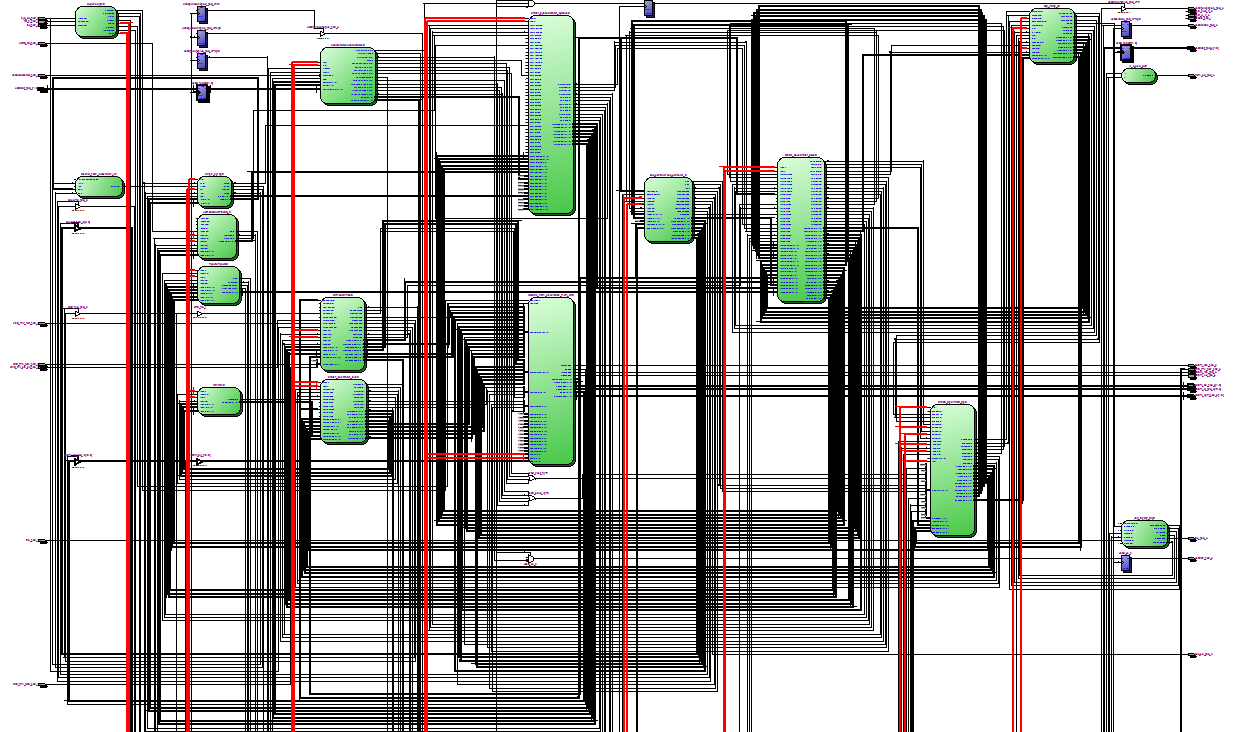

为了看到整个clk系统,我们从源头开始寻找,一直找到芯片内部的分布。

1.1 clk路径梳理:

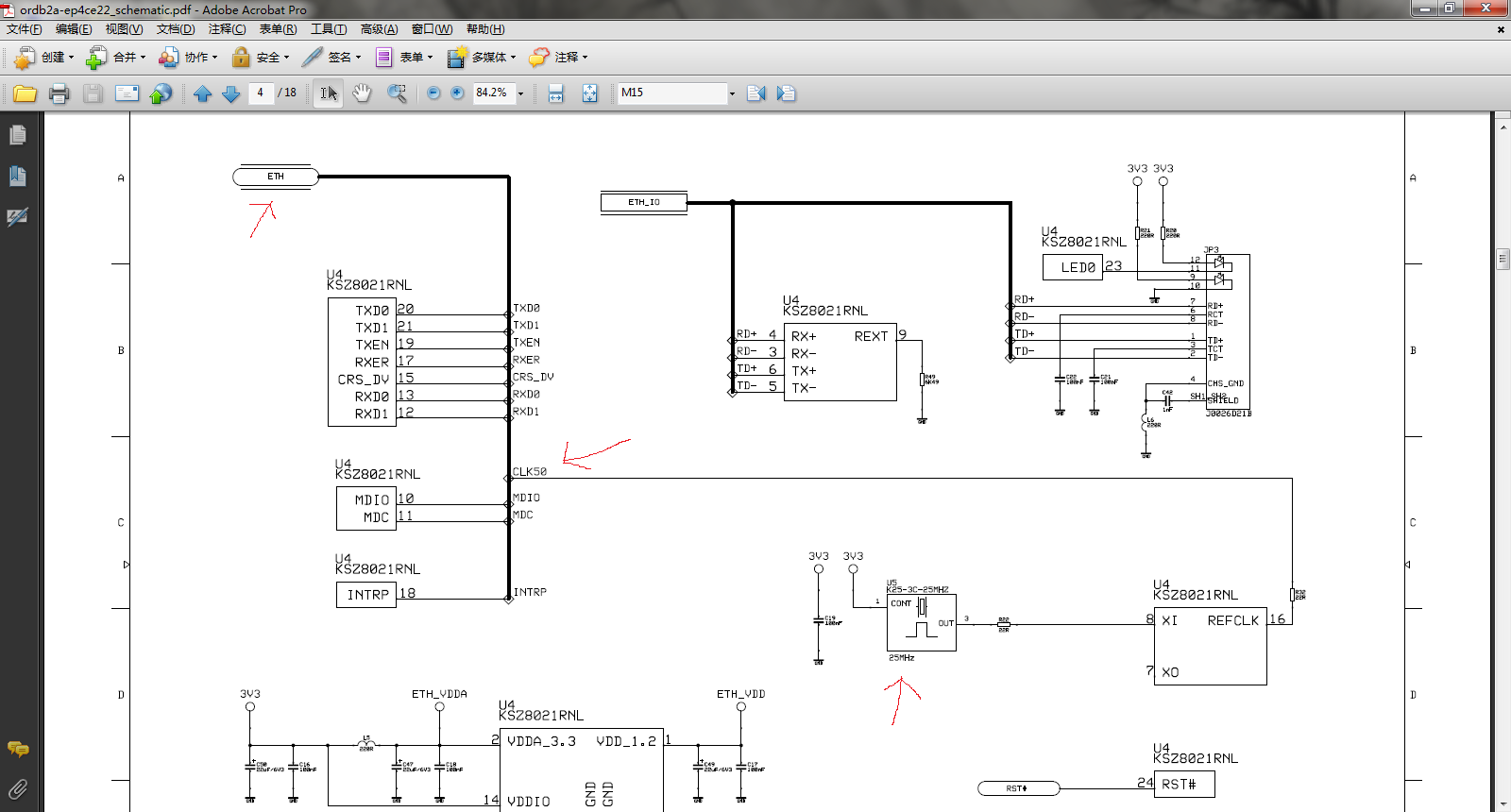

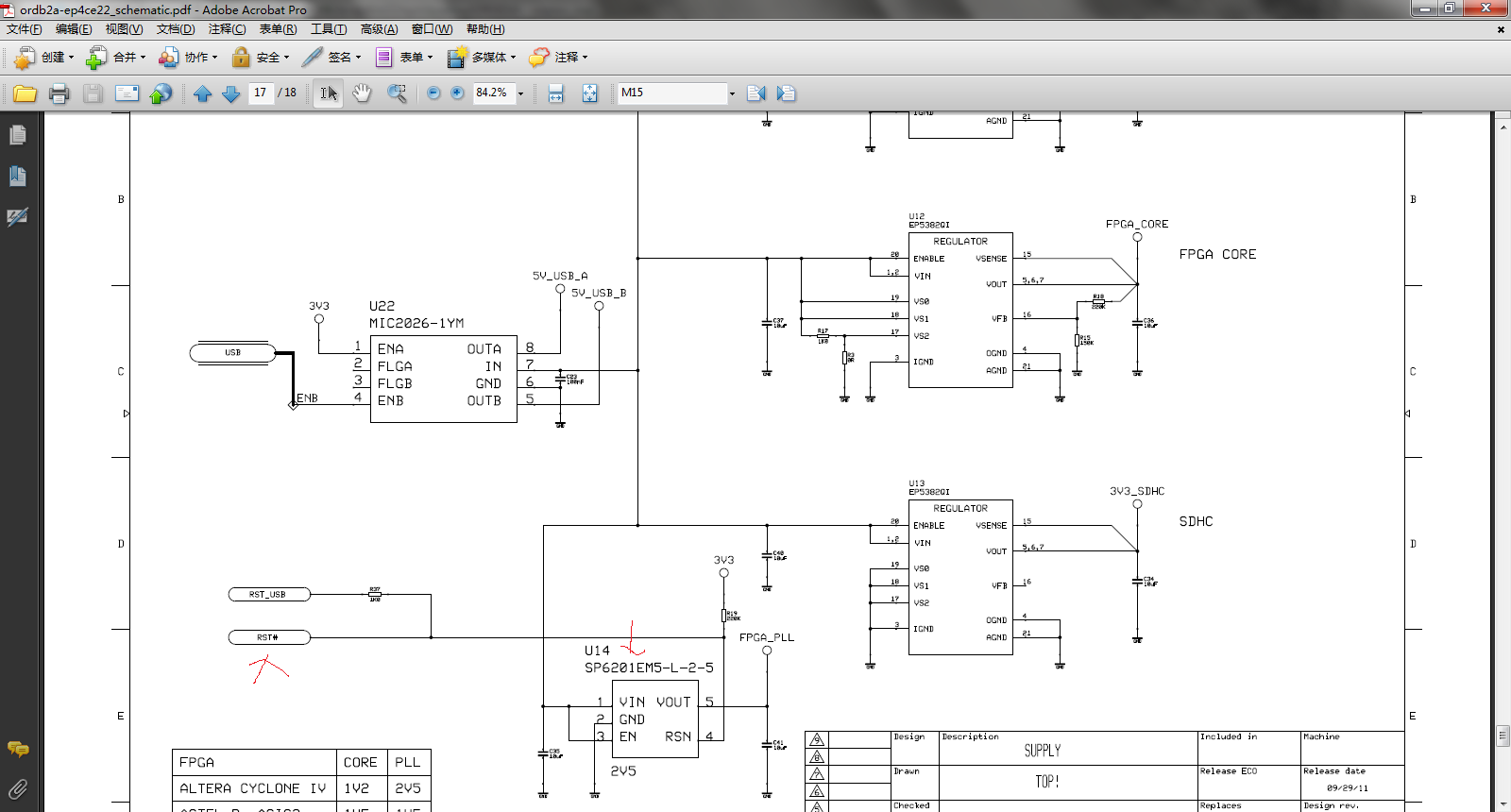

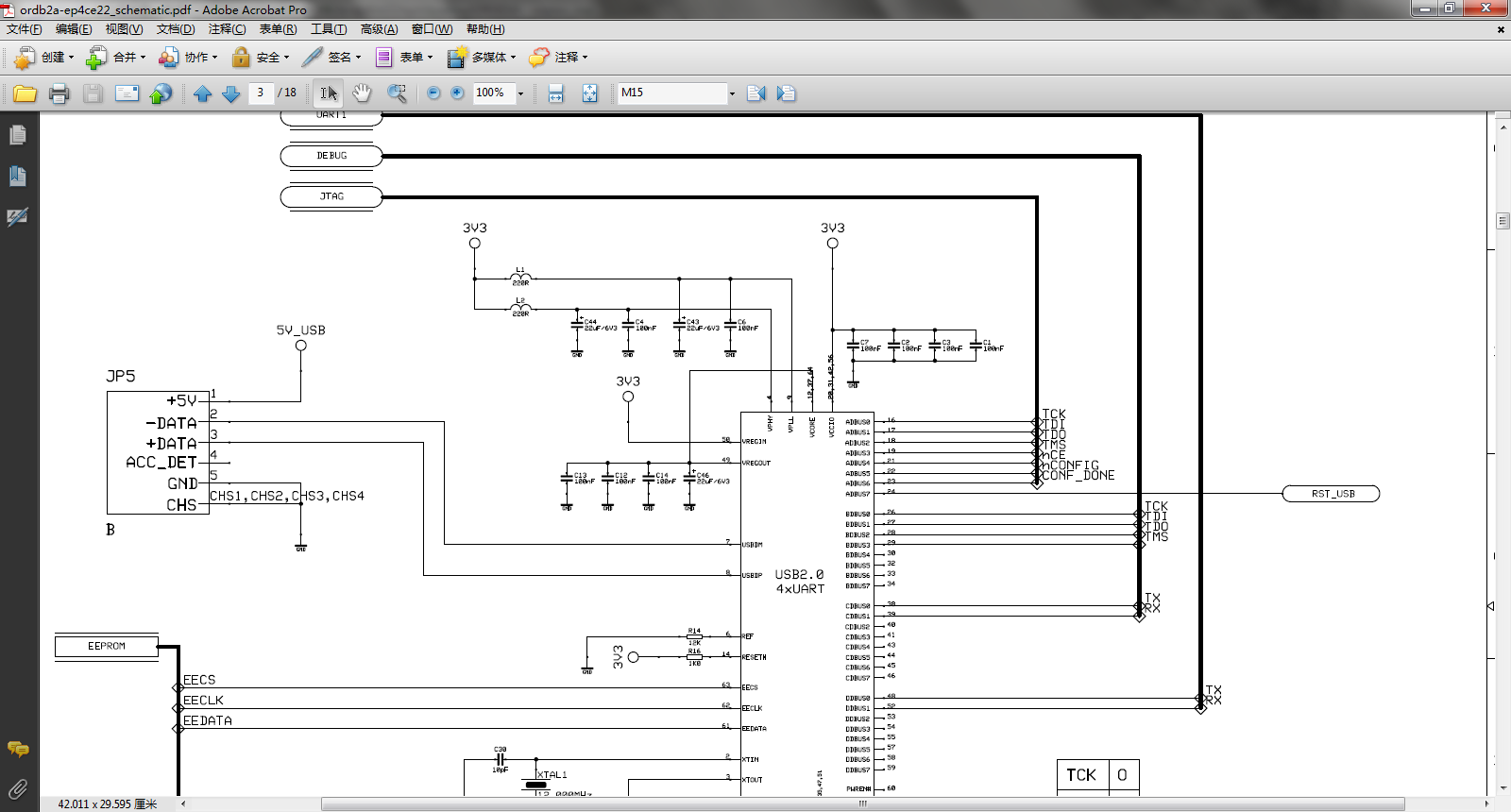

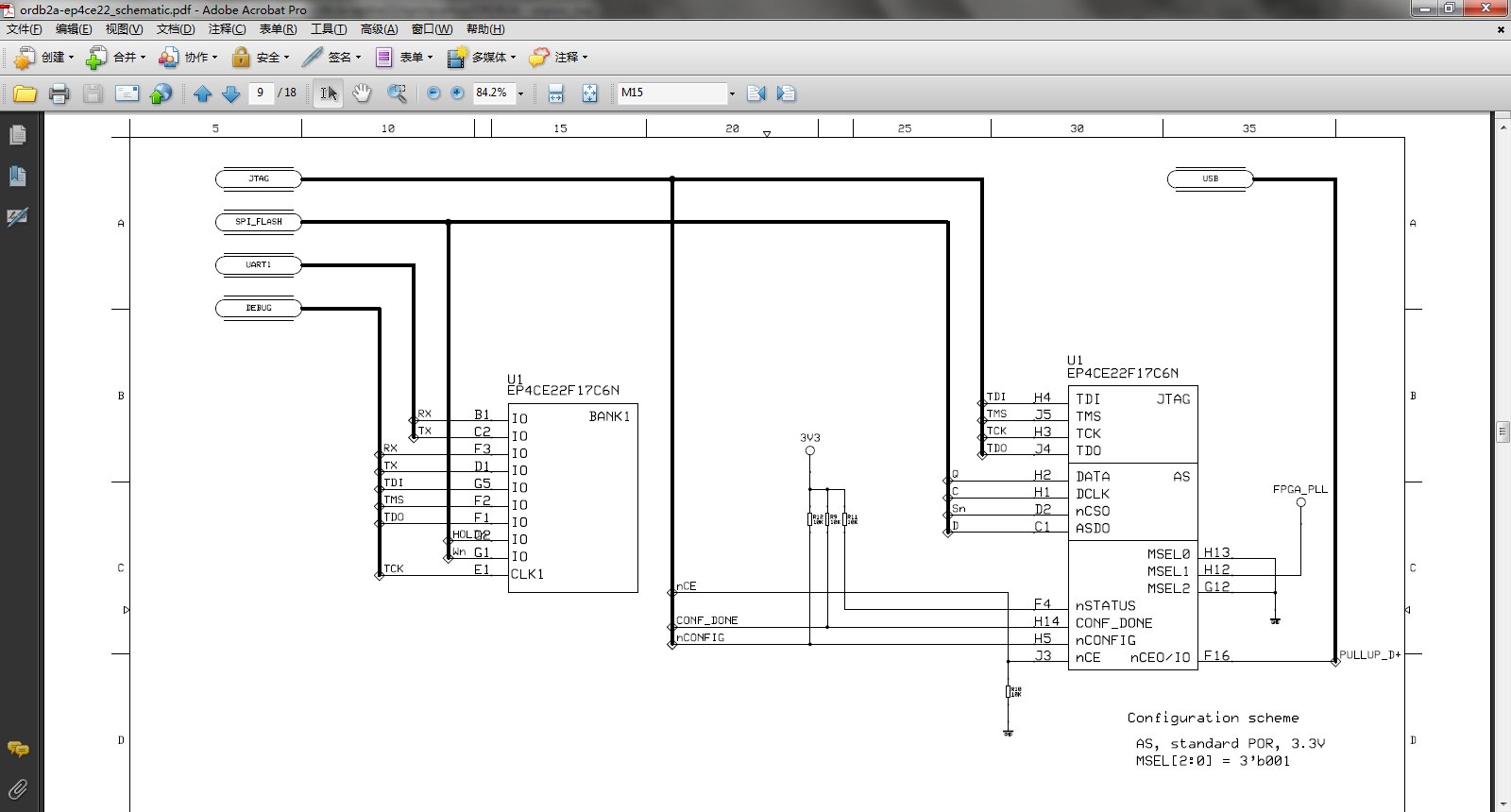

可以看到clk由U5产生,输入为25MHz,输出为50MHz。“ETH”连到哪里了呢?

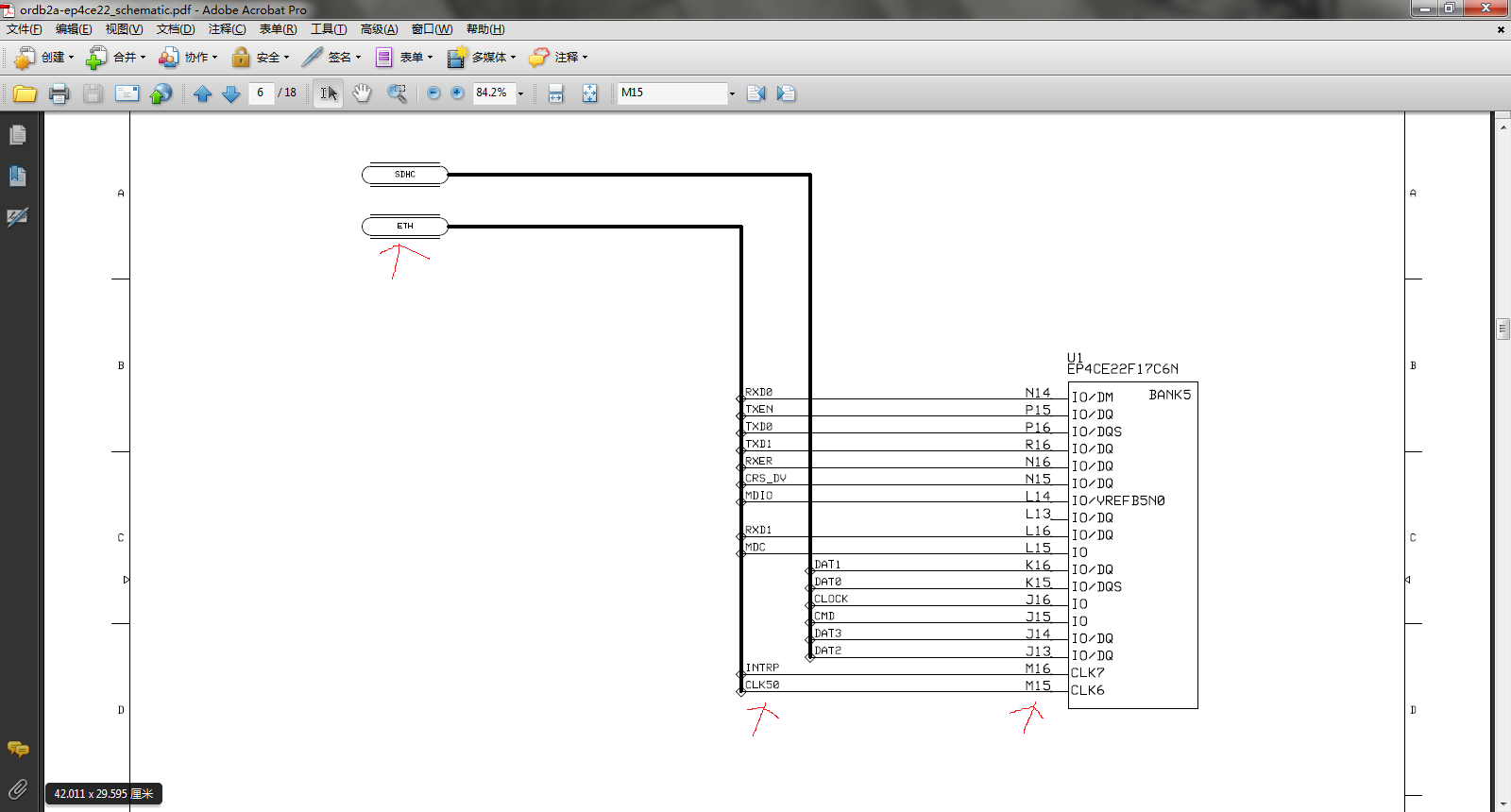

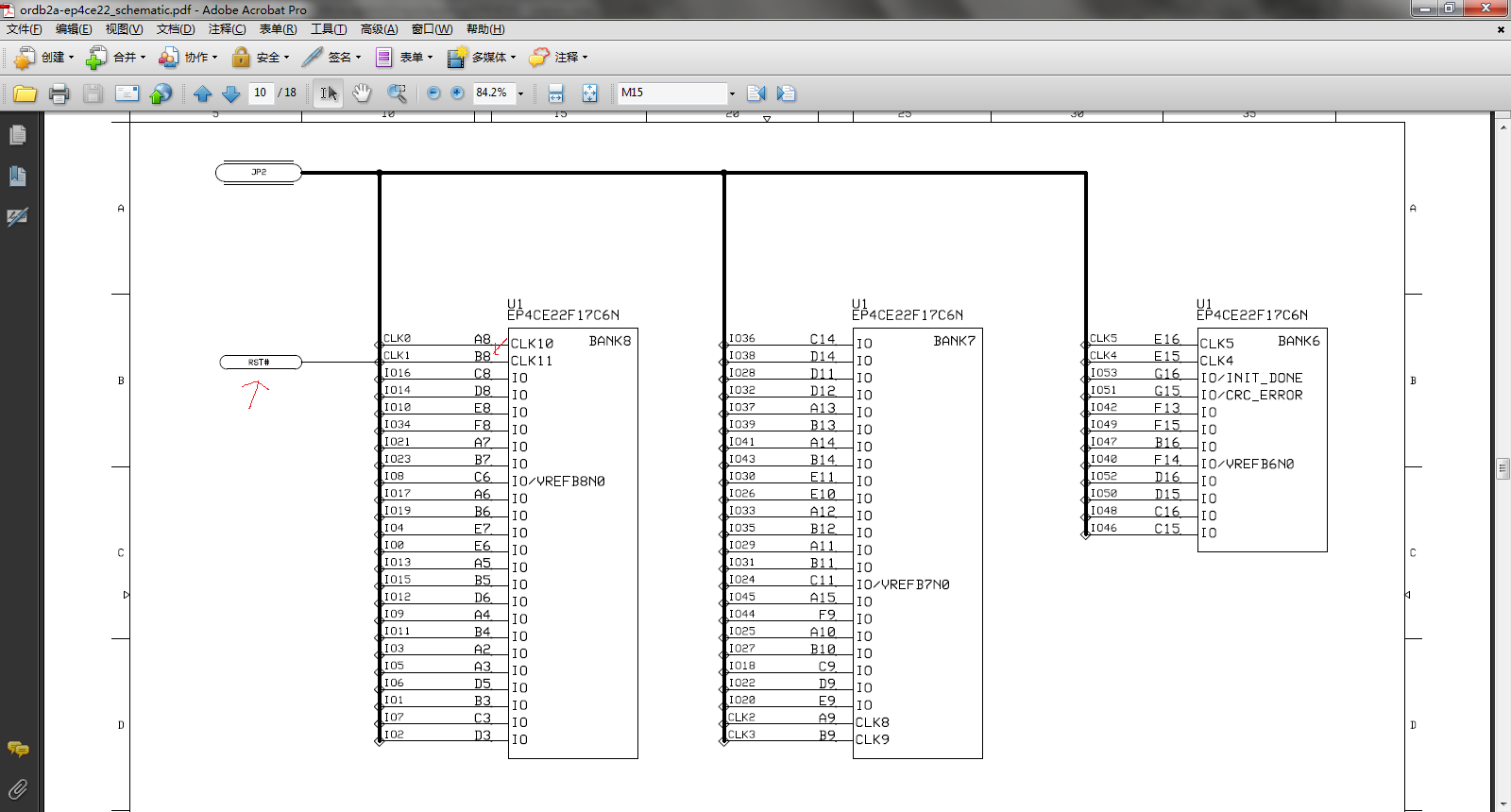

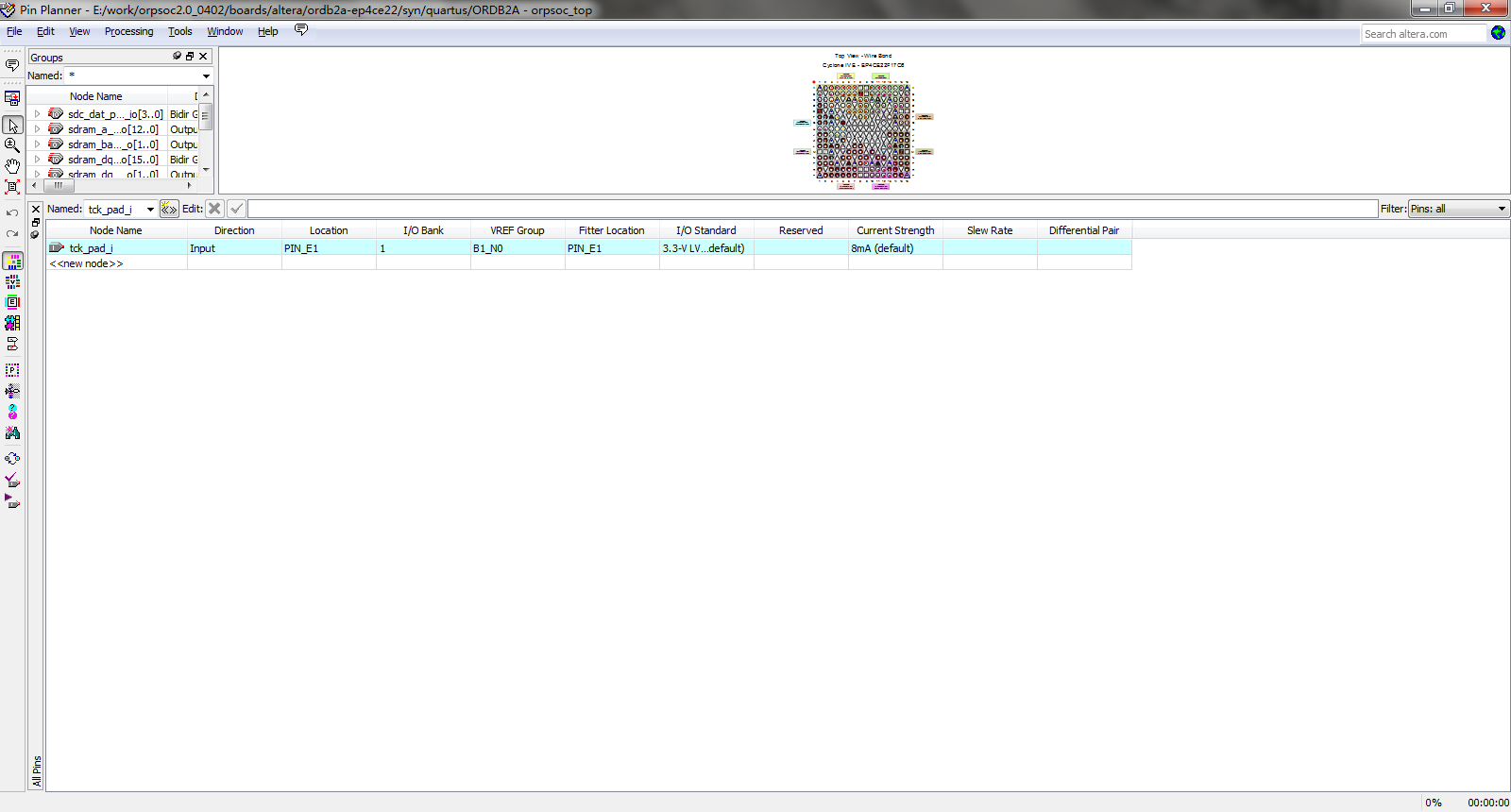

可以看到clk与FPGA的M15引脚相连,M15连到哪里了呢?

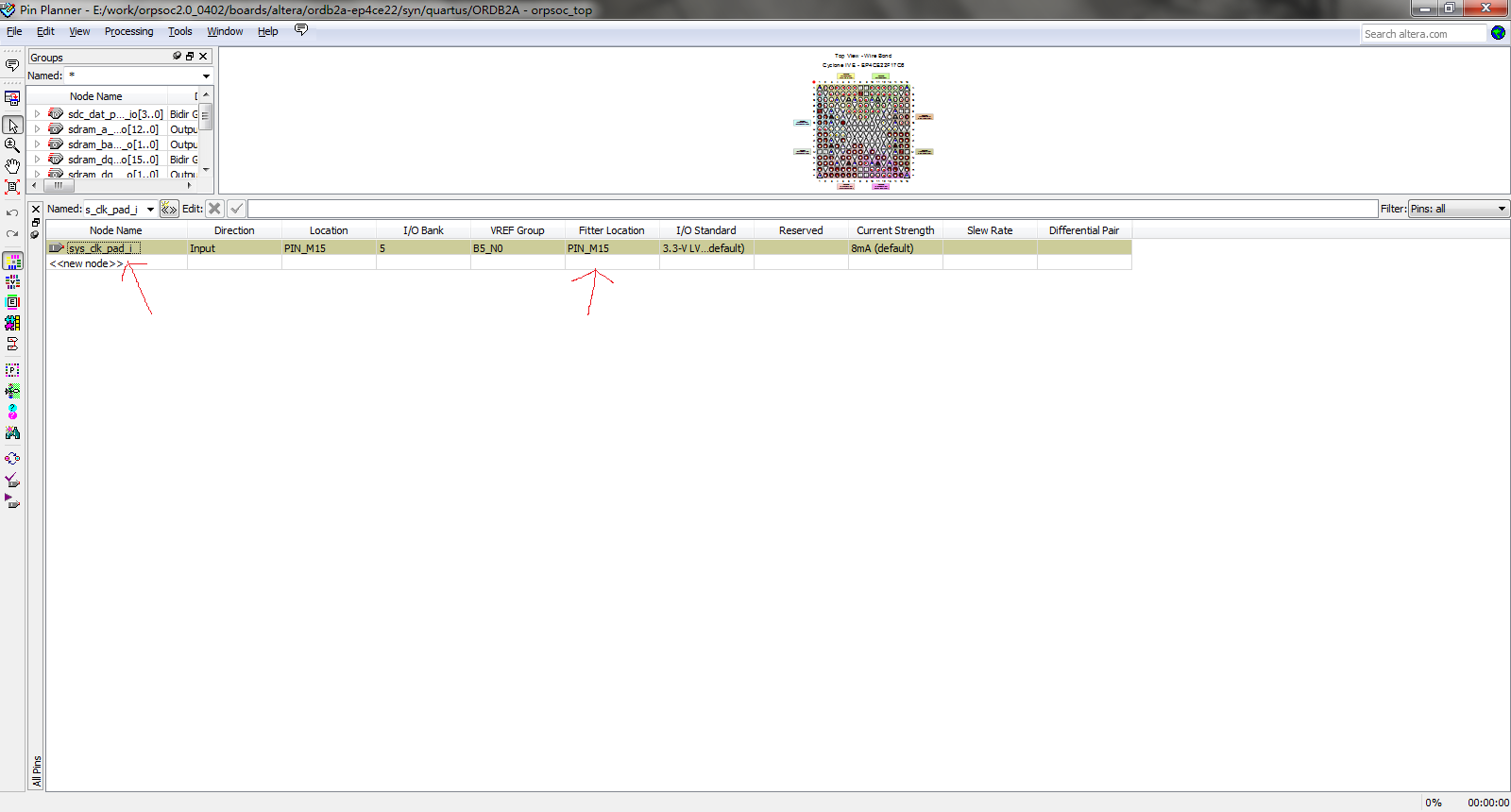

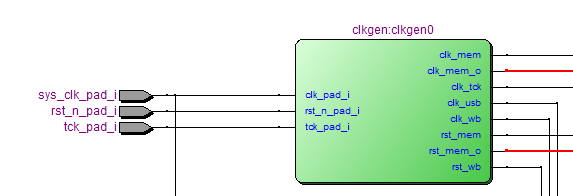

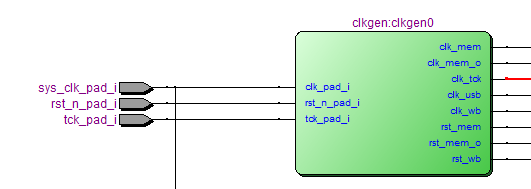

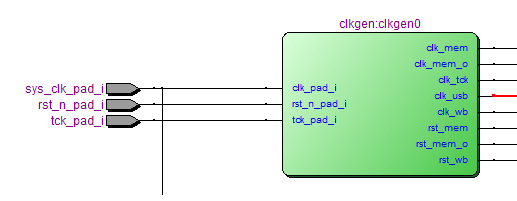

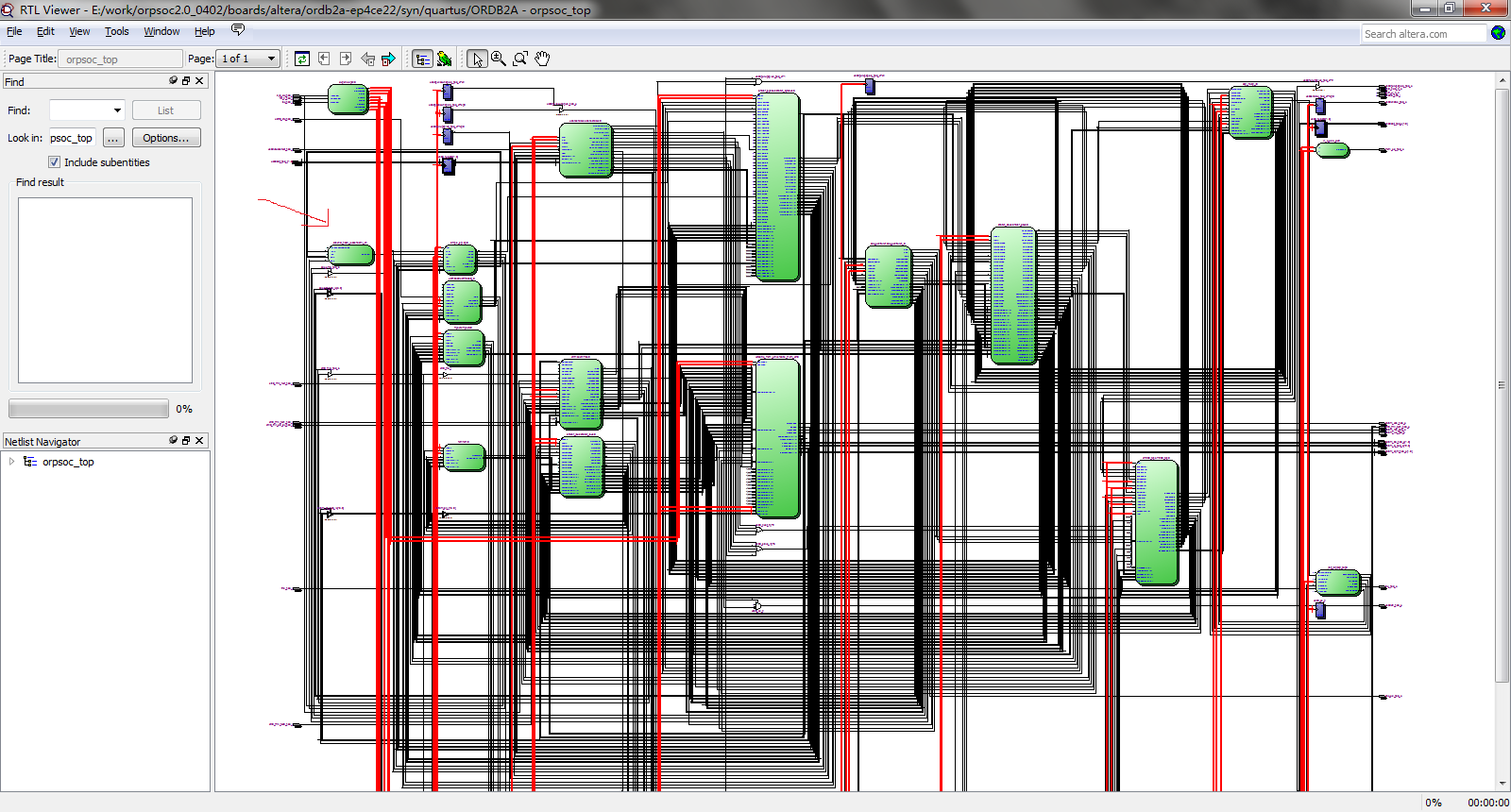

连到了sys_clk_pad_i,这个又连到哪里了呢?

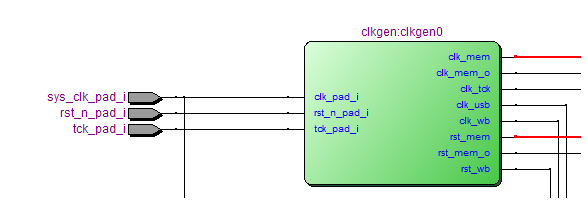

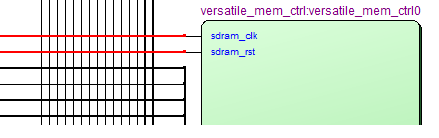

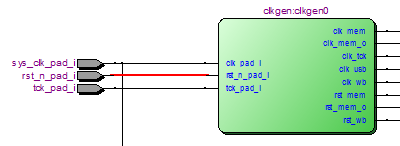

连到了clkgen模块,然后由这个模块扇出5路:(clk_mem, clk_mem_o, clk_tck, clk_usb, clk_wb)

1.2 具体每一路的扇出情况如何呢:请看以下图片:

1>clk_mem:

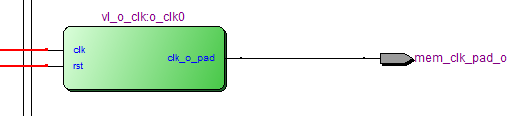

2>clk_mem_o:

3>clk_wb:

4>clk_tck:

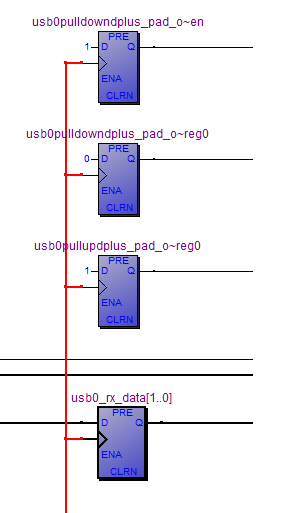

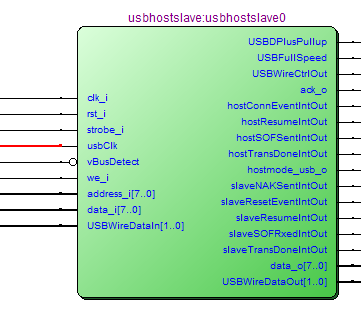

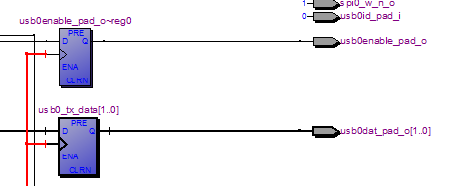

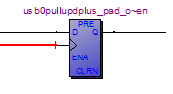

5>clk_usb:

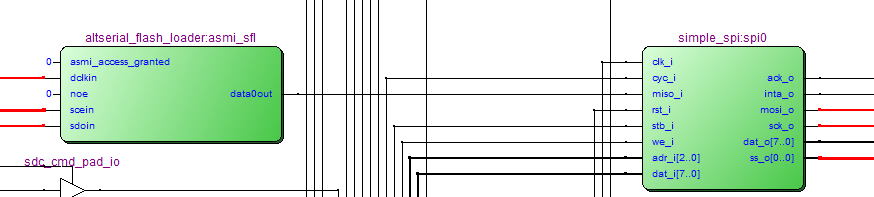

6>目前的状况,这5路扇出包含了ORPSoC的所有的模块了吗?我们看一下:发现还有一个模块(箭头指向)。

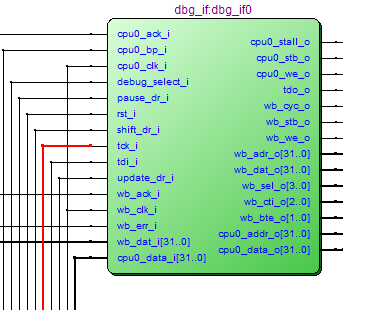

这个模块的时钟由谁提供呢,如下图:

7>clk小结

时钟50MHz,FPGA引脚为M15,进入FPGA内部后由clkgen模块实现时钟的分发,给其他模块提供clk。

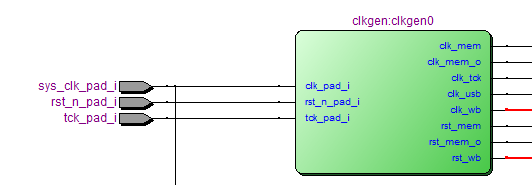

2,rst系统

复位也是一个关键的信号,分析如下:

3, tck系统

tck负责给jtag和debug_if模块提供clk.请参考clk部分的clk_tck.

4,小结

本小节将ORPSoC的时钟,复位和tck部分进行了梳理。

本文详尽分析了ORPSoC的clock子系统,包括clk路径梳理,从源头25MHz到50MHz的转换,以及clk如何通过clkgen模块扇出至clk_mem、clk_mem_o、clk_wb、clk_tck和clk_usb等五路。此外,还探讨了rst系统和tck系统,特别是tck如何服务于JTAG和debug_if模块。

本文详尽分析了ORPSoC的clock子系统,包括clk路径梳理,从源头25MHz到50MHz的转换,以及clk如何通过clkgen模块扇出至clk_mem、clk_mem_o、clk_wb、clk_tck和clk_usb等五路。此外,还探讨了rst系统和tck系统,特别是tck如何服务于JTAG和debug_if模块。

2615

2615

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?