本编文章将使用Zynq开发平台Miz702上的ADAU1761音频编解码芯片,进行采样模拟音频信号(2路),转成数字信号,然后再通过ADAU1761转成模拟信号输出(2路)。在此基础上通过左右声道相减,简单的实现人声消除。本文不介绍ADAU1761驱动的编写方法,直接采用 Ali Aljaani编写的IP。

ADAU1761参数的配置参考 ADA1761 Datasheet

本文所使用的开发板是Miz702(兼容zedboard)

PC 开发环境版本:Vivado 2015.2 Xilinx SDK 2015.2

3.5mm公对公的音频连接线一根

ADA1761驱动IP core下载

建立vivado工程

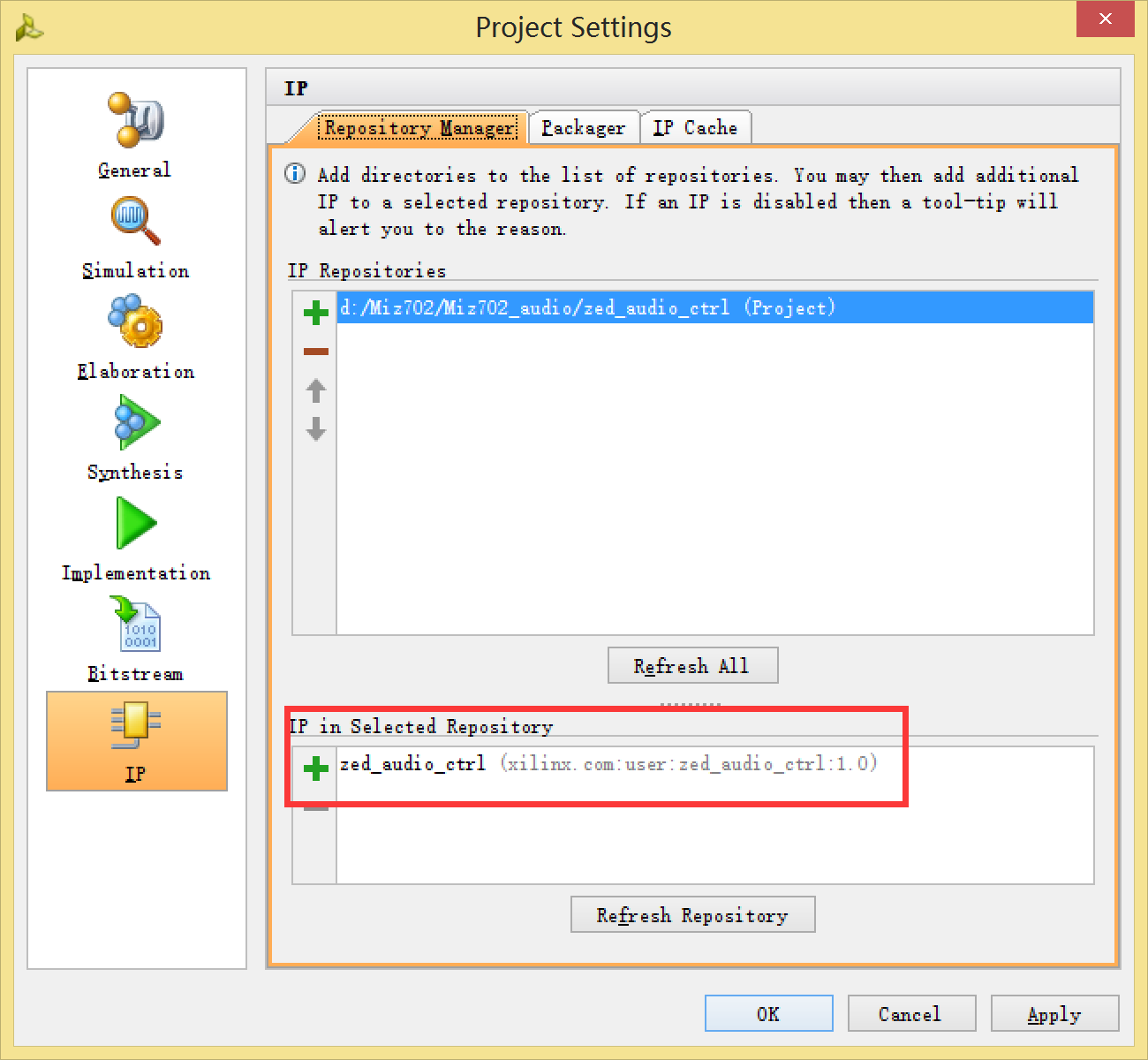

建好工程之后,把下载好的IP添加到IP Repository里面,如图所示

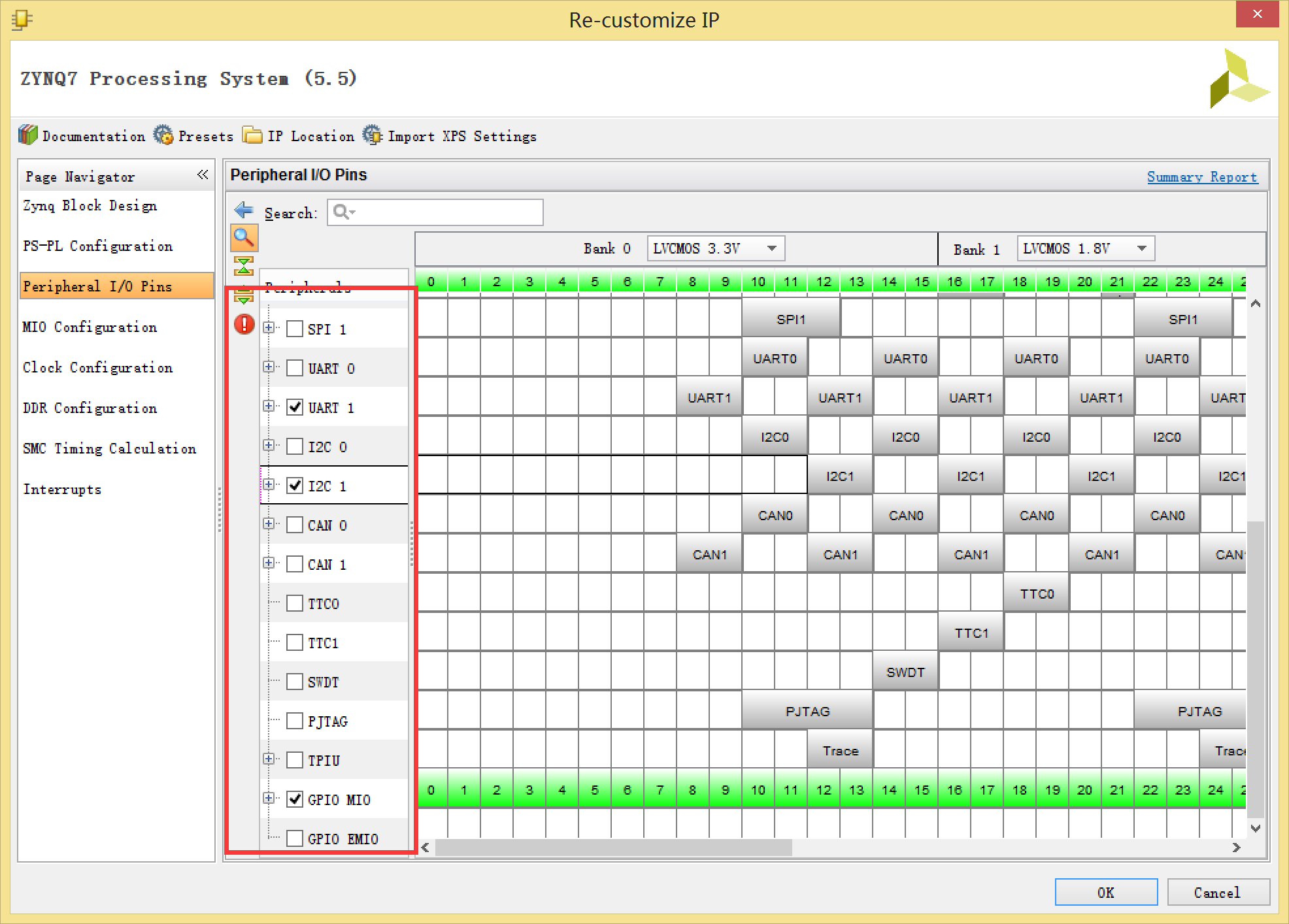

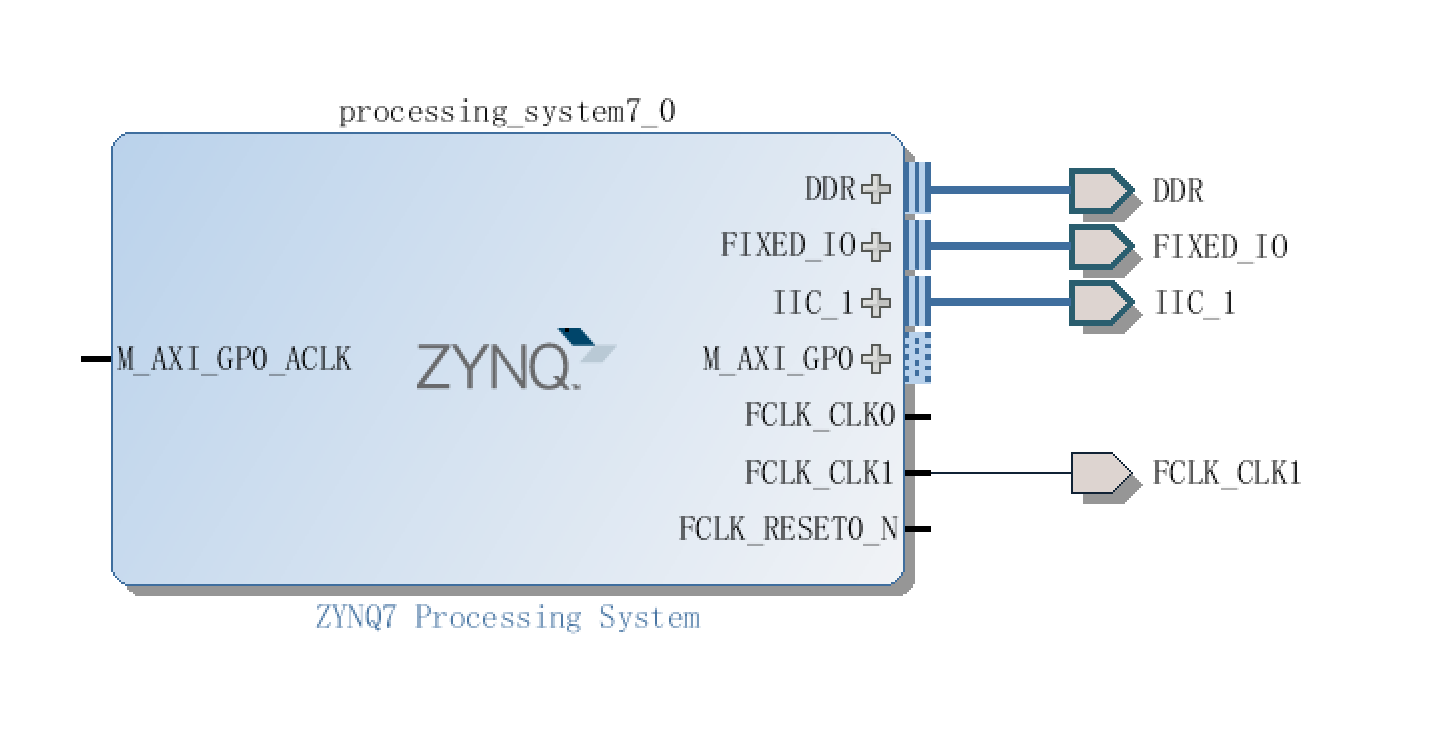

点击Create Blcok Design,完成后点击Add IP,把ZYNQ PS,添加进来,然后双击ZYNQ,进行如下配置

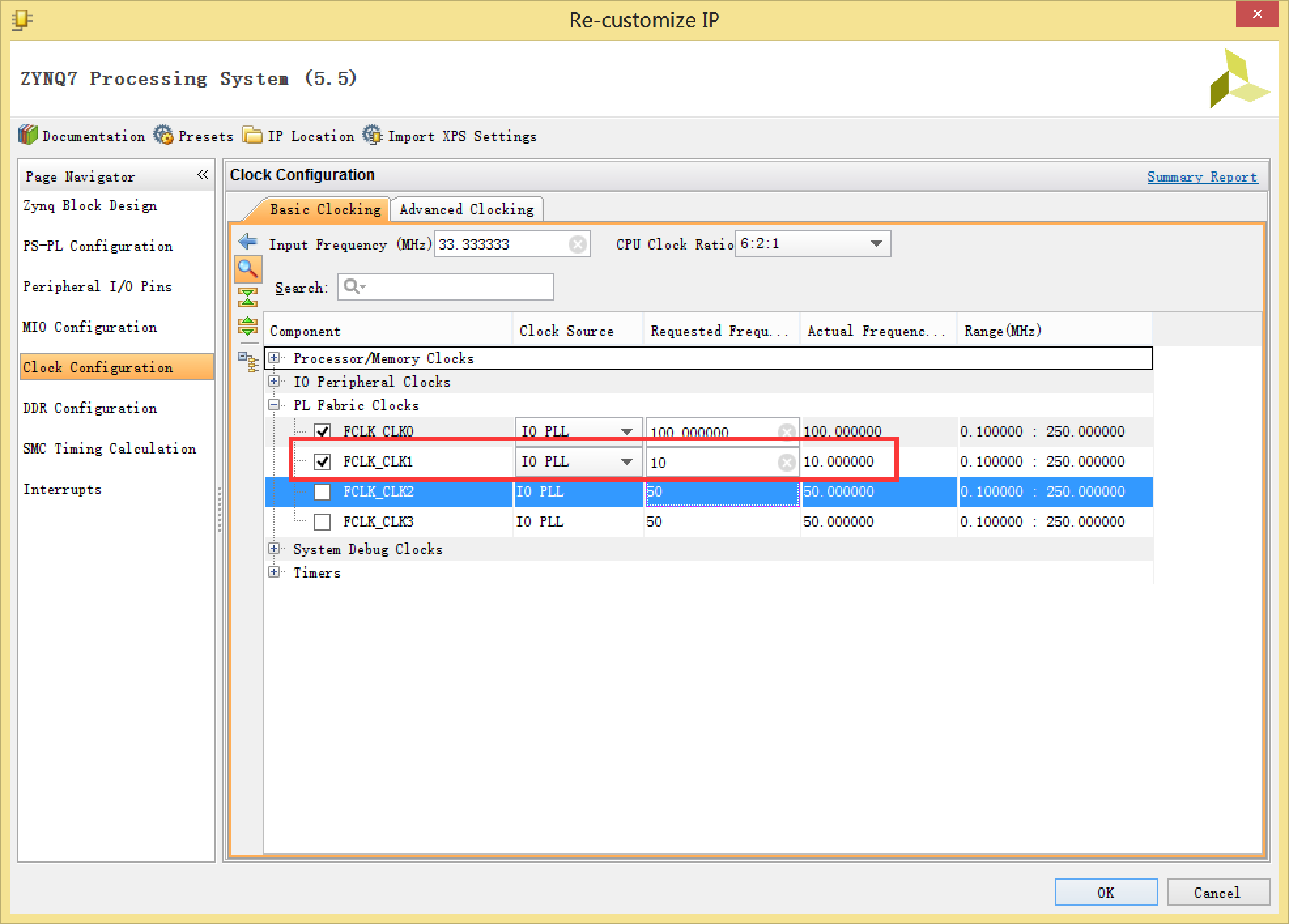

在Clock Configuration下,使能FLCK_CLK1,并且把时钟配置成10Mhz,如图所示

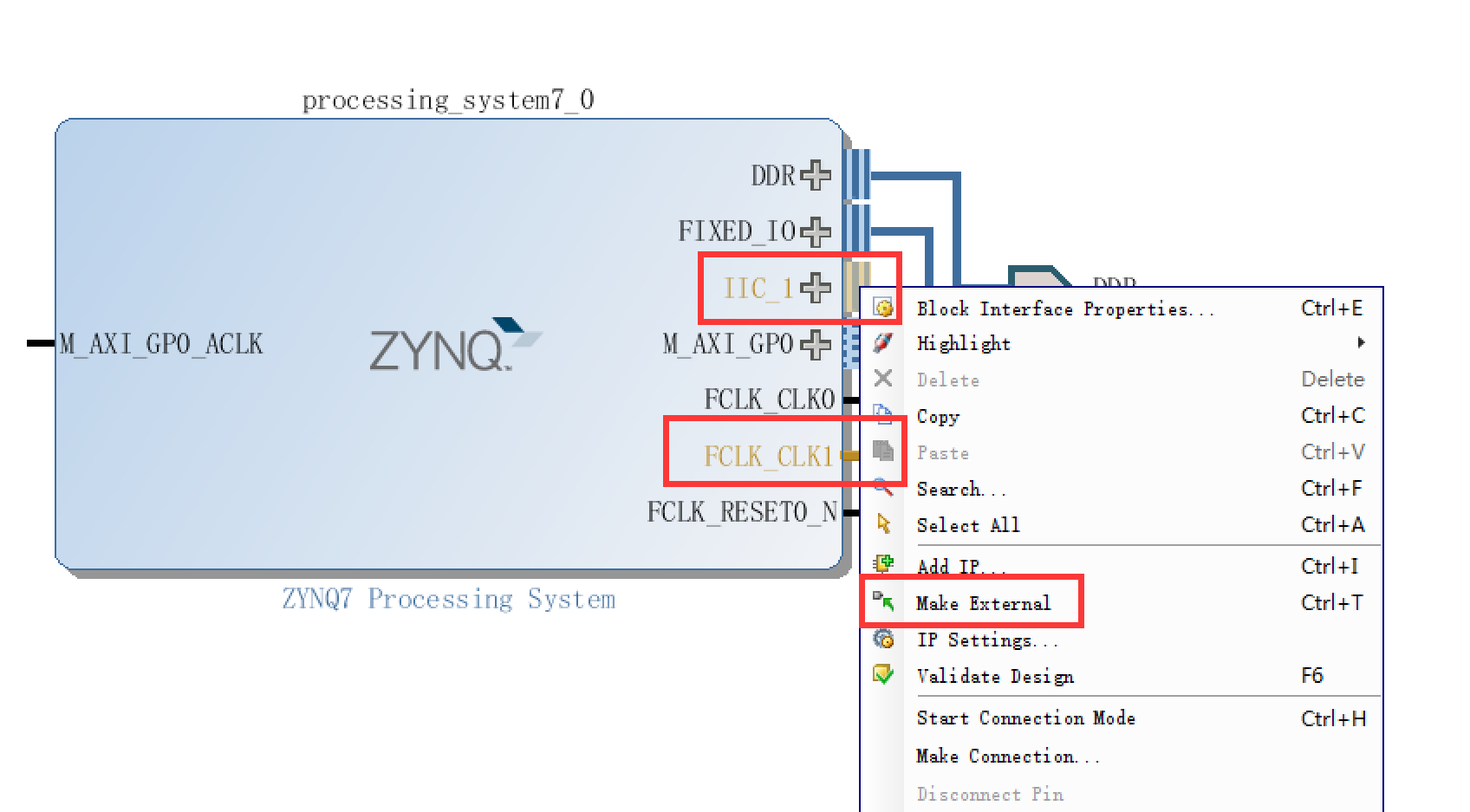

选中IIC_1和FCLK_CLK1,右击,点击Make external

结果如图所示

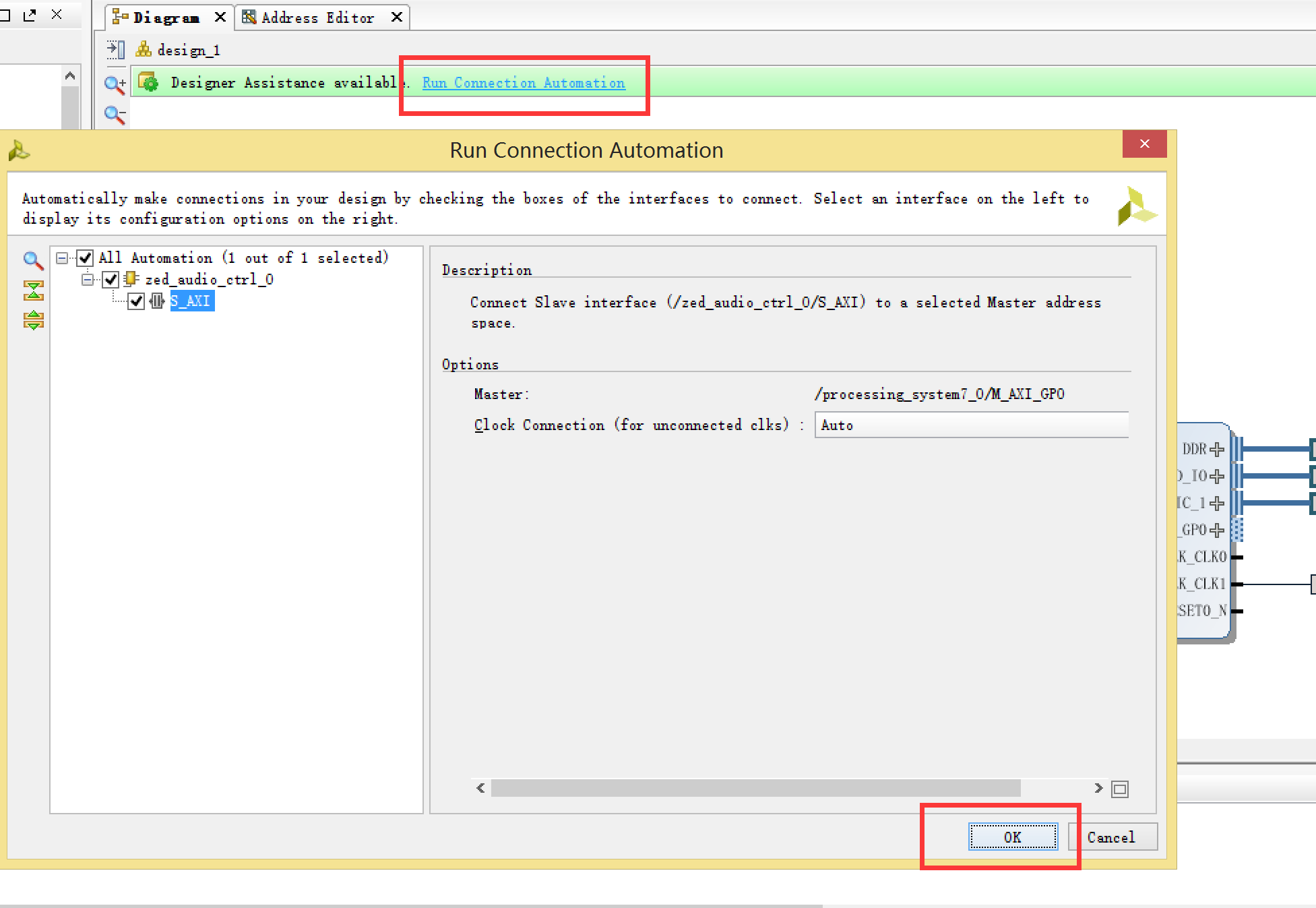

点击Add IP,添加zed_audio_ctrl IP,添加好之后点击Run Connection Automation

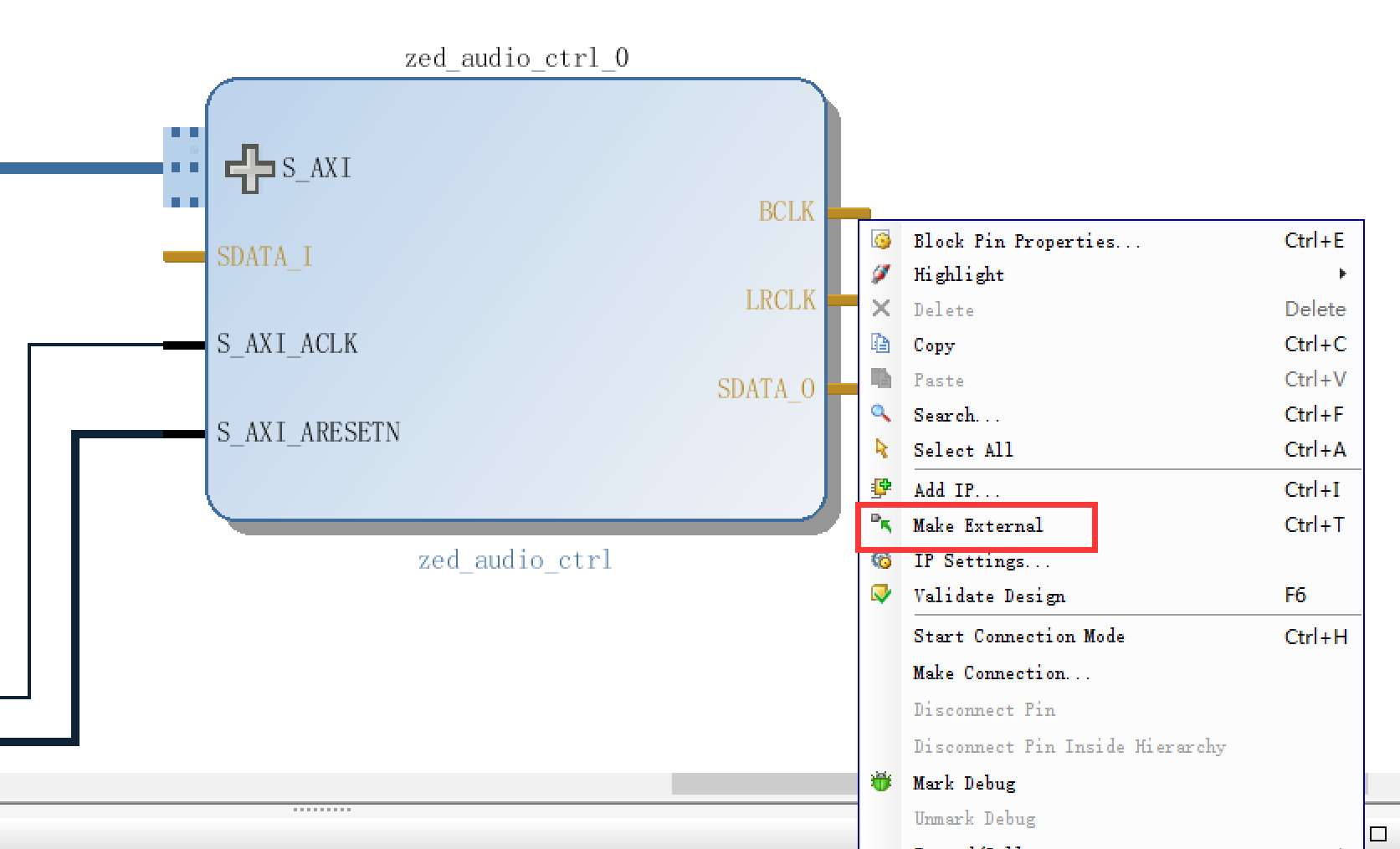

选中zed_audio_ctrl上其余的接口,右击,Make external

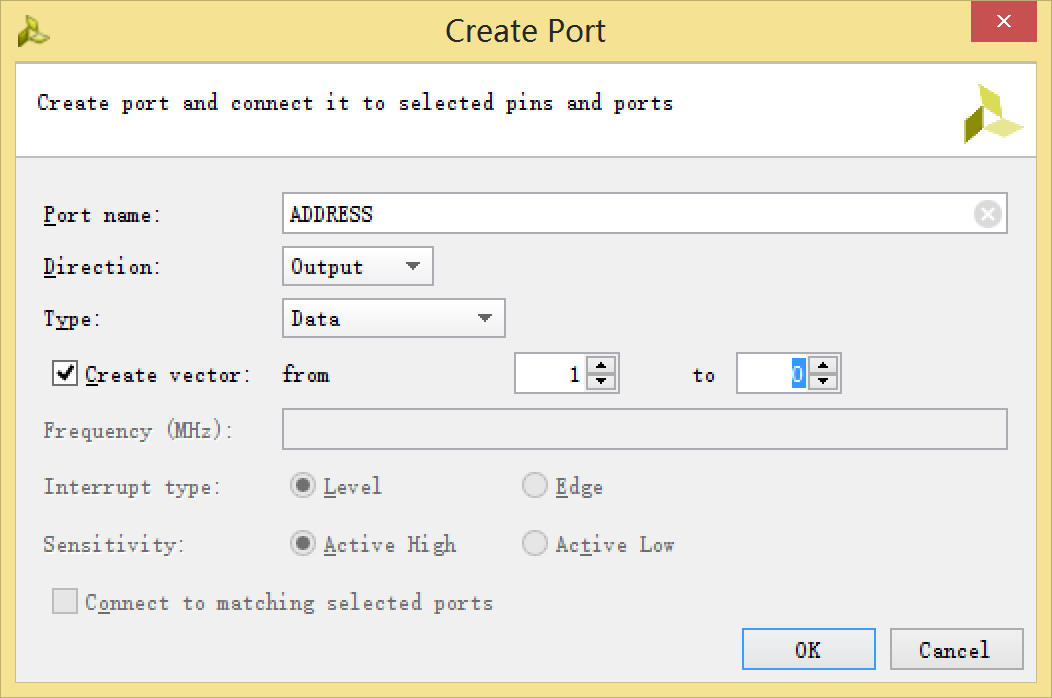

在空白处右击,选择Create port

然后按照如图所示配置

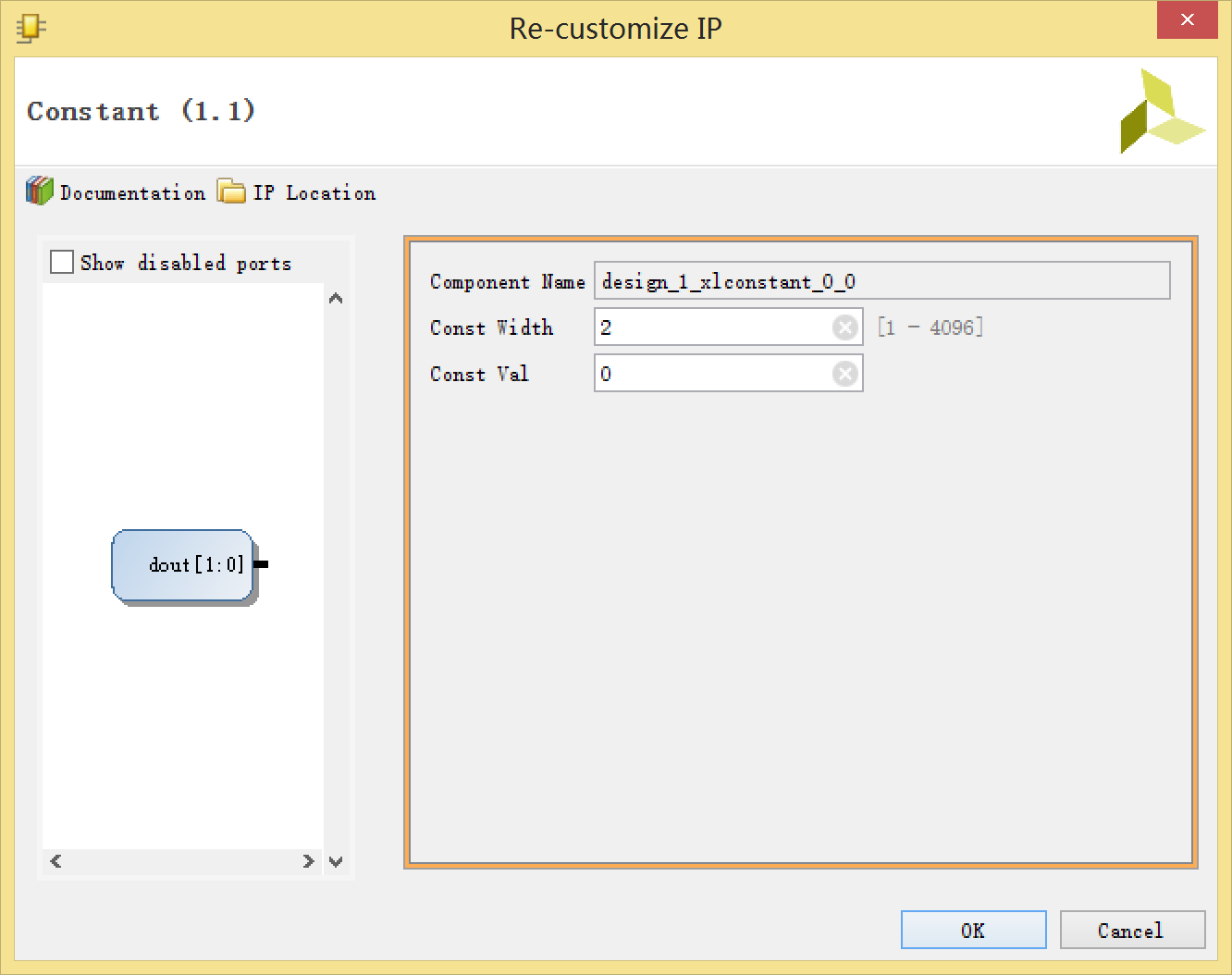

点击Add IP,添加Constant IP,配置如下

新建一个约束文件,把以下引脚约束添加进来

# Miz702 or zedboard Audio Codec Constraints

set_property PACKAGE_PIN AA6 [get_ports BCLK]

set_property IOSTANDARD LVCMOS33 [get_ports BCLK]

set_property PACKAGE_PIN Y6 [get_ports LRCLK]

set_property IOSTANDARD LVCMOS33 [get_ports LRCLK]

set_property PACKAGE_PIN AA7 [get_ports SDATA_I]

set_property IOSTANDARD LVCMOS33 [get_ports SDATA_I]

set_property PACKAGE_PIN Y8 [get_ports SDATA_O]

set_property IOSTANDARD LVCMOS33 [get_ports SDATA_O]

#MCLK

set_property PACKAGE_PIN AB2 [get_ports FCLK_CLK1]

set_property IOSTANDARD LVCMOS33 [get_ports FCLK_CLK1]

set_property PACKAGE_PIN AB4 [get_ports iic_1_scl_io]

set_property IOSTANDARD LVCMOS33 [get_ports iic_1_scl_io]

set_property PACKAGE_PIN AB5 [get_ports iic_1_sda_io]

set_property IOSTANDARD LVCMOS33 [get_ports iic_1_sda_io]

set_property PACKAGE_PIN AB1 [get_ports {ADDRESS[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ADDRESS[0]}]

set_property PACKAGE_PIN Y5 [get_ports {ADDRESS[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ADDRESS[1]}]配置好之后和ADDRESS连接在一起,

然后就可以Create HDL wapper,点击Generate bitstream

建立软件工程

打开SDK之后,新建一个空的工程

新建头文件文件,

audio.h

#ifndef __AUDIO_H_

#define __AUDIO_H_

#include "xparameters.h"

/* Redefine audio controller base address from xparameters.h */

#define AUDIO_BASE XPAR_ZED_AUDIO_CTRL_0_BASEADDR

/* Slave address for the ADAU audio controller 8 */

#define IIC_SLAVE_ADDR 0x70

/* I2C Serial Clock frequency in Hertz */

#define IIC_SCLK_RATE 400000

/* ADAU internal registers */

enum audio_regs {

R0_CLOCK_CONTROL = 0x00,

R1_PLL_CONTROL = 0x02,

R2_DIGITAL_MIC_JACK_DETECTION_CONTROL = 0x08,

R3_RECORD_POWER_MANAGEMENT = 0x09,

R4_RECORD_MIXER_LEFT_CONTROL_0 = 0x0A,

R5_RECORD_MIXER_LEFT_CONTROL_1 = 0x0B,

R6_RECORD_MIXER_RIGHT_CONTROL_0 = 0x0C,

R7_RECORD_MIXER_RIGHT_CONTROL_1 = 0x0D,

R8_LEFT_DIFFERENTIAL_INPUT_VOLUME_CONTROL = 0x0E,

R9_RIGHT_DIFFERENTIAL_INPUT_VOLUME_CONTROL = 0x0F,

R10_RECORD_MICROPHONE_BIAS_CONTROL = 0x10,

R11_ALC_CONTROL_0 =

该篇博客介绍了如何在Zynq开发平台Miz702(兼容Zedboard)上利用ADAU1761音频编解码芯片进行音频信号处理,包括2路模拟信号的数字化和模拟信号输出。通过左右声道相减实现人声消除功能。文中提到不涉及ADAU1761驱动编写,直接使用Ali Aljaani的IP Core,并详细说明了Vivado工程和软件工程的建立步骤,以及硬件约束和软件接口的配置过程。

该篇博客介绍了如何在Zynq开发平台Miz702(兼容Zedboard)上利用ADAU1761音频编解码芯片进行音频信号处理,包括2路模拟信号的数字化和模拟信号输出。通过左右声道相减实现人声消除功能。文中提到不涉及ADAU1761驱动编写,直接使用Ali Aljaani的IP Core,并详细说明了Vivado工程和软件工程的建立步骤,以及硬件约束和软件接口的配置过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3869

3869

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?