技术交流是便宜的博客地址:http://blog.csdn.net/techexchangeischeap

概述

能将处理器的GPIO(General Purpose Input and Output)内部结构和各种模式彻底弄清楚的人并不多,最近在百度上搜索了大量关于这部分的资料,对于其中很多问题的说法并不统一。本文尽可能的将IO涉及到的所有问题罗列出来,对于有明确答案的问题解释清楚,对于还存在疑问的地方也将问题提出,供大家讨论。

概括地说,IO的功能模式大致可以分为输入、输出以及输入输出双向三大类。其中作为基本输入IO,相对比较简单,主要涉及的知识点就是高阻态;作为输出IO,相比于输入复杂一些,工作模式主要有开漏(Open Drain)模式和推挽(Push-Pull)模式,这一部分涉及的知识点比较多;对于输入输出IO,容易产生疑惑的地方是准双向和双向端口的区别。

下面就按照这样的顺序依次介绍各个模式的详细情况。

输入IO

这里所说的输入IO,指的是只作为输入,不具有输出功能。此时对于input引脚的要求就是高阻(高阻与三态是同一个概念)。基本输入电路的类型大致可以分为3类:基本输入IO电路、施密特触发输入电路以及弱上拉输入电路。

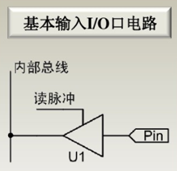

先从最基本的基本输入IO电路说起,其电路如图 1所示。

图 1

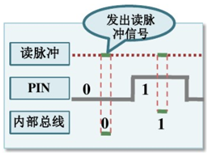

其中的缓冲器U1是具有控制输入端,且具有高阻抗特性的三态缓冲器。通俗地说就是这个缓冲器对外来说是高阻的,相当于在控制输入端不使能的情况下,物理引脚与内部总线之间是完全隔离的,完全不会影响内部电路。而控制输入端的作用就是可以发出读Pin状态的操作指令。其过程如图 2所示。

图 2

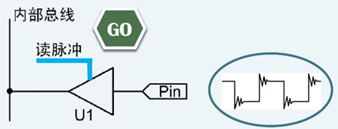

这种基本电路的一个缺点是在读取外部信号的跳变沿时会出现抖动,如下图所示。

图 3

于是施密特触发输入电路就是解决了上述这种抖动的问题,其经过施密特触发器后的信号如图 4所示。

图 4

对于输入电路还存在另外一个问题,就是当输入引脚悬空的时候,输入端检测到的电平是高还是低?当输入信号没有被驱动,即悬空(Floating)时,输入引脚上任何的噪声都会改变输入端检测到的电平,如图 5所示。

图 5

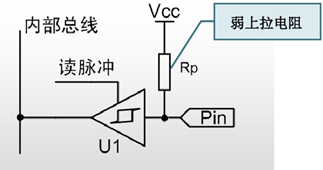

为了解决这个问题,可以在输入引脚处加一个弱上拉电阻,如图 6所示。

图 6

这样,当输入引脚悬空时,会被RP上拉到高电平,在内部总线上就有确定的状态了。

但是这种结构是有一定问题的。首先很明显的一点是,当输入引脚悬空时读到的是1,当输入引脚被高电平驱动时读到的也是1,只有当输入引脚被低电平驱动时读到的才是0。也就是对于读1采取的方式是"读取非零"的方式。

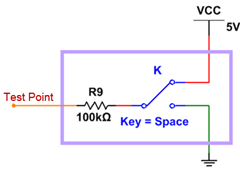

另一个问题是该电路对外呈现的不是高阻,某种意义上说也在向外输出,当外部驱动电路不同时可能出现错误的检测结果。例如外部驱动电路是如图 7所示的结构,该电路结构中通过K打到不同端可以输出高电平或者低电平。

图 7

如果将如图 7所示的电路输出低电平,连接到带有弱上拉电阻的输入引脚,其结构如下所示。

这篇博客详细介绍了GPIO的输入、输出及双向IO的各种模式,包括推挽输出、开漏输出、准双向端口等。作者强调了理解GPIO内部结构和工作模式的重要性,并通过电路图和分析解释了各种模式的特性和应用场景,如推挽输出的全电平驱动能力和开漏输出的线与功能。此外,还特别讨论了51单片机P0端口的复杂双线端口结构及其工作原理。

这篇博客详细介绍了GPIO的输入、输出及双向IO的各种模式,包括推挽输出、开漏输出、准双向端口等。作者强调了理解GPIO内部结构和工作模式的重要性,并通过电路图和分析解释了各种模式的特性和应用场景,如推挽输出的全电平驱动能力和开漏输出的线与功能。此外,还特别讨论了51单片机P0端口的复杂双线端口结构及其工作原理。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6025

6025

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?