技术交流是便宜的博客地址:http://blog.csdn.net/techexchangeischeap

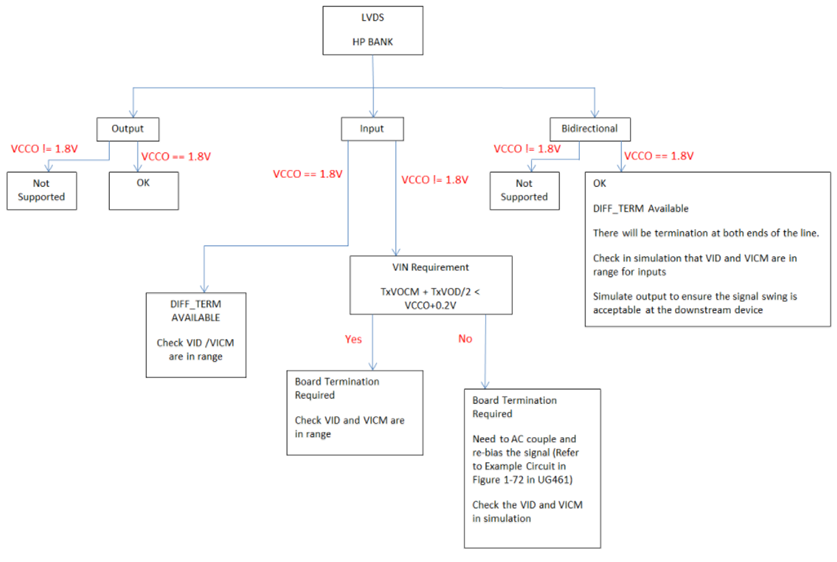

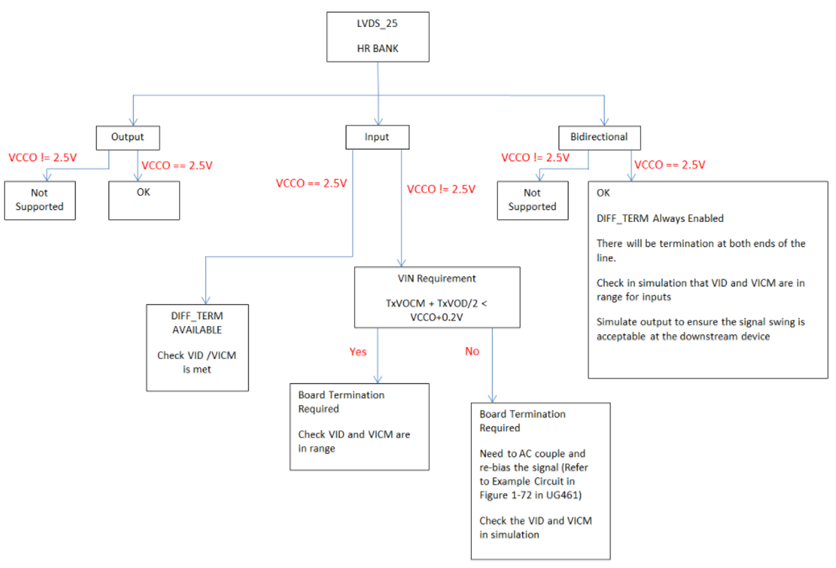

很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电平)连接到了VCCO=2.5V或者3.3V的Bank上,于是产生了关于FPGA引脚与LVDS(以及LVDS-33,LVDS-25)信号相连时兼容性的问题,该专题就解决一下这类问题。总的来说,只要按照下面图 1和图 2流程进行判断即可。

这里补充一点知识,Xilinx的FPGA从7系开始分HR IO Bank和HP IO Bank,其中HR(High Range)Bank支持1.2V,1.5V,1.8V,2.5V以及3.3V供电;而HP(High Performance)Bank只支持1.2V,1.5V,1.8V供电,不再支持2.5V和3.3V供电。

图 1

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2311

2311

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?