摘要: Intel通过在处理器上把管脚数从32增加到36,以提高处理器的寻址能力,使其达到2^36=64GB,然而线性地址的位数仍然是32位,为此,需引入一种新的分页机制。从pentium pro处理器开始,intel引入一种PAE机制,另外一种叫做页大小扩展机制(PSE)在pentium III中引入,但是linux没有采用,本文不讨论它。

本文来源:内存管理:物理地址扩展(PAE)分页机制http://blog.csdn.net/trochiluses/article/details/12853027

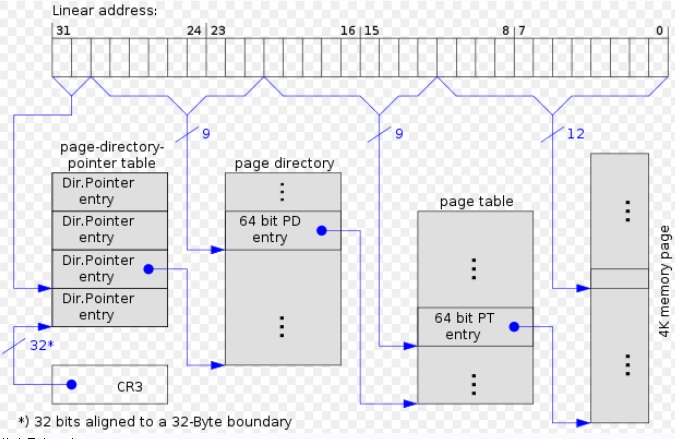

64GB的RAM被分为2^24个页框,页表项的物理地址字段从20位扩展到24位,每个页表项必须包含12个标志位(固定)和24个物理

地址位(36-12),共36位,因此,每个页表项须从32位扩展到64位(36位>32位,考虑到对齐,因此应将页表项扩大一倍到64位)。

在4KB的常规分页情况下,由于每个页表项大小为64为,因而,原有4K大小的页表中,仅能包含512个表项,这占用了32

位线性地址中的9位,同理,由于页目录项与页表项具有同样的结构,高一级的页目录表中也仅能包含512个页表项,同样占用

了32位线性地址中的9位,此时,线性地址剩余位数为:32位(总位数)-12位(页内偏移量)-9位(指示页表中的索引)-9位

(指示页目录表中的索引)=2位,同时,Linux引入了一个页目录指针表(PDPT)的页表新级别,由4个64位表项构成,剩余

的2位即用来指向PDPT中4个项中的一个。

下面4张图详细说明了4种情况下的页表结构(引自Wikipedia)

未启用PAE下的4K分页的页表结构

未启用PAE下的4M分页的页表结构

启用PAE下4K分页的页表结构

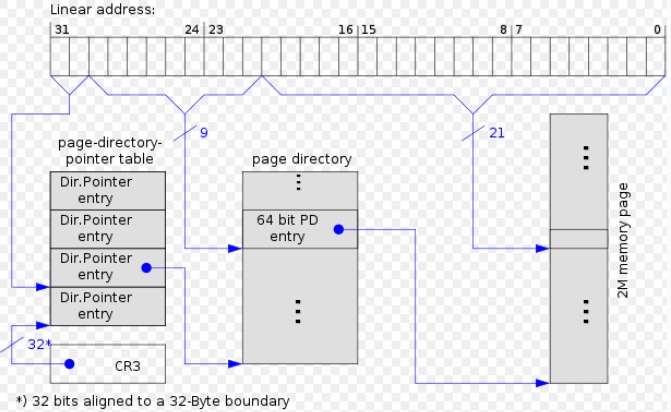

启用PAE下2M分页的页表结构

线性地址的映射过程如下:

1)cr3:指向一个PDPT基地址

2)地址的31~30:确定PDPT项

3)地址的29~21:确定页目录项中的一个

此处,发生了分支:

A。如果页目录项的PS标志位等于0,那么页大小是4K

4)地址的20~12:确定页表的某一项

5)地址的11~0:确定偏移

B. 如果PS=1,启用大页

4)地址的20~0:确定2M页中的偏移量。

4730

4730

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?