spi与iic的对比,为啥使用spi而不用iic。

spi是一主多从模式,iic为各个设备之间地位相等可以主从切换。

1.spi的通讯速率没有限制,而iic最大为3.4mhz,但普遍使用的还是0到400khz,所以spi比iic的通讯速率更快。

2.iic的scl与sda都要配置成开漏输出模式,而spi没有限制

3.spi没有应答位等。

4.spi的抗干扰比iic强。

5.iic是半双工,因为sda相当于spi中的mosi,miso,ss,三根线。spi为全双工。

6.iic速率受限制的原因,iic为弱上拉(回弹慢,影响数据传输速率),强下拉下拉快。

7.spi为推挽输出,浮空或上拉输入,数据传输的速率快效率高。

spi通信介绍(其中m为master主机,s为slave从机,o为output,i为input,)

1.spi有四根通讯线sck(serial clock时钟线),mosi(master output slave input主机输出从机输入),miso(master input slave output主机输入从机输出),ss(slave select从机选择)。

2.支持一主多从模式。

3.同步全双工。(挂载的两个设备可以进行同时的信息传递与接受)同步全双工需要更多的带宽和硬件资源。(因此设备之间的距离较远或存在干扰,可能会影响同步全双工的性能)

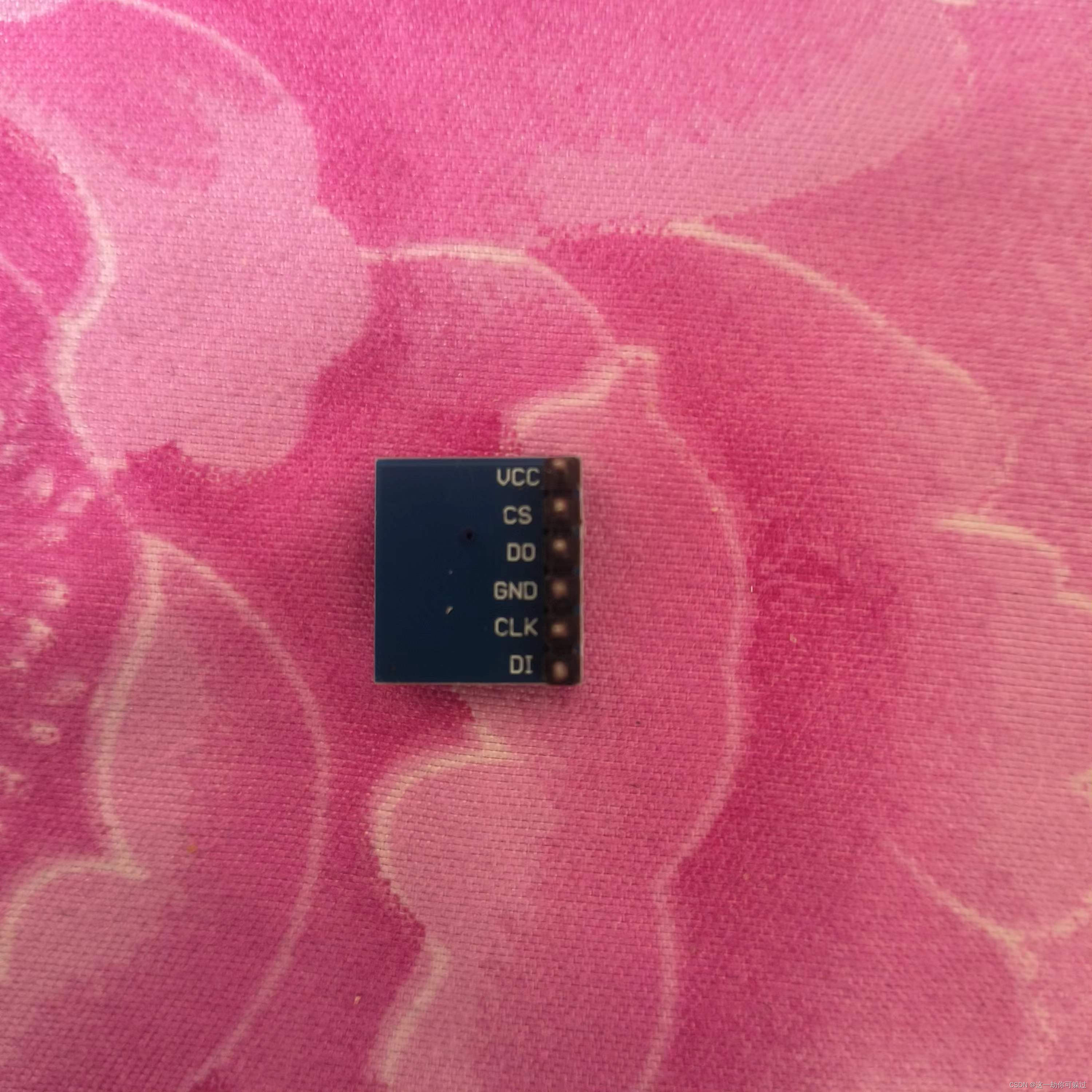

关于一些进行spi通讯的模块介绍

上图是 w25q64是一个flash存储器

图中引脚介绍

vcc电源(3.3v),

cs连接spi通讯线上的ss(slave select从机选择),低电平选中进行通信(低电平允许从设备开始通信),未被选中时miso,mosi两个引脚为高阻态断开。

DO为输出,连接到设备上的miso(主机输入从机输出),

DI为输入,连接到设备上的mosi(主机输出从机输入)

clk为serial clock时钟线,

gnd接地。

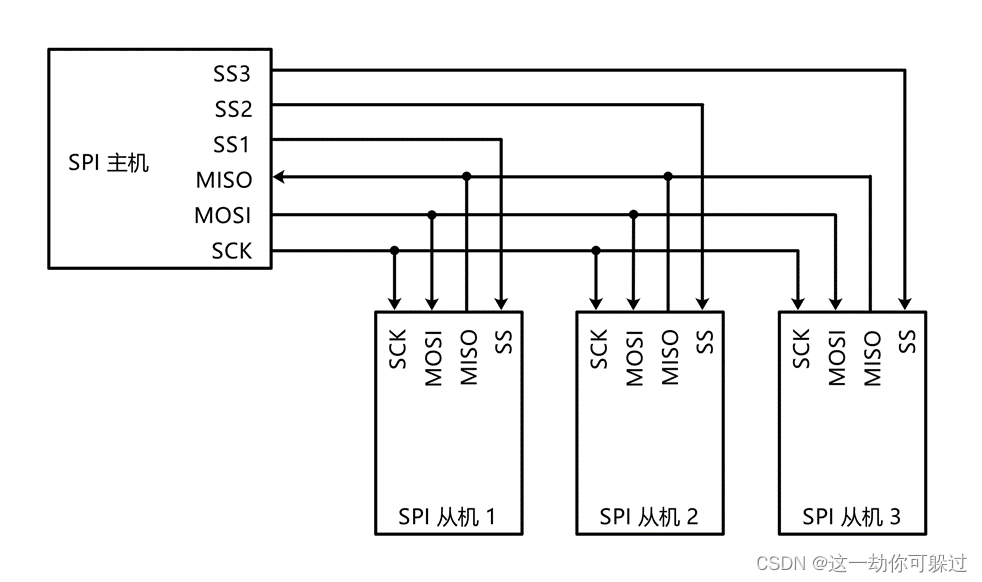

spi硬件电路

1.所有spi设备的sck,mosi,miso分别连接到一起

2.主机另外引出多条ss控制线,分别接到各个从机的ss引脚上。可使用138译码器加573实现三个ss控制多个从设备。

3.输出引脚为推挽输出,输出引脚配置为浮空或者上拉输入。

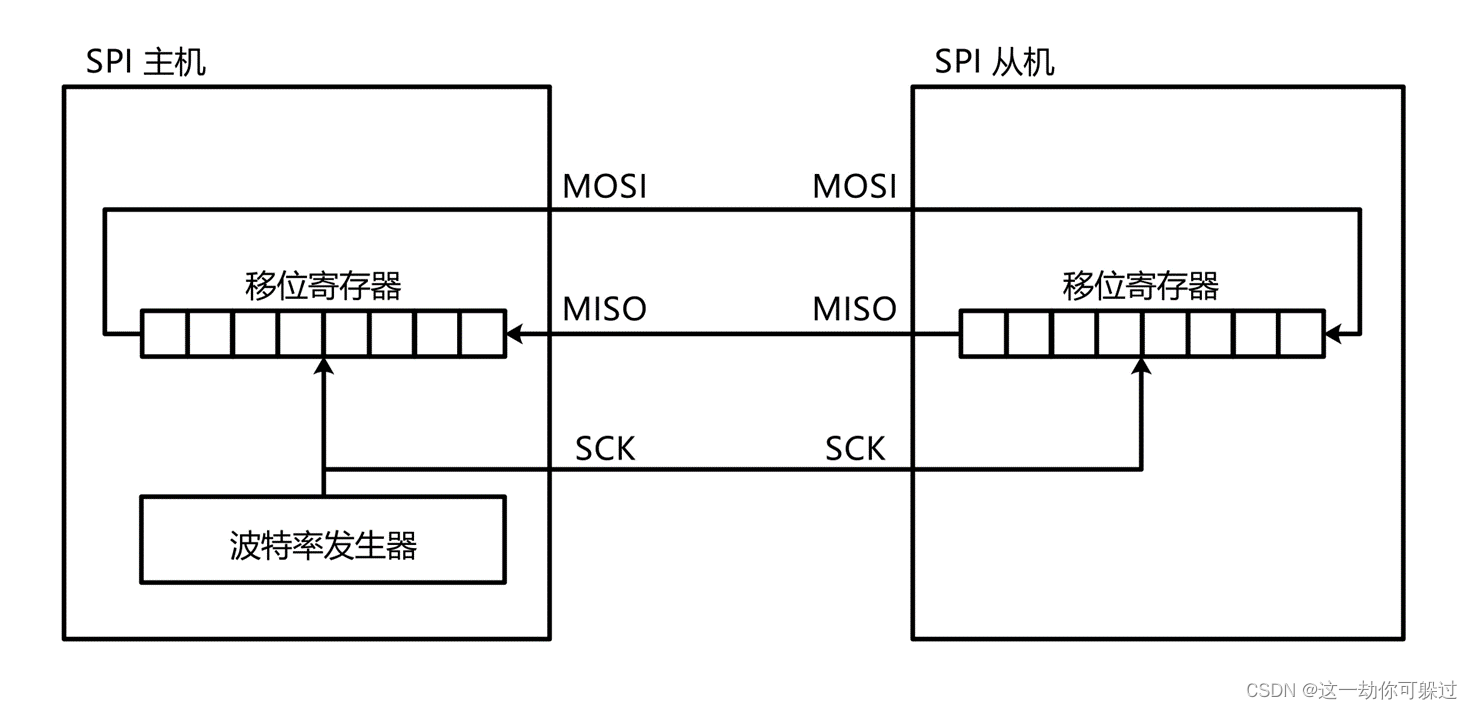

通讯原理图

假如主机中一个八位数据1100 1010要发送到从机,从机一个数据1011 0011要发送到主机,

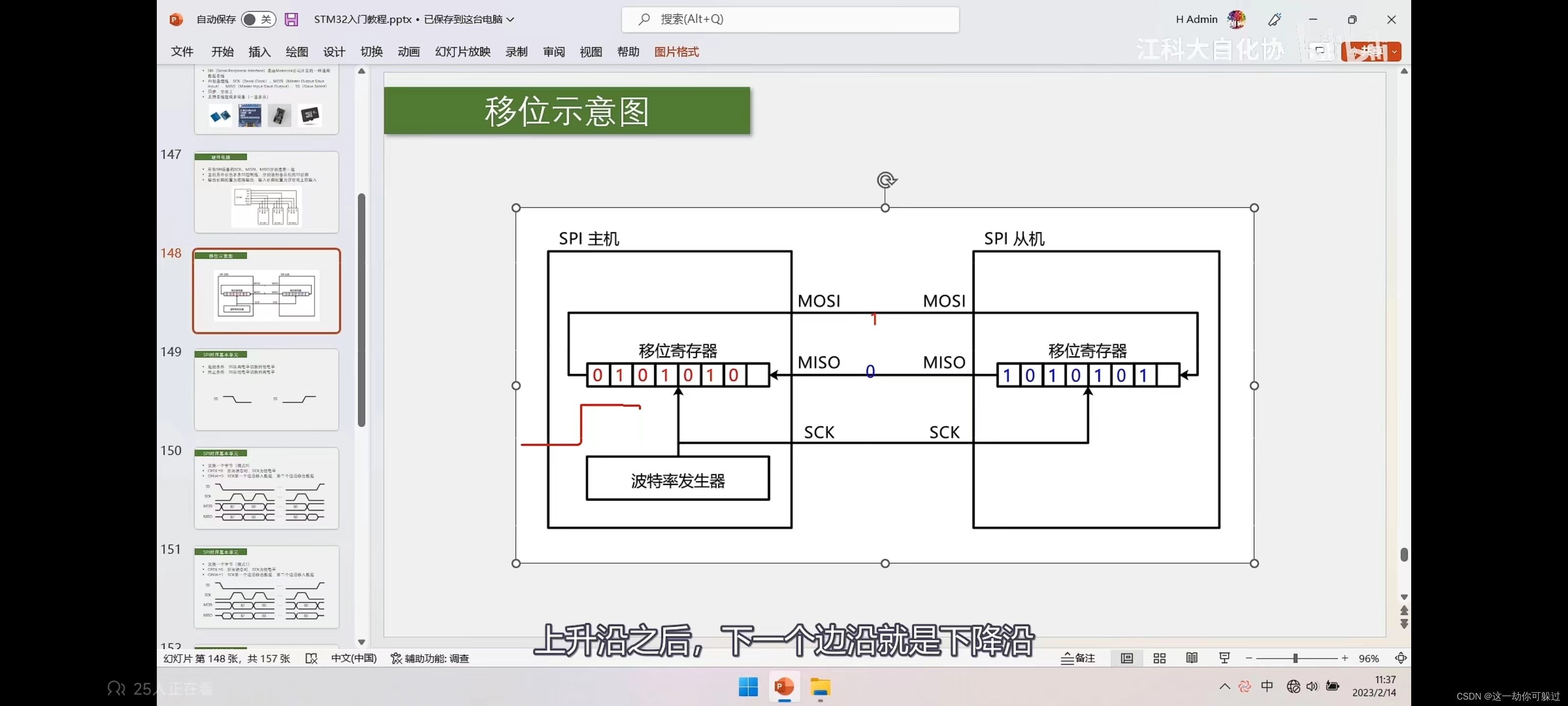

波特率发生器讲解(起到一个同时控制主从设备进行移位采集操作的作用):给一个脉冲(上升沿),将主机移位寄存器中的最高位(最左位)移出寄存器将数据放到MOSI上,同时将从机的最高位(左位数据)放到MISO上。再给一个下降沿脉冲,主机将MISO上的数据采集到自己末尾(最右位),从机将MOSI上的数据采集到从机的移位寄存器的末尾最右位。完成一个位的传输。

开始进行通讯(下图为原理):

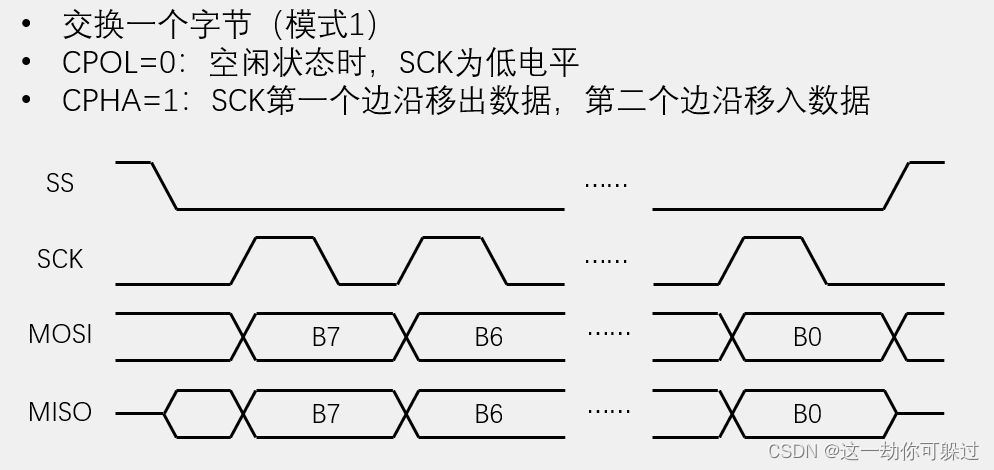

spi通信的时序

1.起始条件:ss从高电平切换到低电平(下降沿)

2.终止条件:ss从低电平切换到高电平(上升沿)

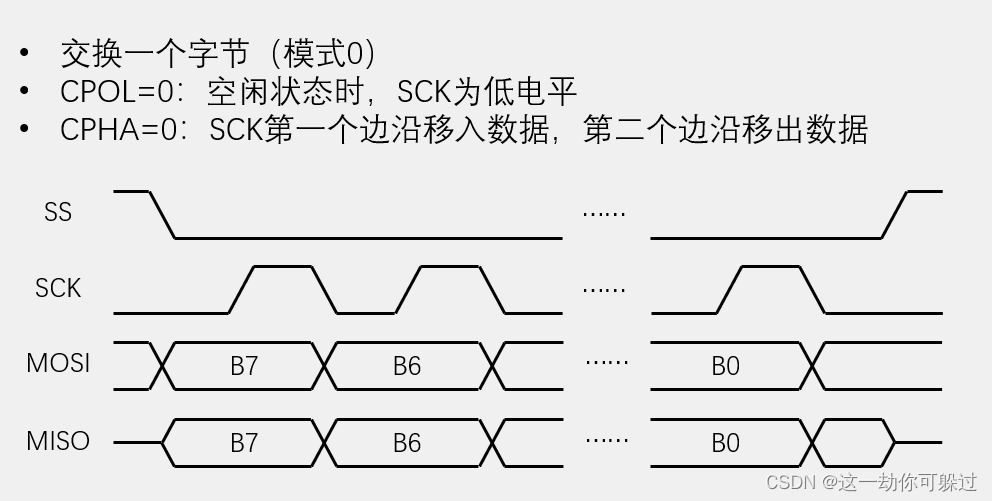

3. 交换一个字节

模式一(上升沿移出,下降沿采集)

1.多个输出连接在一起,如果同时开启输出,会造成冲突当从设备的ss未被选中时MISO为高阻态

2.在SS为上升沿时(终止信号),MOSI可以再变化一次,将mosi置到一个默认的电平,此时MISO变为高阻态。

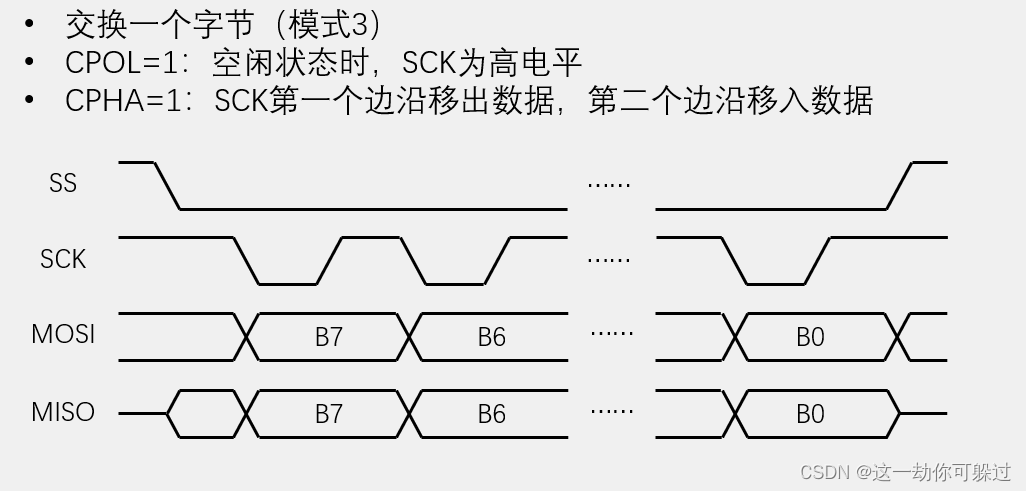

模式三

模式三与模式一再SCK时序上相反,下降沿移出,上升沿采集。

模式零(下降沿移出,上升沿采集)

1.这里是将ss也当做SCK的一个时基单元。ss下降沿后,主机移位寄存器将一个位(最高位)移到MOSI。从机移位寄存器将一个位(最高位)移到MISO上。SCK上升沿后,MOSI上的数据被采集到从机移位寄存器的最后一位。MISO上的数据被采集到主机移位寄存器的最后一位。完成一位数据的交换。

2.ss上升延后终止通讯。

3.在第八个上升沿时,数据被采集完成(一个字节数据交换完成)。在第八个下降沿时,MOSI置回默认电平或者主机放出下一个字节的第一位。MISO变化一次,变为下一个字节的第一位(因为相位提前了原因,ss的下降沿被作为一个信号采集的相位,所以多一个上升沿移出一位,所以移出下一个字节的第一位)。如果这个移出位不需要,就是只传输一个字节就结束(当SS上升沿时)MISO变化为高组态。

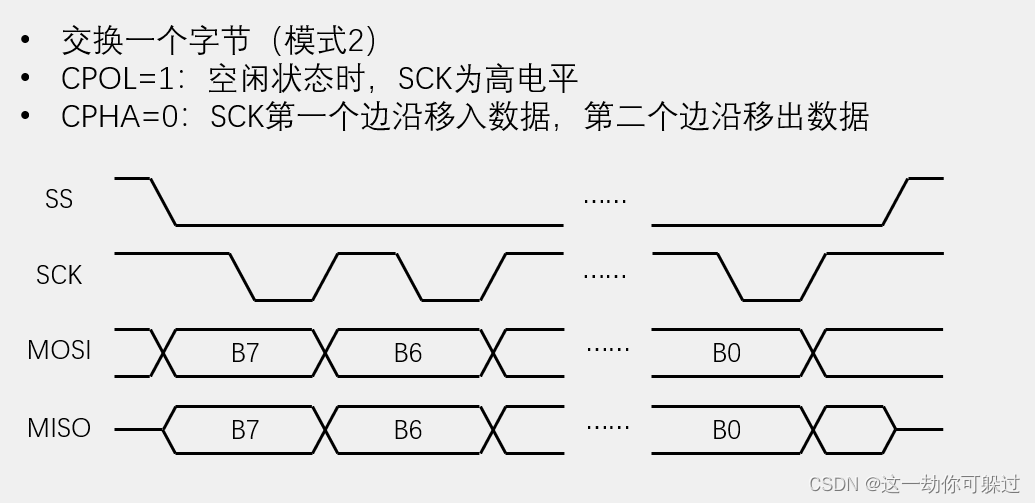

模式二

模式二与模式零在SCK时序上相反,ss起始信号进行移出一位,SCK下降沿采集一位,SCK上升沿移出

本文详细比较了SPI和IIC接口在通信速率、结构特点、抗干扰能力以及同步性方面的差异,重点介绍了SPI的全双工和高速特性,以及SPI在Flash存储器如W25Q64中的应用,包括硬件电路设计和通讯原理示例。

本文详细比较了SPI和IIC接口在通信速率、结构特点、抗干扰能力以及同步性方面的差异,重点介绍了SPI的全双工和高速特性,以及SPI在Flash存储器如W25Q64中的应用,包括硬件电路设计和通讯原理示例。

1778

1778

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?