一、3-8译码器

简介

3-8译码器是一种数字电路,用于将3位输入信号转换为8位输出信号。它通常用于将特定的输入模式映射到对应的输出模式,常见的应用包括控制逻辑电路和显示驱动电路。3-8译码器可以帮助简化复杂的逻辑设计,并且在数字系统中起着重要的作用。

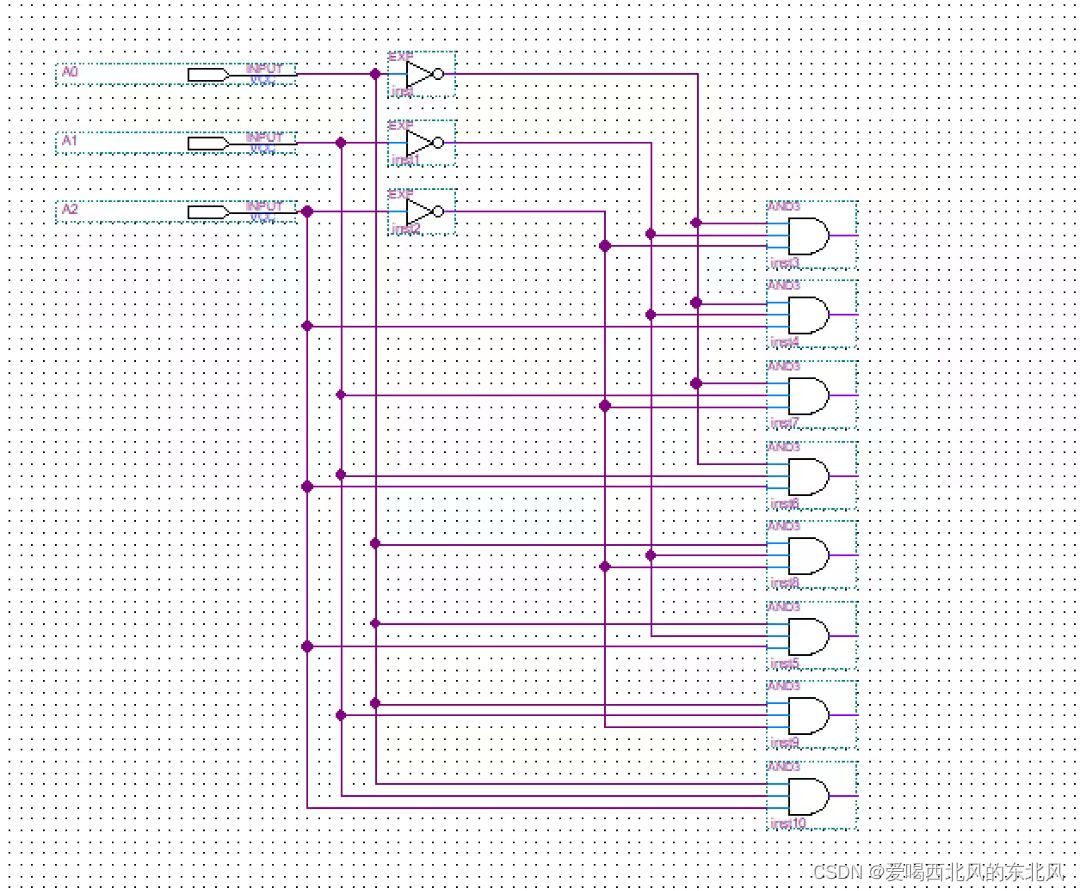

Logisim绘制3-8译码器电路图

逻辑真值表

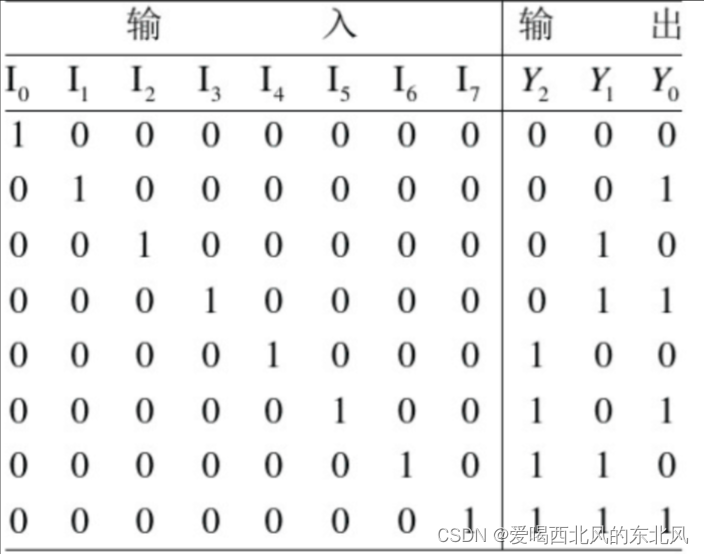

3-8逻辑真值表如下

Verilog编程生成的RTL电路

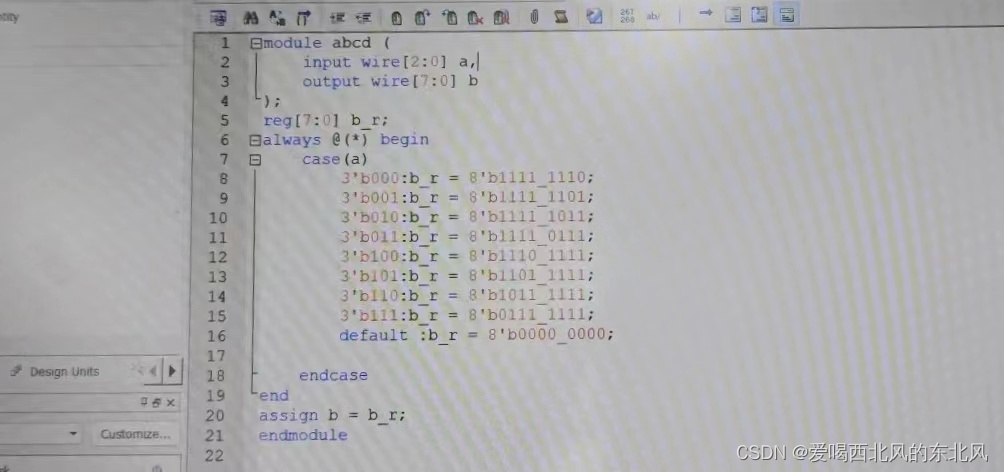

代码如下(always中的case实现)

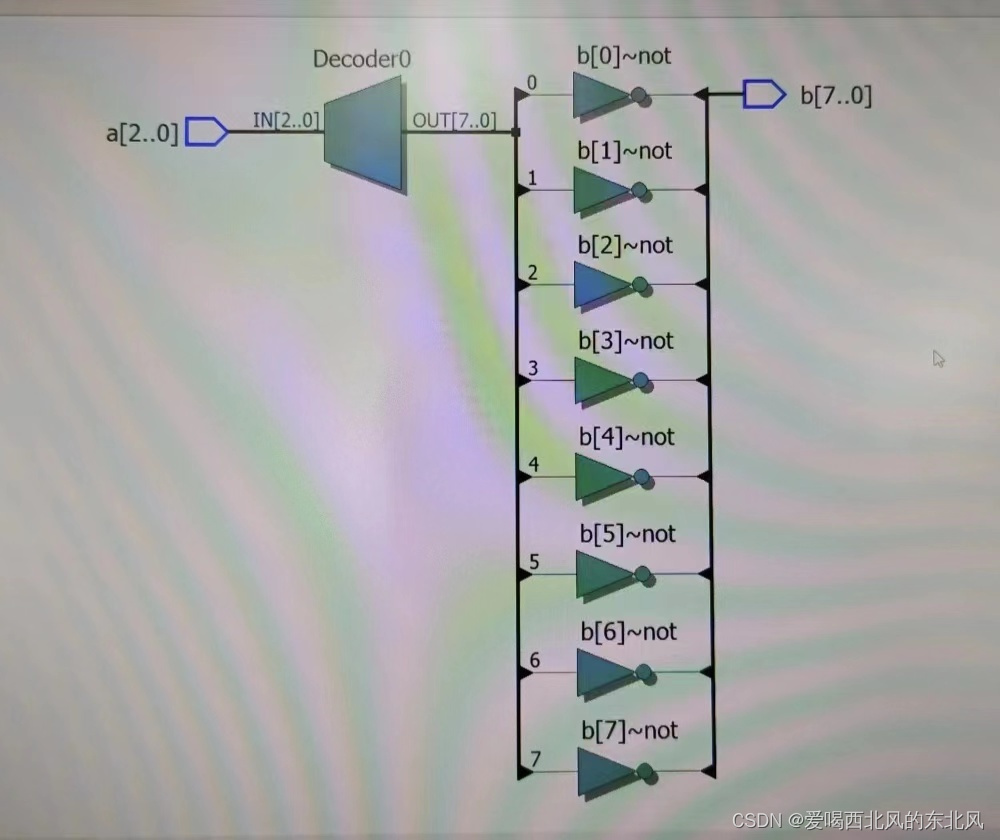

生成的RTL电路如下

问题

Verilog代码设计的3-8译码器模块的输出信号 为何要定义为 reg类型而不用默认wire(导线)类型?改成wire型是否可以? &

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1878

1878

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?