目录

一、 实验目的

掌握组合逻辑电路的分析与设计。掌握真值表、逻辑函数表达式、卡诺图化简基本概念和方法。

二、 实验原理

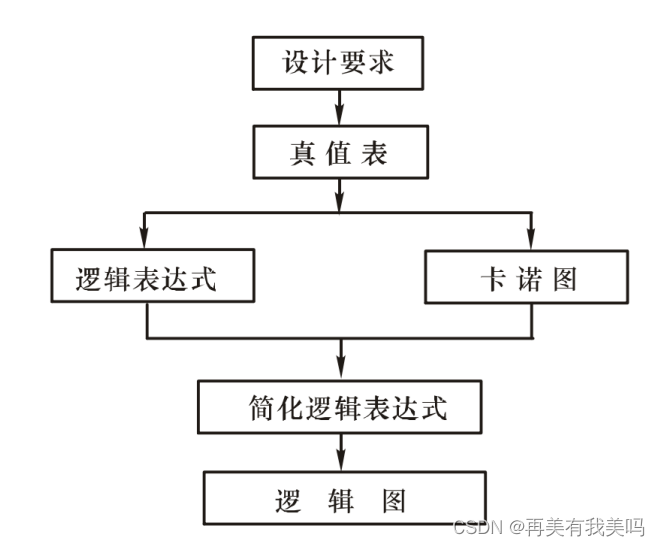

使用中、 小规模集成电路来设计组合电路是最常见的逻辑电路。 设计组合电路的一般步骤如图 3-1 所 示。

图 3-1 组合逻辑电路设计流程图

根据设计任务的要求建立输入、 输出变量, 并列出真值表。 然后用逻辑代数或卡诺图 化简法求出简化的逻辑表达式。 并按实际选用逻辑门的类型修改逻辑表达式。 根据简化后的逻辑表达式, 画出逻辑图, 用标准器件构成逻辑电路。 最后, 用实验来验证设计的正确性。

三、实验内容

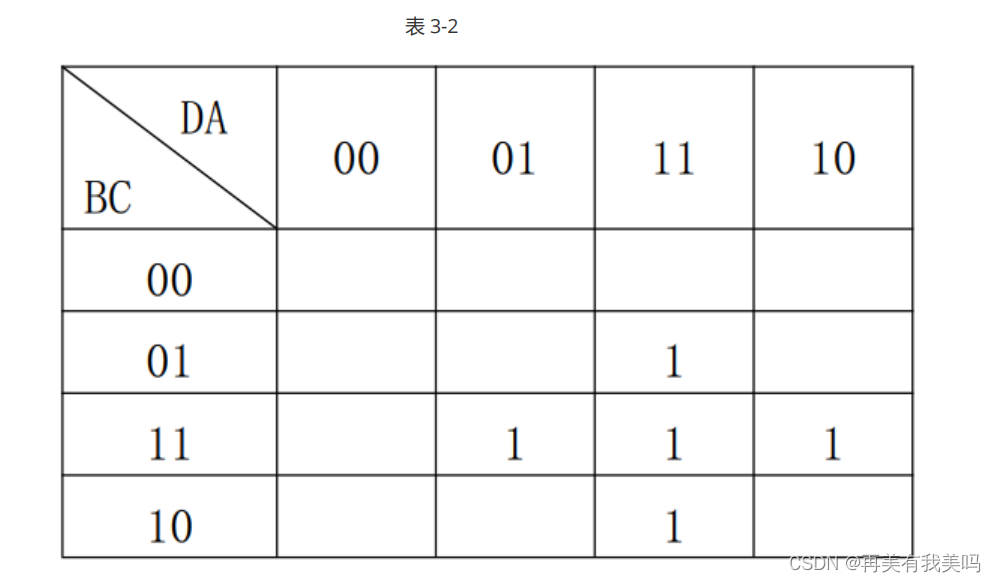

1. 组合逻辑电路--四路表决器 用“ 与非” 门设计一个表决电路: 当四个输入端A、B、C、D中有三个或四个为“ 1” 时, 输出端 才为“ 1”。 设计步骤: 根据题意列出真值表如表3-1 所示, 再填入卡诺图表3-2 中。

表 3-1 真值表(横排改为竖排)

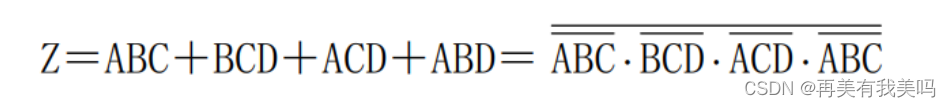

由卡诺图得出逻辑表达式, 并演化成“ 与非” 的形式:

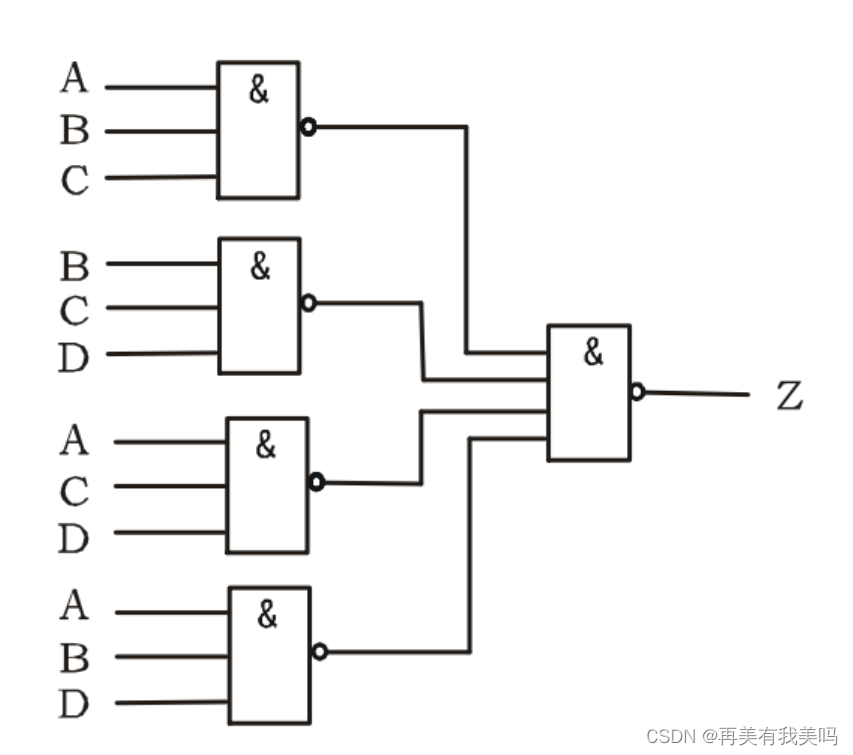

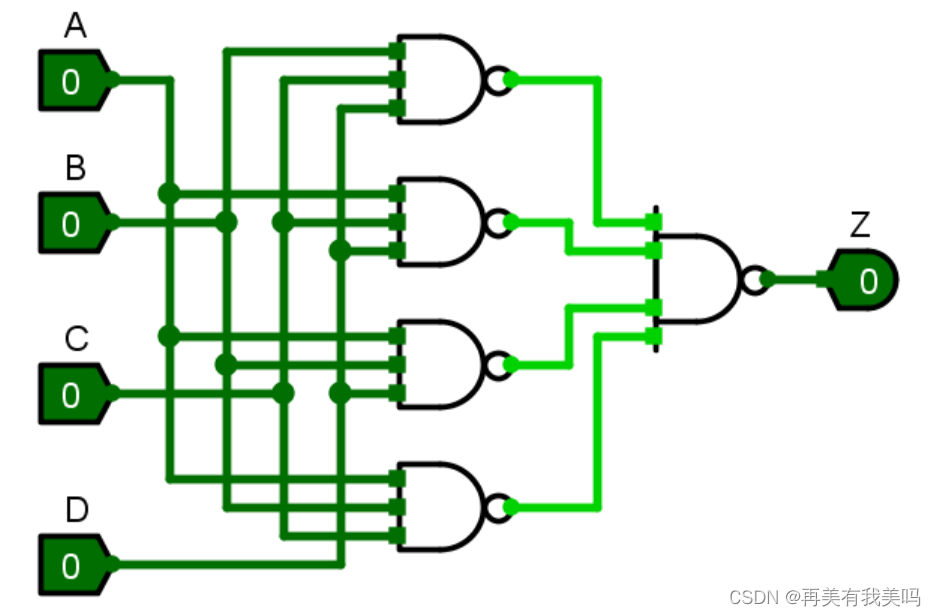

根据逻辑表达式画出用“ 与非门” 构成的逻辑电路如图 3-2 所示。

图 3-2

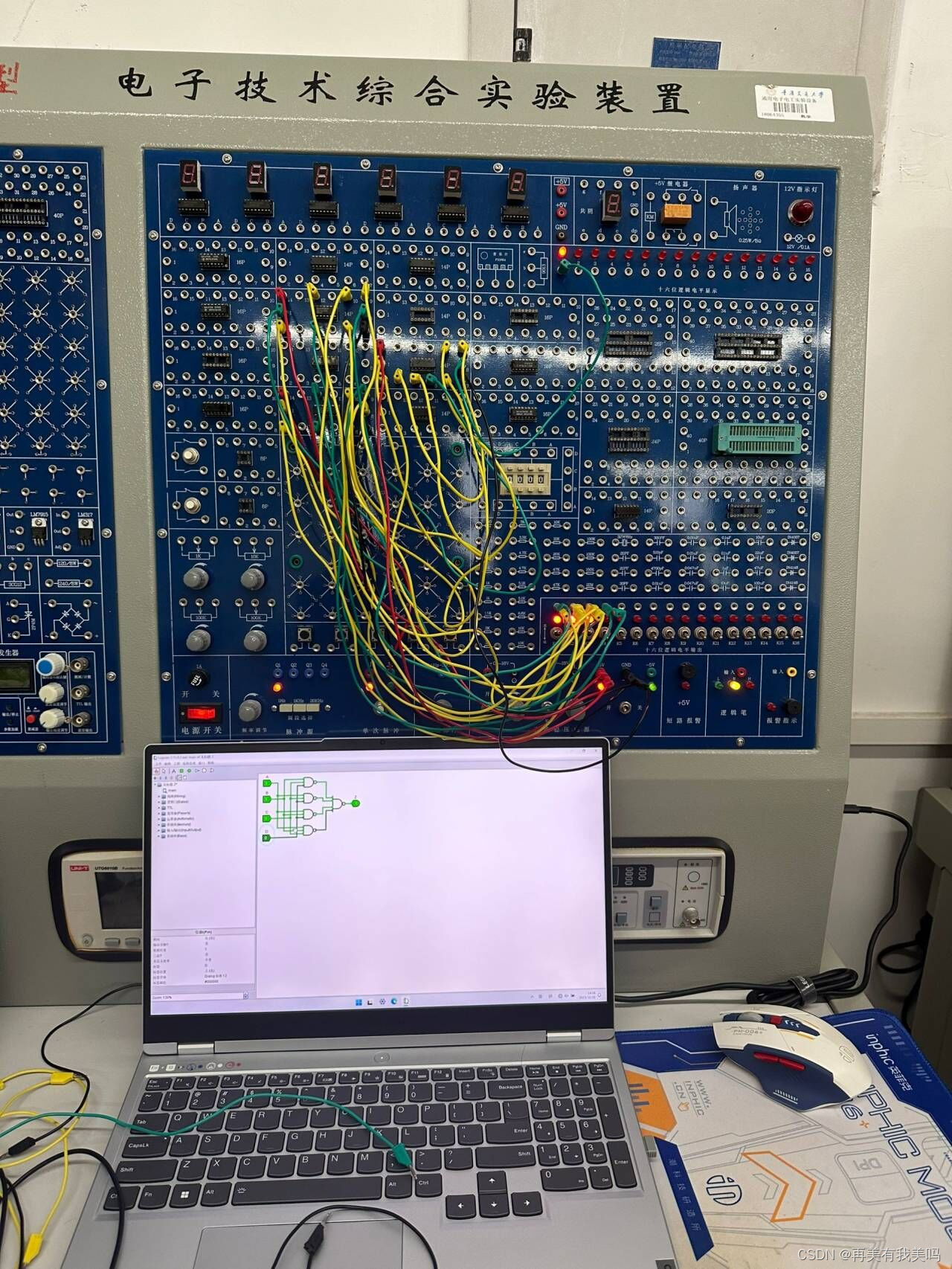

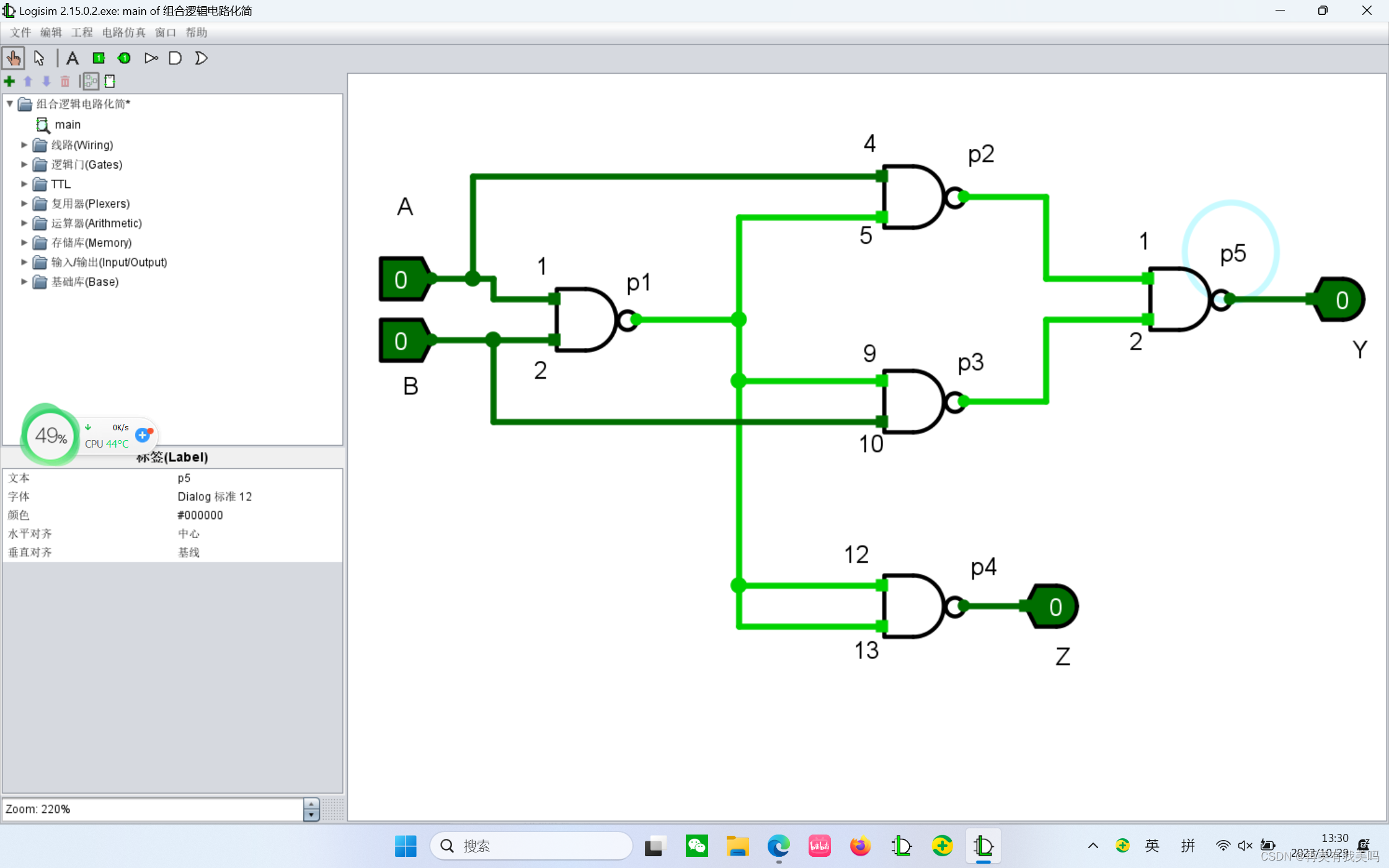

先在Logsim中仿真验证电路的逻辑性。 然后再在实验板上用硬件实现并验证:在实验装置适当位置选定三个14P 插座, 按照集成块定位标记插 好集成块 74LS20。按图3-2接线,输入端 A、 B、 C、 D 接至逻辑开关输出插口, 输出端 Z 接逻辑电平 显示输入插口,按真值表(自拟)要求,逐次改变输入变量, 测量相应的输出值,验证逻辑功能, 与表 3-1 进行比较, 验证所设计的逻辑电路是否符合要求。

(1)Logsim中仿真实验

经反复验证,在logisim上所设计的仿真逻辑电路符合要求,结果如表3-1相同。

(2)具体实现

经验证,与表 3-1 进行比较, 所设计的逻辑电路符合要求。

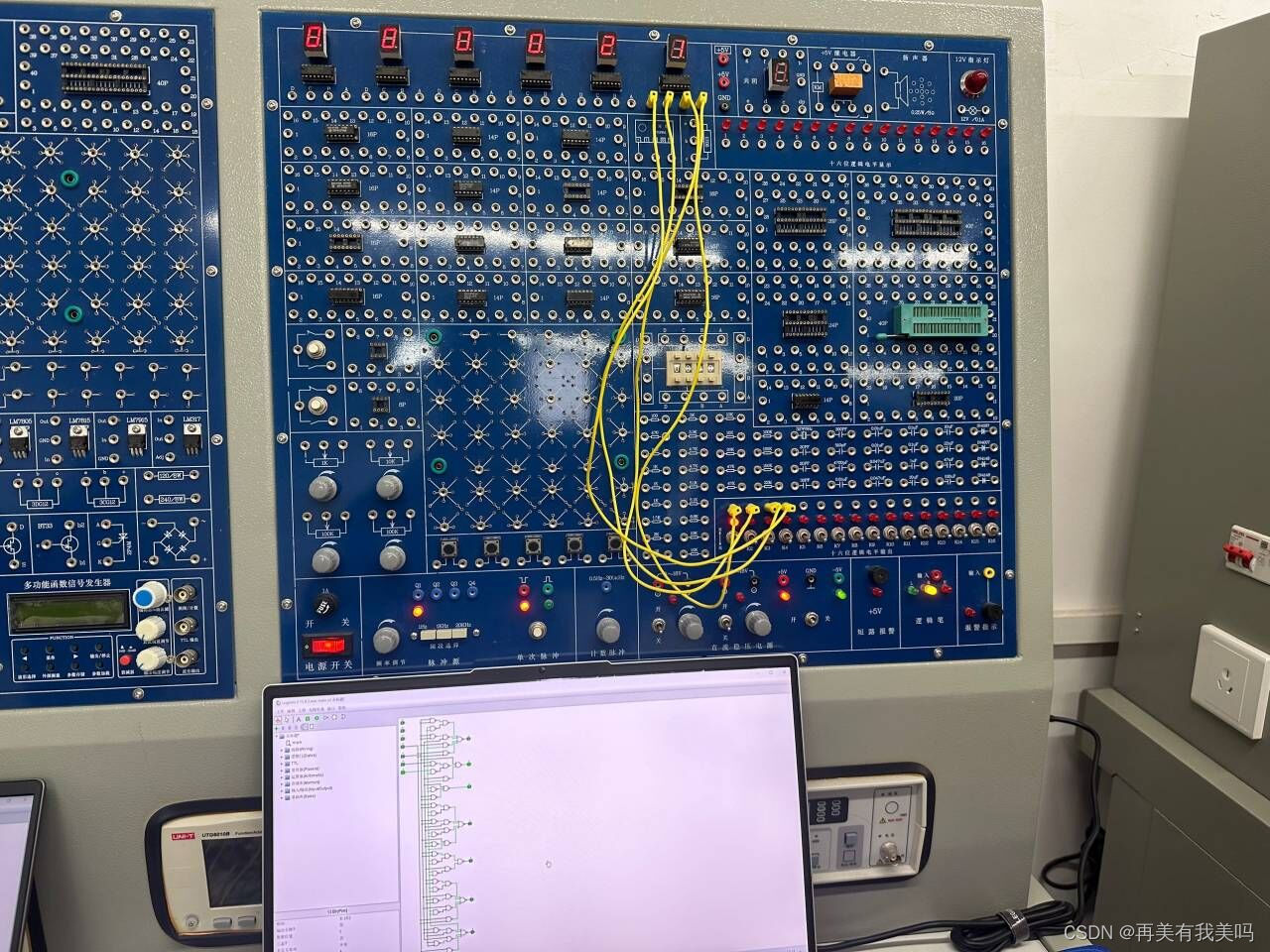

(3)LED显示电路

7段数码显示管(LED)是由7个单独LED二极管组合而成(忽略小数点),经常用来显示0-9 这些 数字。 它可以用 4个输入项A-B-C-D和7个输出项a~g的逻辑关系真值表来表达。

CD4511芯片能够完成这种对应关系的转换。请在之前四路表决器电路实现的基础上,继续用连接 线 联接CD4511,将投票为1的票数总和显示到一个 LED上,思考如何做?

A·logisim仿真实验

B·具体实验

经检验,所设计的逻辑电路符合要求。

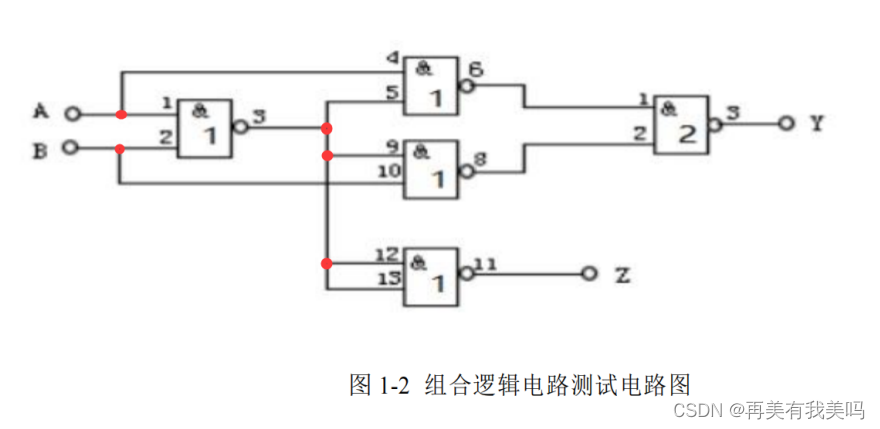

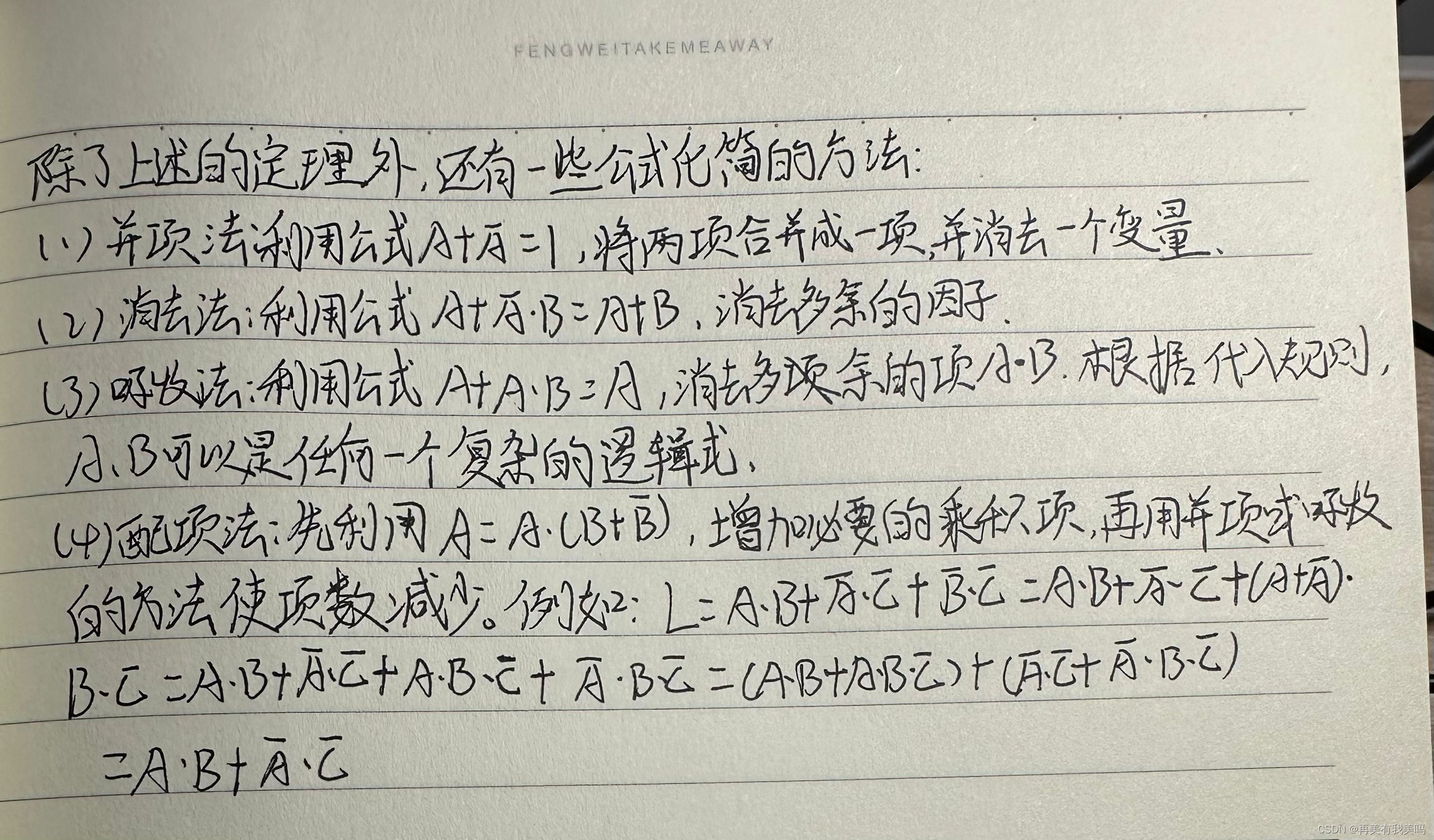

四、组合逻辑电路化简

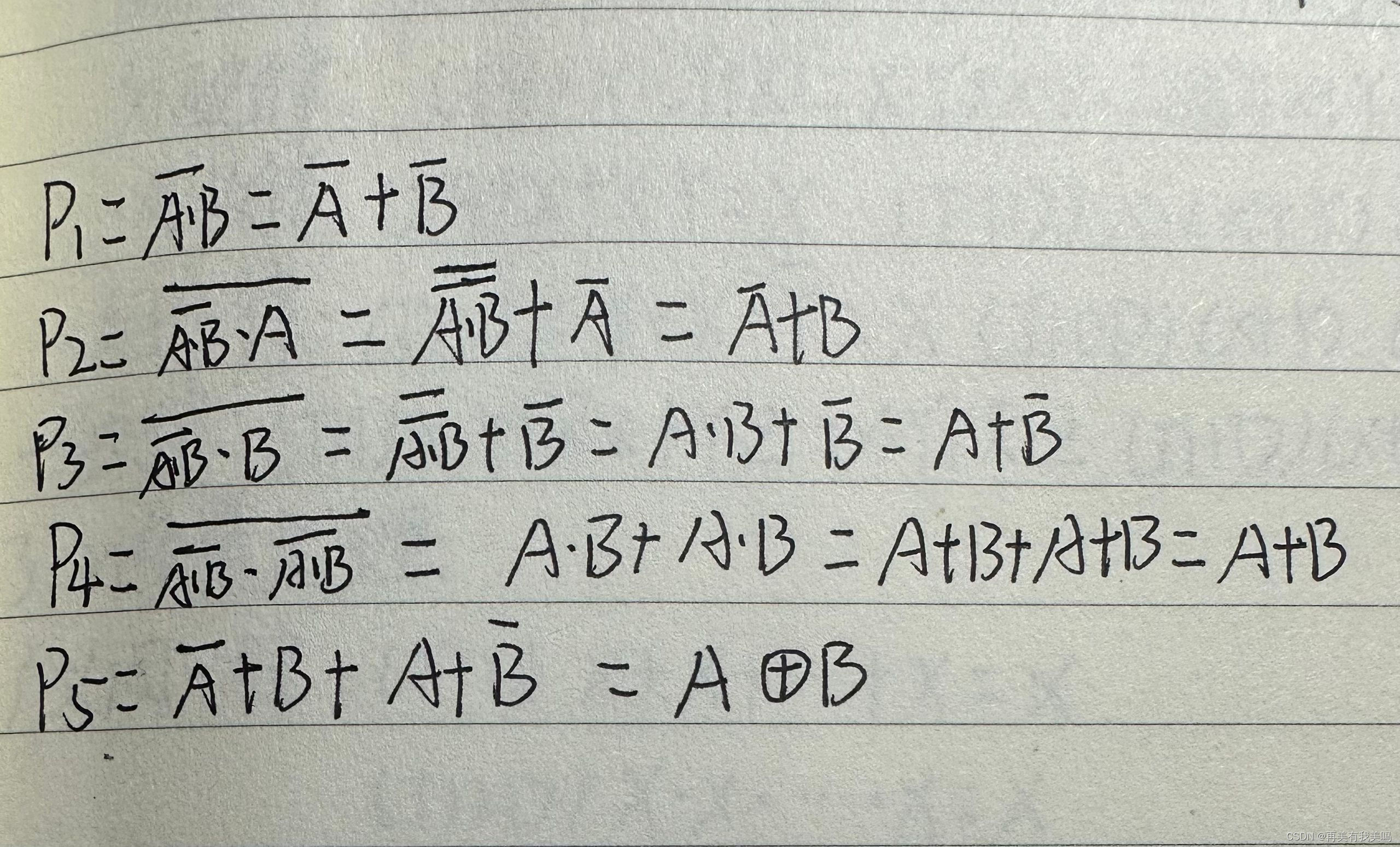

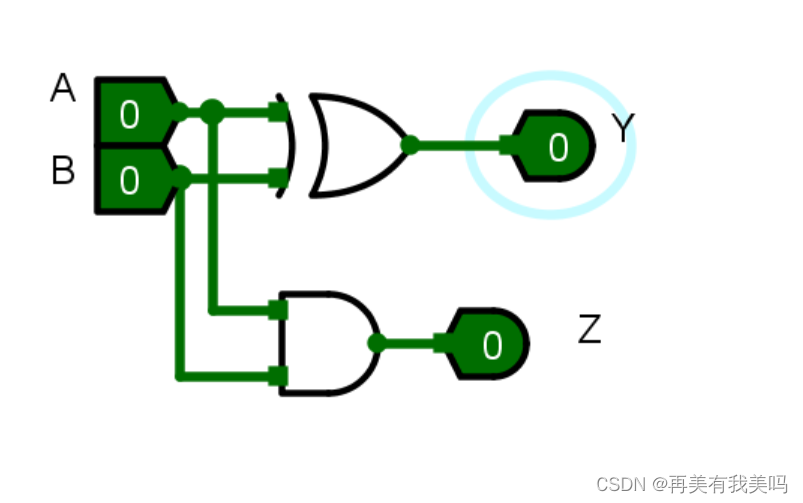

在实验二中有一个组合逻辑电路,入下图所示。请根据电路中写出 Y和Z的逻辑表达式,并进行化简。 重新验证之前的答案在理论上是否正确,并重新设计一个新的简化电路。

A.代数法化简

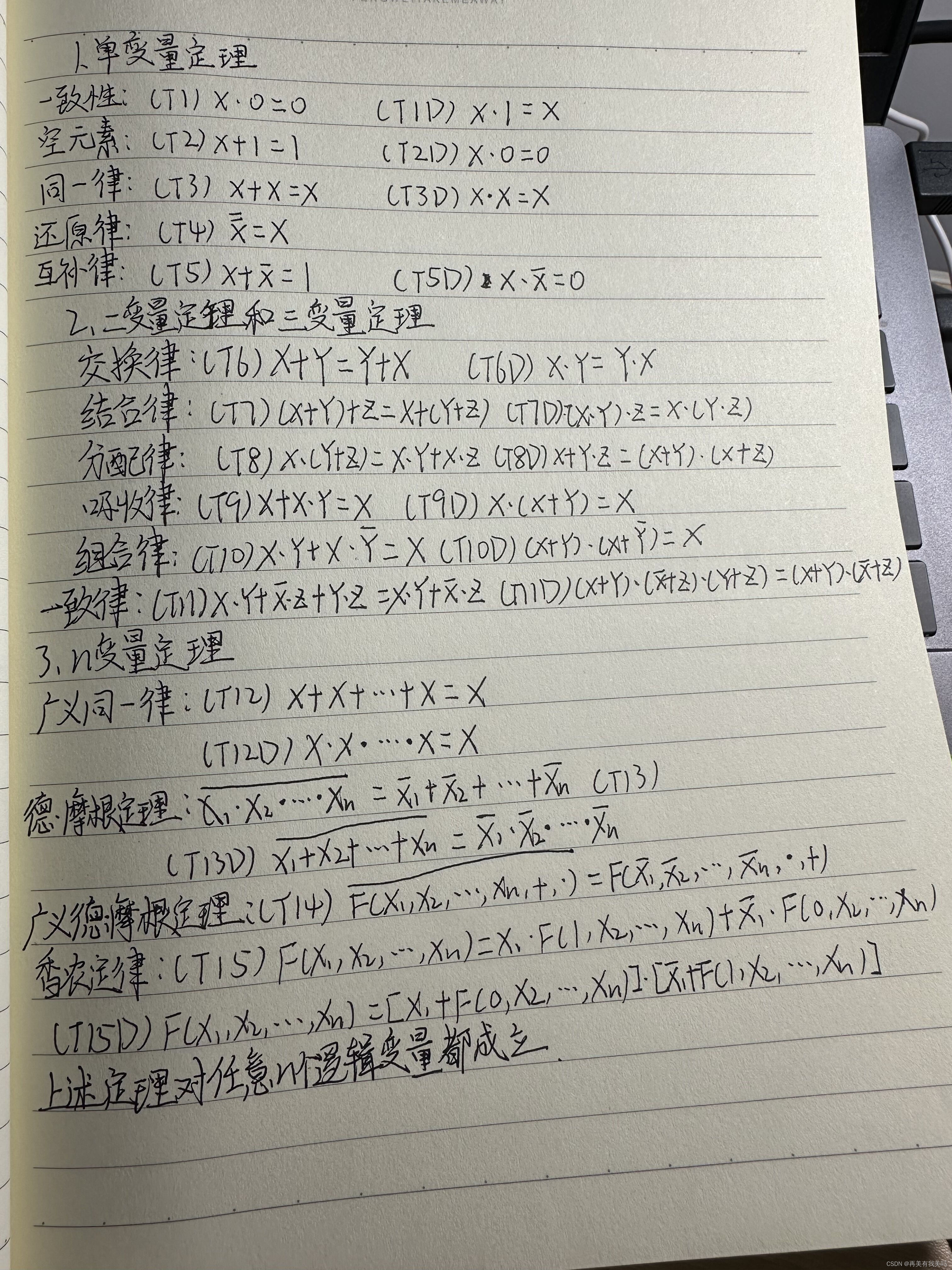

1.公式化简的基本定理

布尔代数定理就是一些通过公理系统推导出来被认为正确的命题,被用来对逻辑表达式

进行简化分析或设计,从而可以采用更高效的数字电路来实现。

2.对组合电路图化简

B.卡诺图法化简

1.卡诺图基本定义

卡诺图是逻辑函数的一种图形表示。一个逻辑函数的卡诺图就是将此函数的最小项表达式中的各最小项相应地填入一个方格图内,此方格图称为卡诺图。

卡诺图的构造特点使卡诺图具有一个重要性质:可以从图形上直观地找出相邻最小项。两个相邻最小项可以合并为一个与项并消去一个变量。

卡诺图的构造特点使卡诺图具有一个重要性质:可以从图形上直观地找出相邻最小项合并。合并的理论依据是并项定理AB+AB反=A。例如,

根据定理AB+AB反=A和相邻最小项的定义,两个相邻最小项可以合并为一个与项并消去一个互反变量。例如,4变量最小项ABCD和ABC反D相邻,可以合并为ABD;A反BCD和A反BC反D相邻,可以合并为A反BD;而与项A反BD和ABD又为相邻与项,故按同样道理可进一步将两个相邻与项合并为BD。

用卡诺图化简逻辑函数的基本原理就是把上述逻辑依据和图形特征结合起来,通过把卡诺图上表征相邻最小项的相邻小方格“圈”在一起进行合并,达到用一个简单“与”项代替若干最小项的目的。

通常把用来包围那些能由一个简单“与”项代替的若干最小项的“圈”称为卡诺圈。

2.对组合电路化简

C.使用两种方法化简的结果

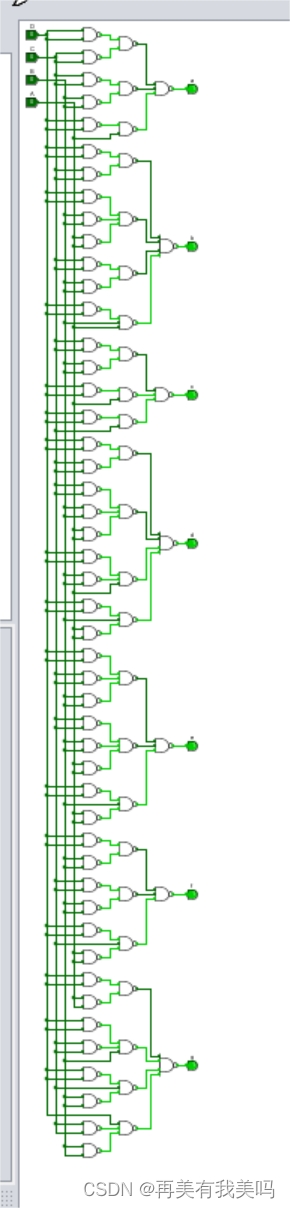

通过使用logisim软件进行仿真实验:

通过代数法及卡诺图法验证之前的答案在理论上正确,并重新设计一个新的简化电路:

五、组合逻辑电路--1位全加器

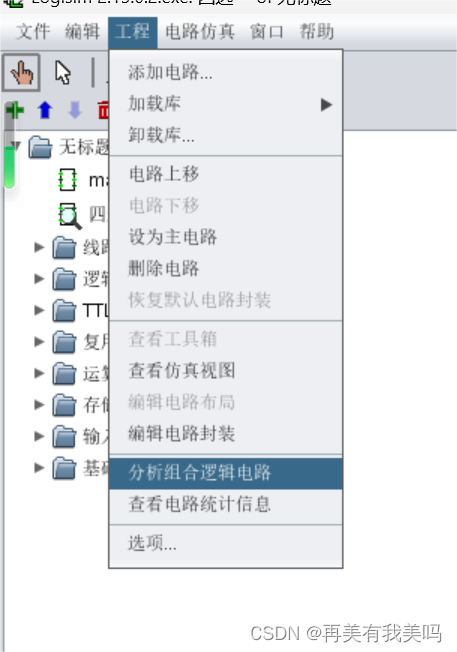

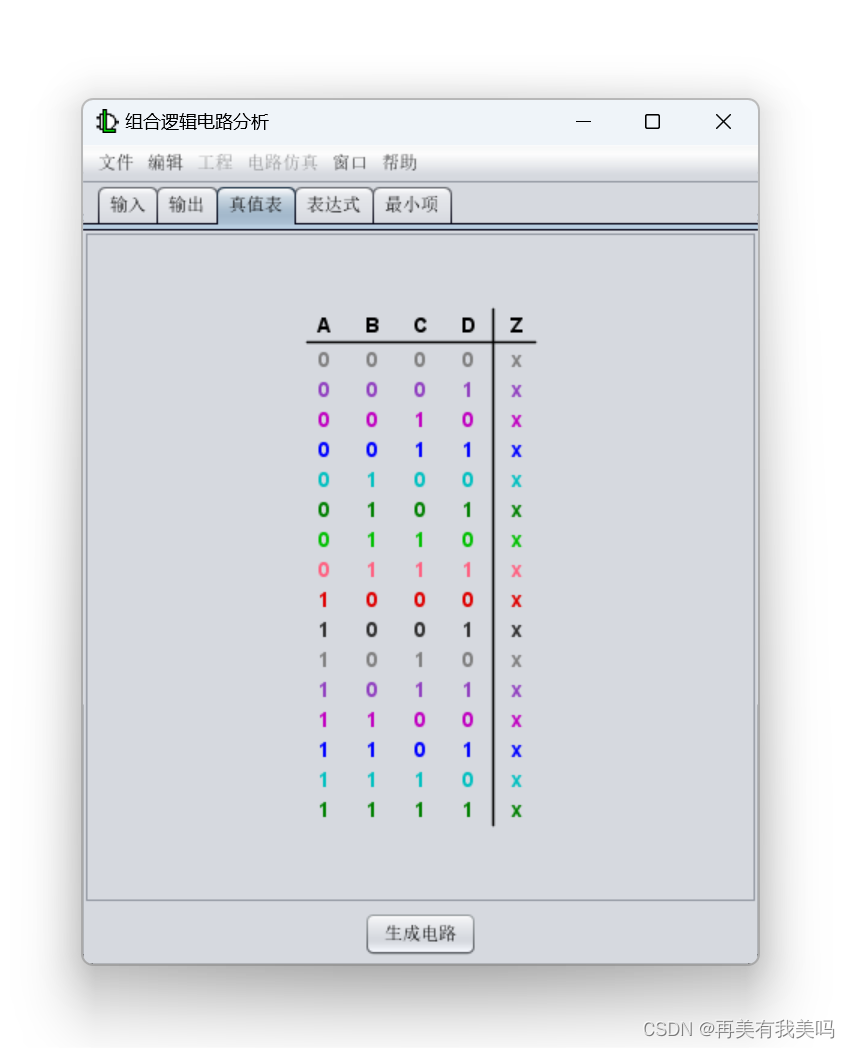

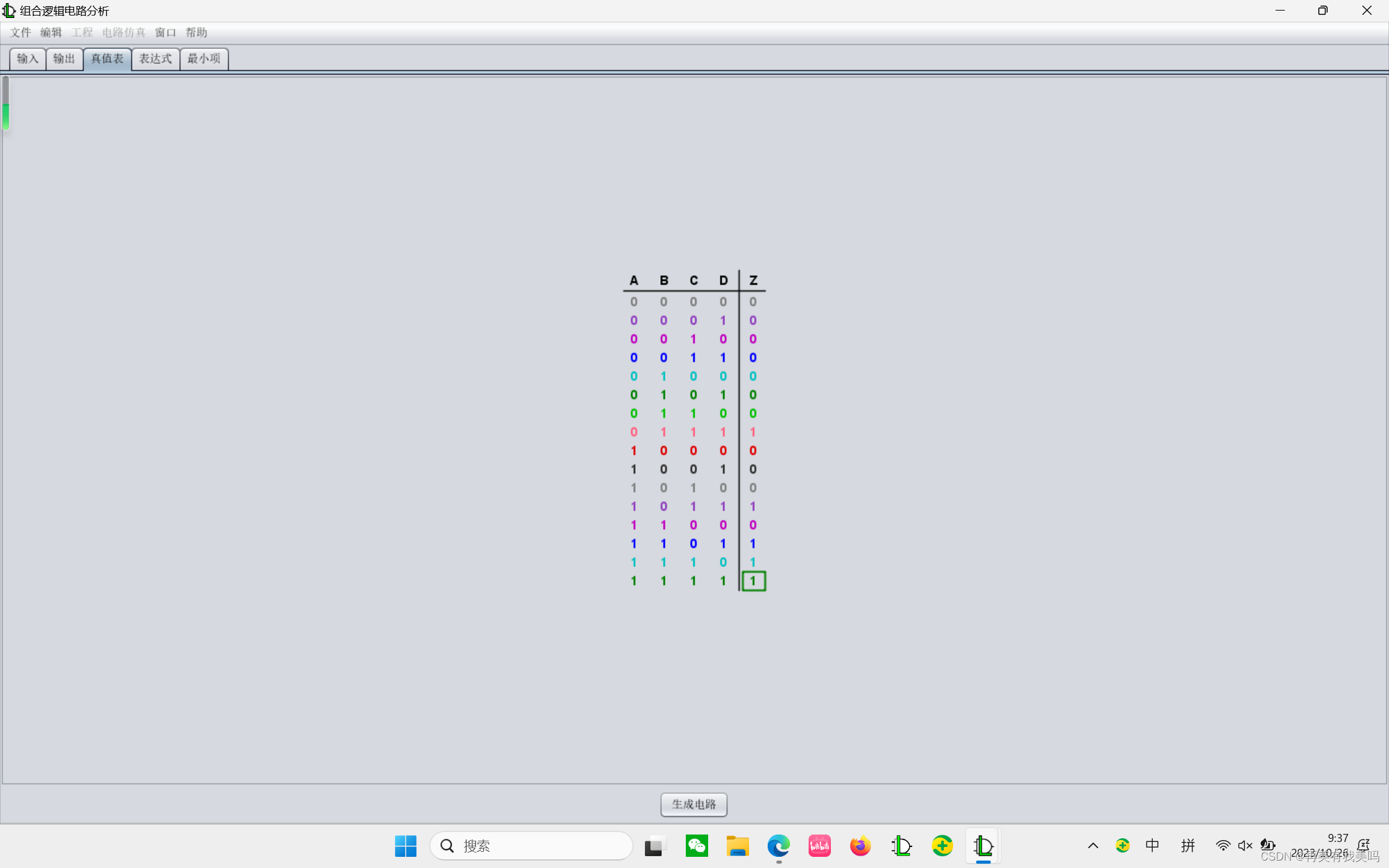

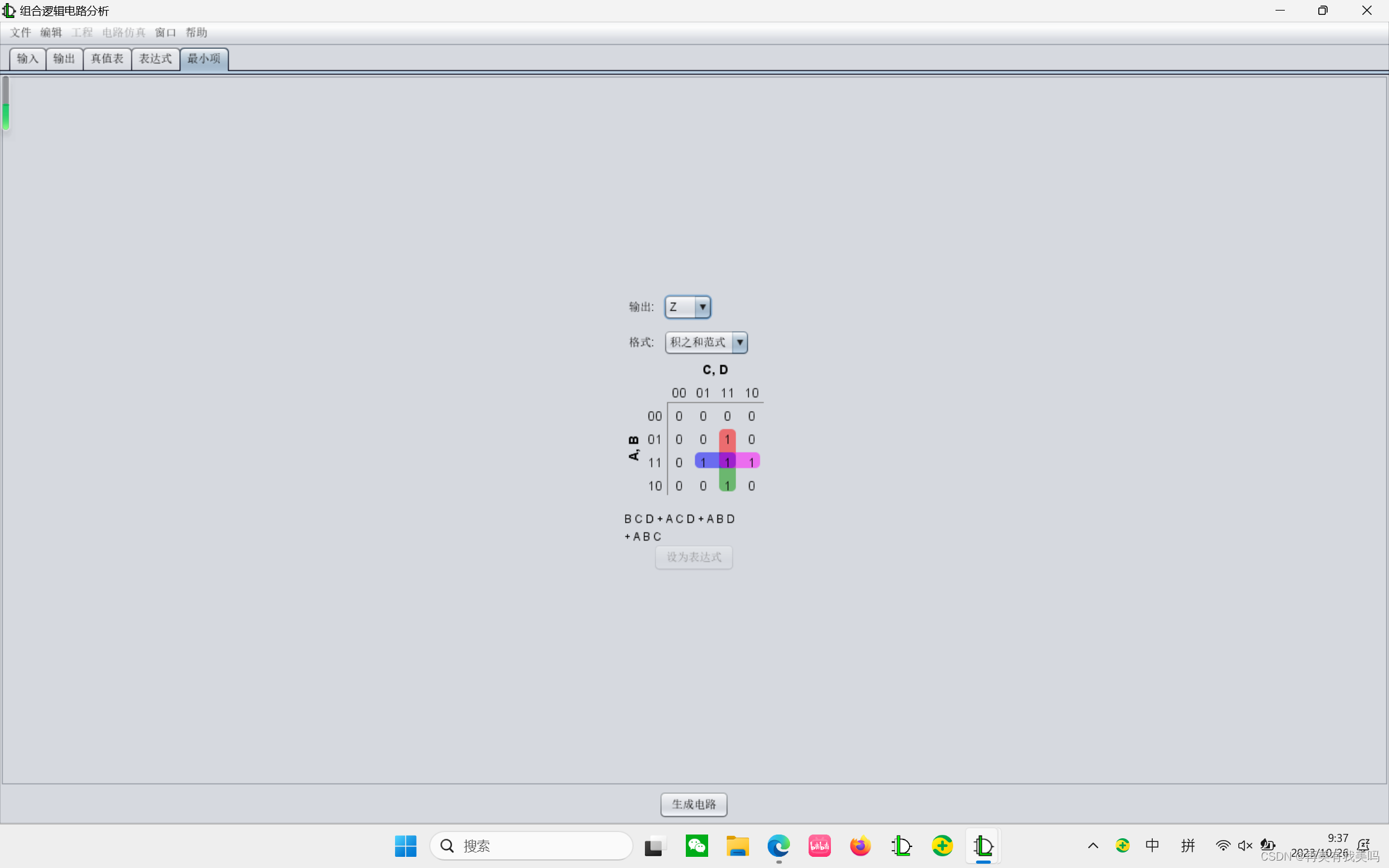

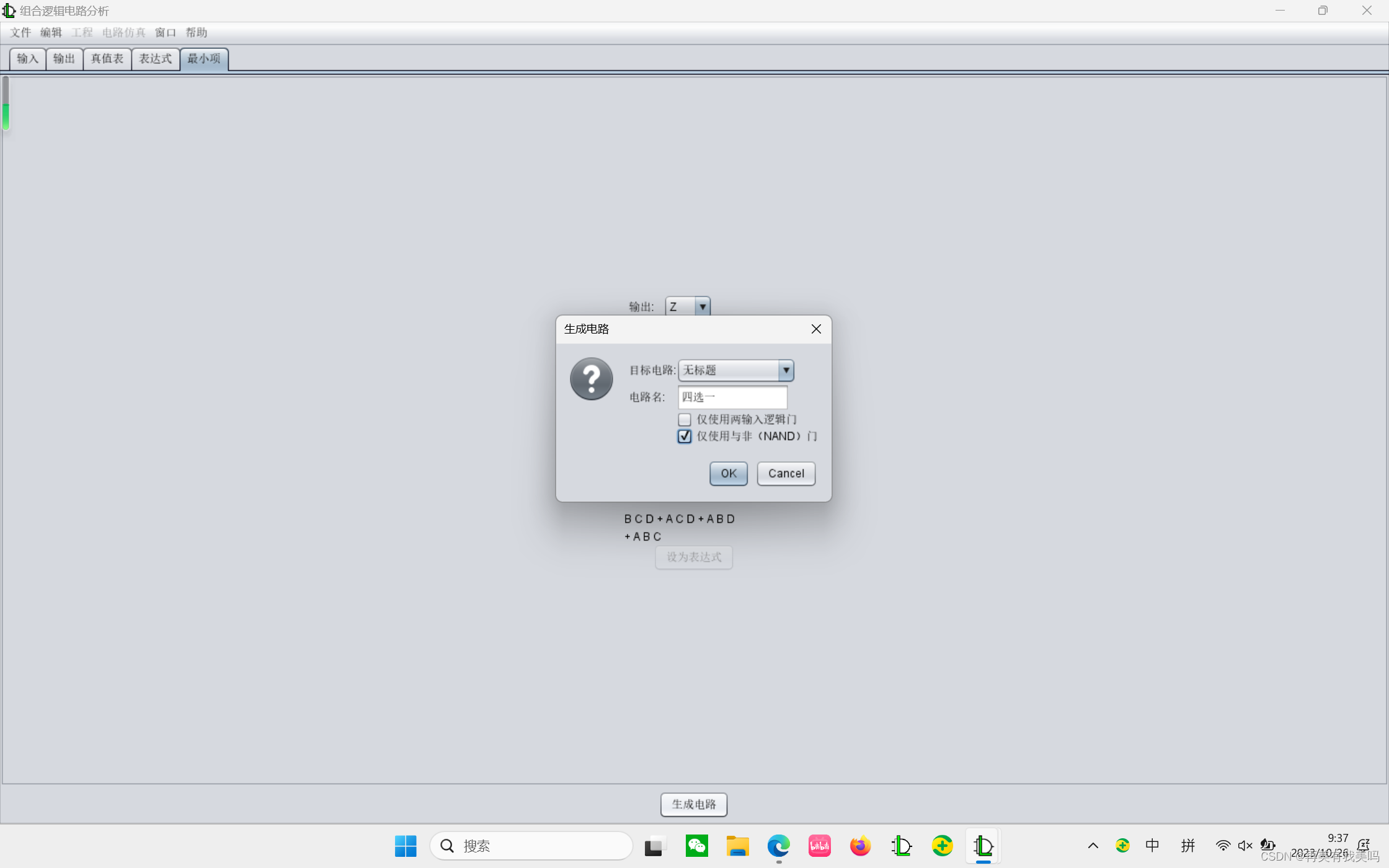

使用Logsim的提供的“分析组合逻辑电路”的智能功能,重新完成 4路表决器实验。

步骤如下:

点击ok键,生成电路,即可得到:

六、总结

1.在实验前应该先在logisim上进行仿真实验然后再进行具体实现

2.牢记公式化简的基本定理才能更高效地化简组合逻辑电路

3.使用Logsim的提供的“分析组合逻辑电路”的智能功能可以帮助我们更快地进行虚拟实验,提高效率。

2009

2009

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?