DC电参数测试

输入电流(IIL/IIH)

IIL测试测量的是输入管脚到VDD的阻抗,IIH测的是的输入到VSS的阻抗(VSS在COMS电路中这是接地,VDD是芯片内部的电源)

测试目的:

符合阻抗要求

测试方法

串行(静态)测试法

IIL测试

(1)先给电源端VDDmax值,同时将所有管脚通过Pin Driver施加VIH,使预处理的为逻辑1实现预处理;

(2)接入DC测试资源连接到管脚,同时驱动低电平输入

(3)测量电流并且比较

注意:(1)IIH的测试在IIL的测试上将预处理的逻辑改为0;

(2)同时Drive改为1;但是IIH有钳制要求

(3)注意PMU的延迟,测量时要确认VDD、Vin及IIL/IIH等设置的正确。

优缺点:

串行测试是对每一个管脚进行测试,所以每一个测试管脚与不同管脚之间的具有电压差,所以使管脚之间的漏电流会更加的明显,但是会大大的增加测试的时间。

并行(静态)测试法

拥有Per Pin PMU的ATE支撑进行并行测试,所谓的并行其实就是给每一个管脚单独给电流,再判断是否符合设计;

集体测试法

由单个PMU对所有的管脚进行测试,集体输出管脚逻辑1,测试总电流,再集体输出管脚逻辑0,测试总电流

集体测试对COMS器件的效果比较好,因为COMS器件的阻抗比较高,电流的一般为0,出现问题电流的变化也是很明显的

对于以下情况不适合使用:(1)特定的低阻抗管脚。(2)外接上拉下拉等对电流消耗大的

优点:不用强调Per Pin PMU的结构,同时速度快;但是只适合高阻抗的输入器件,对于出现问题也只能用串行的测试在测试一遍;

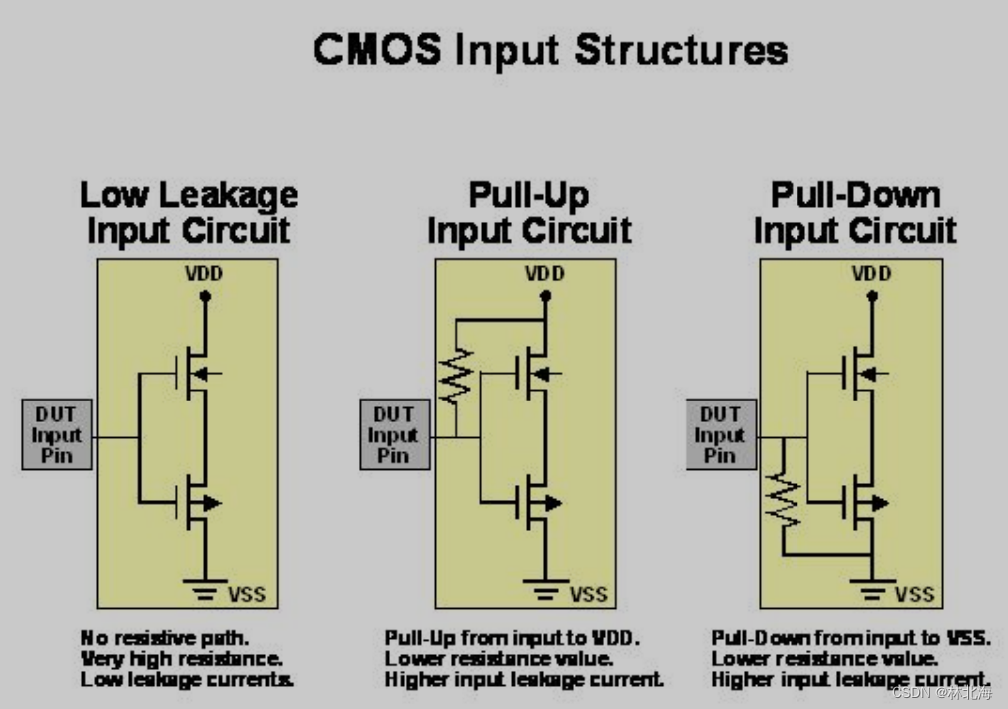

输入结构-高阻/上拉/下拉

部分管脚具有上拉和下拉,所以会导致每个管脚的所可以吸收的电流大小并不相同,所以集体测试的方法并不适合用来测试。同时阻抗输入也会影响器件的IDD电流,也取决与每一个输入管脚上输入的管脚

输出扇出

输出扇出指的是一个管脚控制接入多个输出管脚的能力;

TTL电路和COMS电路不一样:

传统的COMS电路一个COMS可以驱动多个COMS输入,只要是将足够

高阻电流(High Impedance Currents,IOZH/IOZL)

IOZL指的是当一个低电平施加在一个有高阻态的输出管脚上,管脚所产生的漏电流(I);IOZH指的则是给一个高电平,其他的条件不发生改变

IOZL测试的是VDD到管脚的阻抗,IOZH测试的是管脚到GND的阻抗

测试方法:

1.串行/静态测试法

施加VDD,使整个器件都在高阻态的向量,PMU可以以此驱动高低管脚管脚测试电流值;

要保证VDD和VOZ不会出现错误

2.并行测试法

施加VDD,使整个器件都在高阻态的向量,PMU可以以此驱动高低管脚管脚测试电流值;

要保证VDD和VOZ不会出现错误(同样需要Per pin PMU的结构)

注意:(1)集成测试并不适合

故障分析

1.情况1:测试不通过,但是输出的值的大小在与预定值的附近

可能是器件在生产中出现的问题,导致VDD到管脚出现导致的漏电流(可以用精确的电阻进行代替测试调整)

2.情况2:不通过,但是输出的电流远远超出我们的预定值;可能是器件的重大缺陷或者是有杂质在Loadbroad上

输出短路电流(Output short circuit current)(IOS)

解释:输出口位于短路时的电流

目的:可以保证在短路状态下,短路电流可以控制在可以接受的情况下;同时可以控制上升沿的信号速度

方法:(1)预处理:将每一个管脚都设置成输出为逻辑1,

(2)再施加0V到其中的输出管脚;

(3)测量电流并且比较大小

同时要避免热切换,器件预处理为1后,电压在VOH和VDD中,一旦PMU驱动短接到器件上,电压差会导致高速电流,这就导致热切换的问题到来;

1474

1474

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?