1.存储器层次结构

在简单模型中,存储器系统是一个线性的字节数组,而CPU能够在一个常数时间内访问每个存储器位置。

实际上,存储器系统(memory system)是一个具有不同容量、成本和访问时间的存储设备的层次结构。CPU寄存器保存着最常用的数据。靠近CPU的小的、快速的高速缓存存储器(cache memory)作为一部分存储在相对慢速的主存储器(main memory)中数据和指令的缓冲区域。主存缓存存储在容量较大的、慢速磁盘上的数据,而这些磁盘常常又作为存储在通过网络连接的其他机器的磁盘或磁带上的数据的缓冲区域。

存储器层次结构它对应用程序的性能有着巨大的影响。

例如:

如果程序需要的数据是存储在CPU寄存器中的,那么在指令的执行期间,在 0个周期内就能访问到它们。

如果存储在高速缓存中,需要4~75个周期。

如果存储在主存中,需要上百个周期。而如果存储在磁盘上,需要大约几千万个周期!

1.1 存储技术

随机访问存储器(Random-Access Memory, RAM)分为两类:

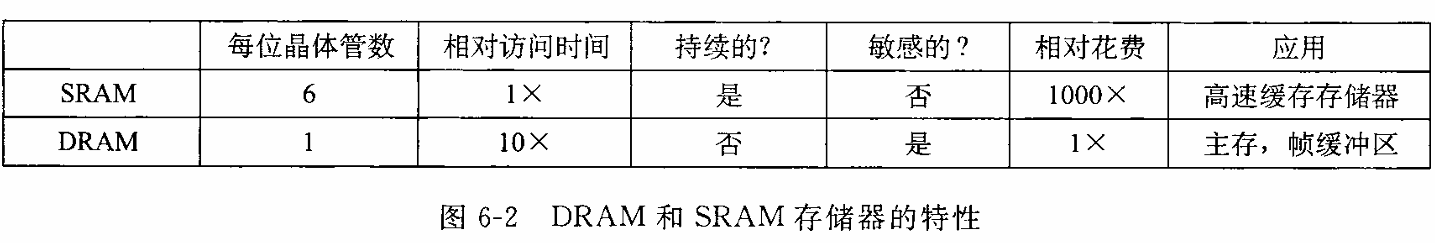

静态的和动态的。静态 RAM(SRAM)比动态RAM(DRAM)更快,但也贵得多。SRAM用来作为高速缓存存储器,既可以在CPU芯片上,也可以在片下。DRAM用来作为主存以及图形系统的帧缓冲 区。典型地,一个桌面系统的SRAM不会超过几兆字节,但是DRAM却有几百或几千兆字节。

1. 静态RAM

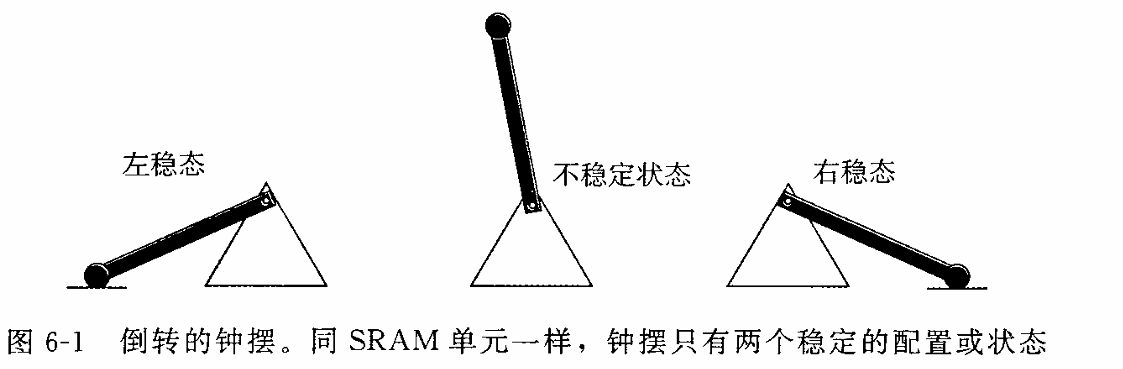

SRAM将每个位存储在一个双稳态的(Instable)存储器单元里。每个单元是用一个六晶体管电路来实现的。这个电路有这样一个属性,它可以无限期地保持在两个不同的电压配置(configuration)或状态(state)之一。其他任何状态都是不稳定的一从不稳定状态开始,电路会迅速地转移到两个稳定状态中的一个。

由于SRAM存储器单元的双稳态特性,只要有电,它就会永远地保持它的值。即使有干扰(例如电子噪音)来扰乱电压,当干扰消除时,电路就会恢复到稳定值。

2. 动态RAM

DRAM将每个位存储为对一个电容的充电。这个电容非常小,通常只有大约30毫微微法拉(femtofarad)—30X10 负十五次方法拉。

DRAM存储器可以制造得非常密集—每个单元由一个电容和一个访问晶体管组成。但是,与SRAM不同,DRAM存储器单元对干扰非常敏感。当电容的电压被扰乱之后,它就永远不会恢复了。暴露在光线下会导致电容电压改变。实际上,数码照相机和摄像机中 的传感器本质上就是DRAM单元的阵列。

SRAM 和DRAM存储器的特性如上图。只要有供电,SRAM就会保持不变。 与DRAM不同,它不需要刷新。

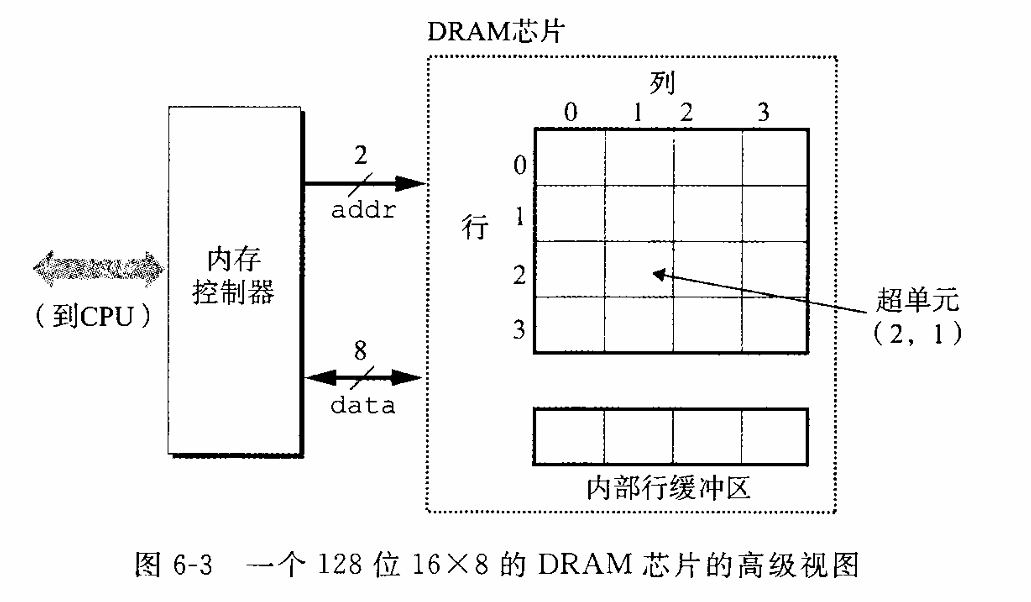

3. 传统的DRAM

DRAM芯片中的单元(位)被分成d个超单元(supercell),每个超单元都由 w个 DRAM 单元组成。一个加的DRAM总共存储了如位信息。一个 d×w的DRAM总共存储了dw位信息。超单元被组织成一个r行c列的长方形阵列,这里rc=d。每个超单元有形如(i,j)的地址,这里i表示行,而 j表示列。

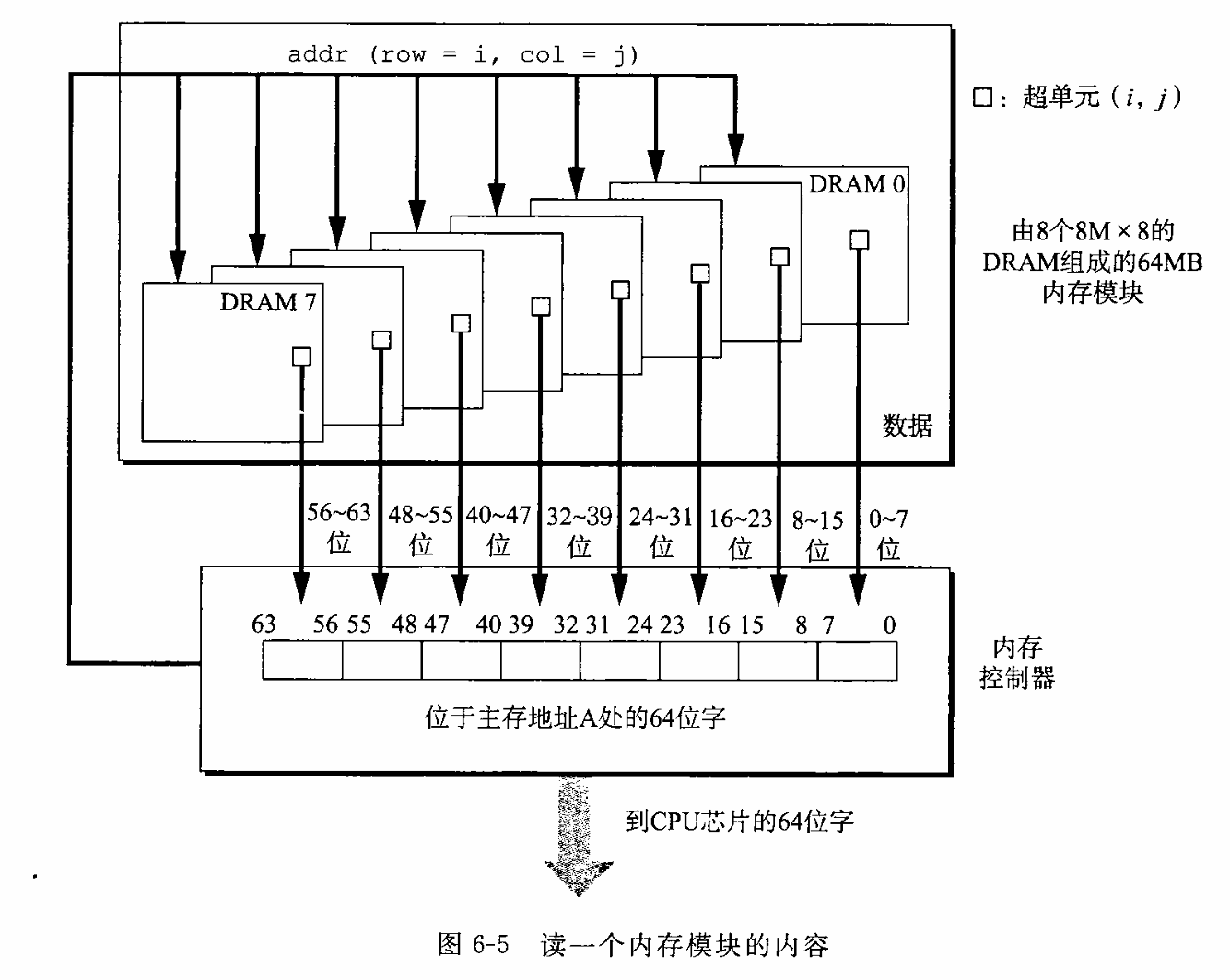

4. 内存模块

DRAM芯片封装在内存模块(memory module)中,它插到主板的扩展槽上。Core i7 系统使用的240个引脚的双列直插内存模块(Dual Inline Memory Module,DIMM), 它以 64 位为块传送数据到内存控制器和从内存控制器传出数据。

如图展示了一个内存模块的基本思想

图中所示模块用8个64 Mbit的8 MX8的DRAM 芯片,总共存储64MB(兆字节),这8个芯片编号为0~ 7。

5. 増强的DRAM

一些优化过的DRAM如下:

(1)快页模式DRAM(Fast Page Mode DRAM, FPM DRAM)。传统的 DRAM 将超单元的一整行复制到它的内部行缓冲区中,使用一个,然后丢弃剩余的。FPM DRAM允许对同一行连续地访问可以直接从行缓冲区得到服务,从而改进了这一 点。

(2)扩展数据输出DRAM(Extended Data Out DRAM, EDO DRAM)。FPM DRAM的一个增强的形式,它允许各个CAS信号在时间上靠得更紧密一点。

(3)同步DRAM(Synchronous DRAM, SDRAM)。就它们与内存控制器通信使用一组显式的控制信号来说,常规的、FPM和EDODRAM都是异步的。SDRAM用与驱动内存控制器相同的外部时钟信号的上升沿来代替许多这样的控制信号。

(4)双倍数据速率同步 DRAM(Double Data Rate Synchronous DRAM, DDR SDRAM)。 DDR SDRAM是对SDRAM的一种增强,它通过使用两个时钟沿作为控制信号, 从而使DRAM的速度翻倍。

(5)视频RAM(VideoRAM, VRAM)。它用在图形系统的帧缓冲区中。VRAM的思想 与FPMDRAM类似。两个主要区别是:1)VRAM的输出是通过依次对内部缓冲 区的整个内容进行移位得到的;2)VRAM允许对内存并行地读和写。

6. 非易失性存储器

如果断电,DRAM和SRAM会丟失它们的信息,从这个意义上说,它们是易失的 (volatile)。另一方面,非易失性存储器(nonvolatile memory)即使是在关电后,仍然保存着它们的信息。现在有很多种非易失性存储器。

PROM(Programmable ROM, 可编程 ROM)只能被编程一次。PROM的每个存储器单元有一种熔丝(fuse),只能用高电流熔断一次。

可擦写可编程ROM(Erasable Programmable ROM, EPROM)有一个透明的石英窗口,允许光到达存储单元。紫外线光照射过窗口,EPROM单元就被清除为 0。

闪存(flash memory)是一类非易失性存储器,基于 EEPROM,它已经成为了一种重要的存储技术。

7.访问主存

数据流通过称为总线(bus)的共享电子电路在处理器和DRAM主存之间来来回回。每次CPU 和主存之间的数据传送都是通过一系列步骤来完成的,这些步骤称为总线事务 ( bus transaction)。读事务(read transaction)从主存传送数据到 CPU。写事务(write transaction) CPU 传送数据到主存。

总线是一组并行的导线,能携带地址、数据和控制信号。取决于总线的设计,数据和地址信号可以共享同一组导线,也可以使用不同的。

本文详细介绍了存储器层次结构,包括CPU、高速缓存、主存和磁盘的不同层级,强调了不同存储技术(如SRAM和DRAM)的特点及其在性能上的差异。同时涵盖了内存模块、非易失性存储器(如PROM、EPROM和闪存)以及数据在处理器和主存间通过总线传输的过程。

本文详细介绍了存储器层次结构,包括CPU、高速缓存、主存和磁盘的不同层级,强调了不同存储技术(如SRAM和DRAM)的特点及其在性能上的差异。同时涵盖了内存模块、非易失性存储器(如PROM、EPROM和闪存)以及数据在处理器和主存间通过总线传输的过程。

3617

3617

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?