要根据需求调整基于 74LS161 的电路计数值范围,以构建 12 进制计数器为例,下面为你详细介绍具体的原理、方法和实现步骤。

原理

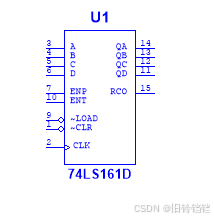

74LS161 是 4 位二进制同步计数器,其计数范围是从 0000(十进制的 0)到 1111(十进制的 15),共 16 个状态。要实现 12 进制计数器,就需要让计数器在计到 11(二进制 1011)后,下一个状态回到 0,跳过 12 - 15 这几个状态。

方法

实现 12 进制计数器通常有两种方法:异步清零法和同步置数法。

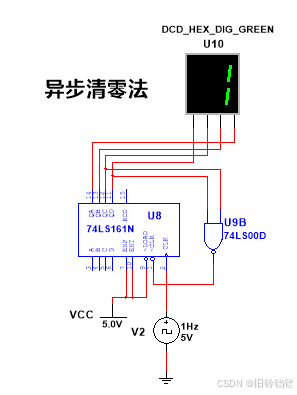

异步清零法

- 原理:利用 74LS161 的异步清零端 ,当计数器计到 12(二进制 1100)时,产生一个清零信号使计数器立即清零。需要注意的是,由于是异步清零,计数器会短暂出现 12 这个状态,然后迅速清零。

- 电路连接

- 把时钟信号连接到 74LS161 的时钟输入端 。

- 使能端ENP 和 ENT 接高电平(Vcc),允许计数器计数。

- 置数端LOAD 接高电平(Vcc),不使用置数功能。

- 数据输入端ABCD 可以任意连接,因为不使用置数功能。

- 用一个与非门,将 Q2 和 Q3作为与非门的输入(因为计到 12 时 ,Q2=1,Q3=1),与非门的输出连接到 CLR 端。

- 代码示例(以 Proteus 仿真中的逻辑表达式表示)

收起

plaintext

CLR = NOT(Q2 AND Q3)

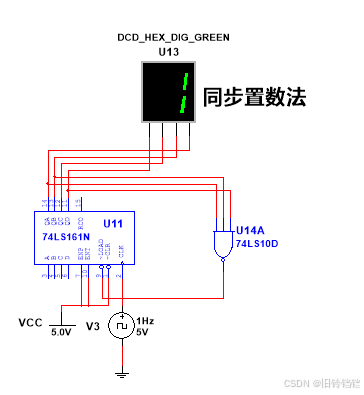

同步置数法

- 原理:利用 74LS161 的同步置数端 ,当计数器计到 11(二进制 1011)时,在下一个时钟脉冲到来时,将计数器置为 0。与异步清零法不同,同步置数不会出现短暂的多余状态。

- 电路连接

- 时钟信号连接到 端。

- 使能端 ENP 和 ENT接高电平()。

- 数据输入端ABCD 都接低电平(地),即置数为 0。

- 用一个与非门,将Q0 、Q1 和 Q3 作为与非门的输入(因为计到 11 时 ,Q0=1,Q1=1Q3=1),与非门的输出连接到 LOAD 端。

- 代码示例(以 Proteus 仿真中的逻辑表达式表示)

收起

plaintext

LOAD = NOT(Q0 AND Q1 AND Q3)

总结

通过上述两种方法,你可以将基于 74LS161 的计数器调整为 12 进制计数器。异步清零法实现简单,但会有短暂的多余状态;同步置数法没有多余状态,但电路连接相对复杂一些。你可以根据实际需求选择合适的方法。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?