74LS161 是一款常用的 TTL(晶体管 - 晶体管逻辑)集成电路,属于 4 位二进制同步计数器,下面将从基本信息、引脚功能、工作模式、应用场景等方面详细介绍:

基本信息

- 所属系列:74LS 系列是低功耗肖特基 TTL 集成电路,具有功耗较低、速度较快等特点,在数字电路设计中应用广泛。

- 功能用途:主要用于对时钟信号进行计数操作,可实现二进制计数、分频、定时等多种功能。

引脚功能

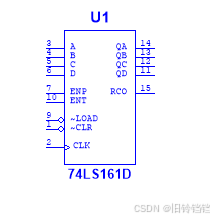

74LS161 一般采用 16 引脚双列直插式封装,各引脚功能如下:

| 引脚编号 | 引脚名称 | 功能描述 |

|---|---|---|

| 1 | CLR | 异步清零端,低电平有效。当该引脚输入低电平时,计数器立即被清零,与时钟信号无关。 |

| 2 | D0 | 并行数据输入端 0,用于同步置数时输入数据。 |

| 3 | D1 | 并行数据输入端 1,用于同步置数时输入数据。 |

| 4 | D2 | 并行数据输入端 2,用于同步置数时输入数据。 |

| 5 | D3 | 并行数据输入端 3,用于同步置数时输入数据。 |

| 6 | CLK | 时钟输入端,计数器在时钟信号的上升沿进行计数或其他操作。 |

| 7 | LOAD | 同步置数端,低电平有效。当该引脚为低电平且时钟信号上升沿到来时,将 端的数据并行置入计数器。 |

| 8 | ENP | 计数使能端 P,高电平有效。当 和 都为高电平时,计数器正常计数。 |

| 9 | ENT | 计数使能端 T,高电平有效。当 和 都为高电平时,计数器正常计数,同时 还控制进位输出 。 |

| 10 | Q0 | 计数器输出端 0,输出计数值的最低位。 |

| 11 | Q1 | 计数器输出端 1。 |

| 12 | Q2 | 计数器输出端 2。 |

| 13 | Q3 | 计数器输出端 3,输出计数值的最高位。 |

| 14 | RCO | 进位输出端,当计数器计到 1111 时, 输出高电平,可用于级联多个计数器。 |

| 15 | GND | 接地端。 |

| 16 | Vcc | 电源端,一般接 +5V 电源。 |

工作模式

- 计数模式:当CLR=1 (高电平),LOAD=1(高电平),ENP=1(高电平),ENT=1(高电平)时,计数器在时钟信号 的上升沿进行计数,计数值从 0000 递增到 1111,共 16 个状态。

- 异步清零模式:当 CLR=0(低电平)时,无论其他引脚状态如何,计数器立即被清零,输出 Q3Q2Q1Q0 变为 0000。

- 同步置数模式:当 CLR=1(高电平),LOAD=0(低电平)时,在时钟信号 CLK 的上升沿,将D0-D3 端的数据并行置入计数器,使Q3Q2Q1Q0=D3D2D1D0 。

应用场景

- 数字时钟:可用于实现时钟的秒、分、时计数功能,通过级联多个 74LS161 芯片,并结合适当的译码和显示电路,能构成完整的数字时钟系统。

- 分频电路:利用 74LS161 的计数功能,可将输入的高频时钟信号进行分频,得到所需的低频信号。例如,将 16MHz 的时钟信号分频为 1MHz 的信号。

- 序列信号发生器:通过合理设置并行数据输入端 和控制信号,可产生特定的序列信号,用于通信、测试等领域。

74LS161、74LS160、74LS163 都是常用的数字集成电路计数器,它们的区别主要体现在以下几个方面:

计数进制

- 74LS161:是 4 位二进制同步计数器,为 16 进制计数器,计数范围从 0000 到 1111123。

- 74LS160:是 4 位十进制同步计数器,计数范围从 0000 到 1001,即 0 到 914。

- 74LS163:是 4 位二进制同步计数器,属于 16 进制计数器,计数范围从 0000 到 1111134。

清零方式

- 74LS161:采用异步清零方式。只要在清零输入端 MR 输入低电平,计数器就会立即清零,不需要等待时钟脉冲123。

- 74LS160:也是异步清零,在清零端输入低电平可立即清零1。

- 74LS163:采用同步清零方式。在清零输入端 MR 输入低电平后,需要在下一个时钟脉冲到来时才会清零13。

应用场景

- 74LS161:适用于需要二进制计数或对二进制数据进行处理的电路,如数字分频器、数字时钟电路、地址发生器等,可方便地实现 2 的幂次方分频。

- 74LS160:常用于需要十进制计数的场合,如数字显示电路、计数式定时器、频率计的十进制计数部分等,符合人们日常的十进制计数习惯。

- 74LS163:在需要精确同步二进制计数的系统中使用,如一些对计数同步性要求较高的数字逻辑电路、数据存储地址计数等场景。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?