设计方式:

一、设计思路

- 地址处理:

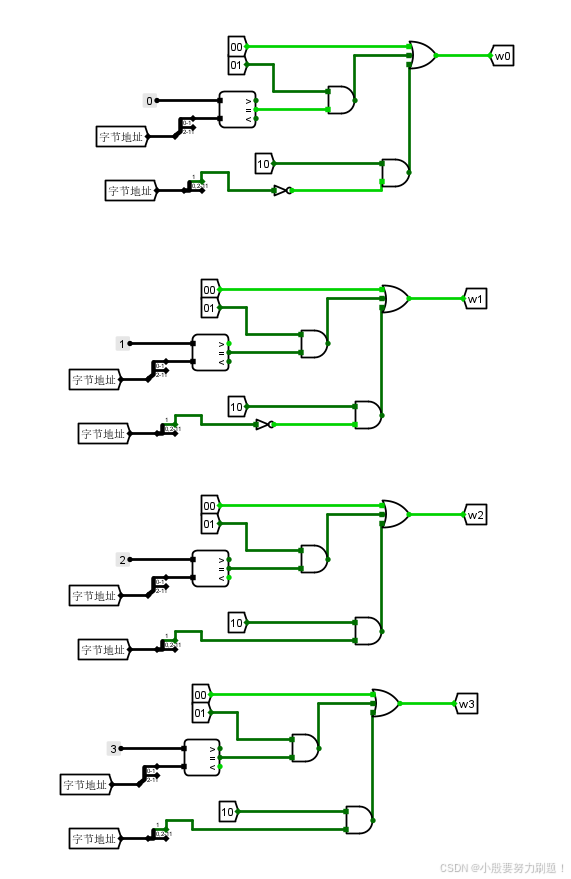

- 由于Addr是12位字节地址输入,我们需要根据Mode来选择合适的地址位。

- 字访问时(Mode=00),忽略Addr的最低2位,因为1个字由4个字节组成,地址需要右移2位(除以4)来选择正确的字。

- 半字访问时(Mode=10),忽略Addr的最低位,并使用倒数第二位作为片选信号来选择两个RAM中的一个(因为1个半字由2个字节组成,地址需要右移1位,但此处我们还需要用最低位未忽略前的值来决定是访问RAM0/1还是RAM2/3中的哪一个半字)。

- 字节访问时(Mode=01),直接使用Addr的最低2位来进行片选,以选择4个RAM中的一个。

- 数据处理:

- Din是32位写入数据,根据Mode将数据拆分并写入对应的RAM。

- Dout是32位读出数据,从对应的RAM中读取数据后,根据Mode将数据拼接成32位。

- 控制信号:

- WE是写使能信号,控制数据的写入或读出。

二、电路设计

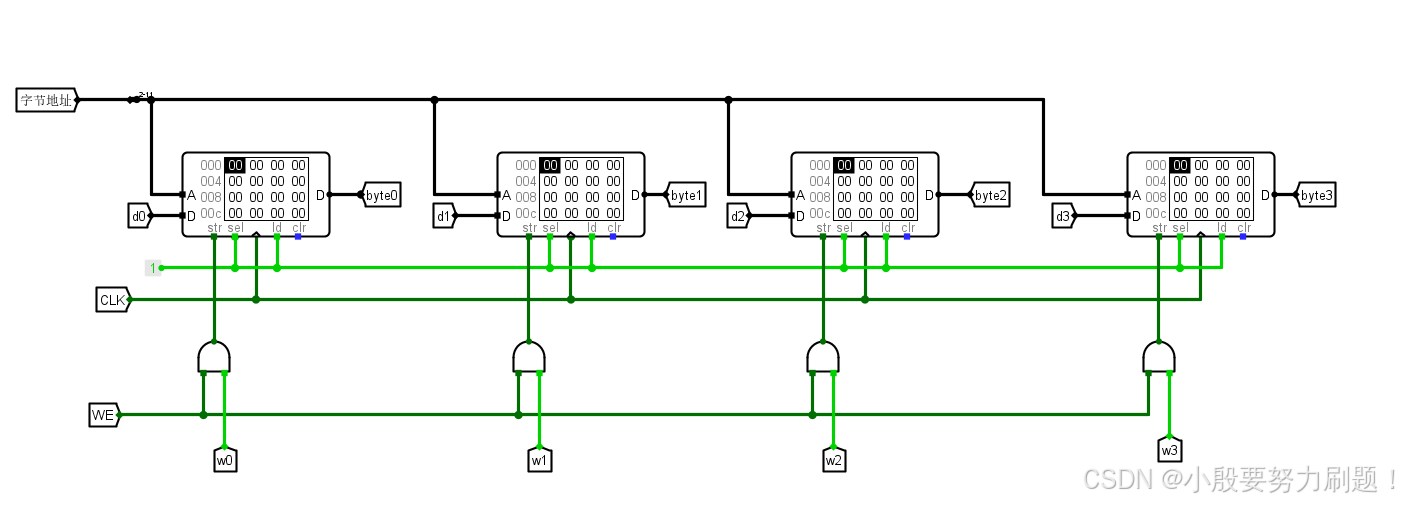

- 地址解码与选择:

- 使用多个多路选择器(Multiplexer)和逻辑门(Logic Gates)来实现地址的解码和RAM的选择。

- 根据Mode的值,选择相应的地址位,并通过多路选择器将地址信号送到正确的RAM。

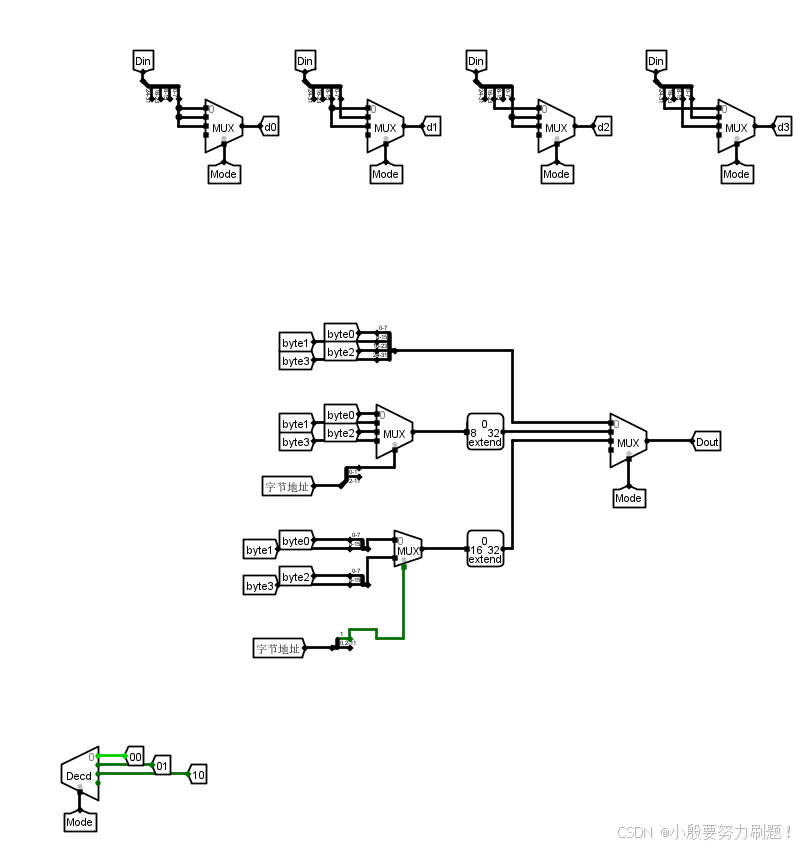

- 数据拆分与拼接:

- 使用多个拆分器(Splitter)和合并器(Merger)来处理Din和Dout。

- 根据Mode的值,将Din拆分成8位、16位或32位的数据块,并写入对应的RAM。

- 从RAM中读取数据时,根据Mode的值,将8位、16位或32位的数据块拼接成32位的Dout。

- 写使能控制:

- 使用逻辑门来控制WE信号,确保在正确的时机写入或读出数据。

三、输入输出引脚连接

- Addr:连接到地址解码与选择电路。

- Din:连接到数据拆分电路。

- Dout:从数据拼接电路输出。

- Mode:控制地址解码与选择电路和数据拆分/拼接电路。

- WE:控制写使能信号。

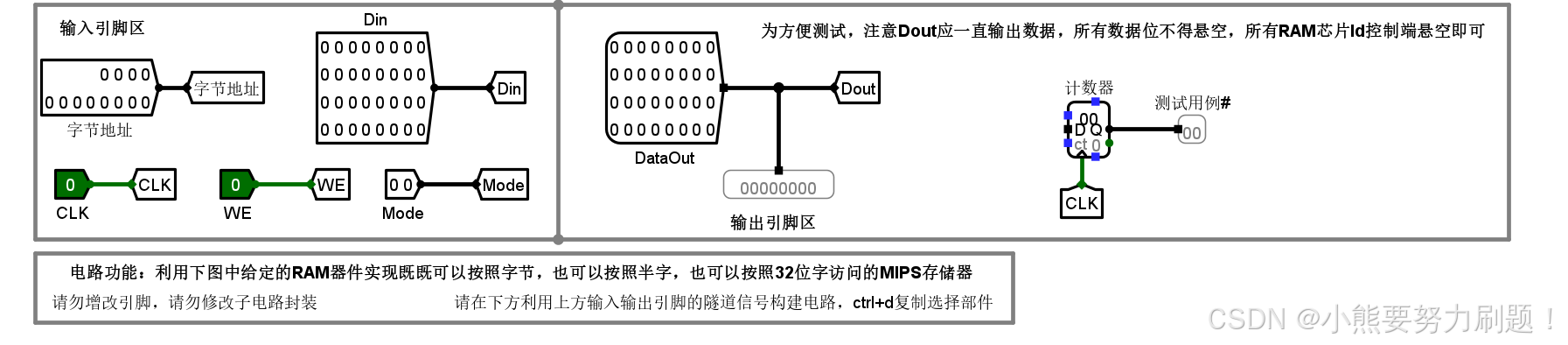

四、封装与测试

- 完成电路设计后,将电路封装成一个子电路,命名为MIPS RAM。

- 在Logisim中创建一个新的测试电路,将MIPS RAM子电路实例化到测试电路中。

- 通过设置不同的Addr、Din、Mode和WE值,测试MIPS RAM子电路的功能是否正确。

五、注意事项

- 在设计过程中,要注意地址的边界条件和数据的对齐问题。

- 确保在不同访问模式下,数据的读写都是正确的。

- 测试时要覆盖所有可能的输入组合,以确保电路的稳定性和可靠性。

实验设计要求的详细说明:

要设计一个既能按照8位(字节),也能按照16位(半字),还能按照32位(字)进行读写的32位存储系统,我们可以利用4个1KB×8位的RAM组件进行扩展。这些RAM组件的地址是10位的(因为2^10 = 1024 = 1KB),每个RAM的数据宽度是8位。

我们的目标是构建一个32位的存储系统,其总容量为4KB(因为4个1KB的RAM组件),地址位宽为12位(因为2^12 = 4096 = 4KB),并且可以通过控制信号选择访问模式(字节、半字、字)。

解决方案

- 地址处理:

- Addr是一个12位的地址输入,表示字节地址。

- 根据Mode的不同,我们需要调整Addr以选择正确的RAM和字节偏移。

- 数据处理:

- Din是32位的写入数据,我们需要根据Mode将其拆分并写入相应的RAM。

- Dout是32位的读出数据,我们需要从相应的RAM读取数据并合并。

- 控制信号:

- Mode是一个2位的控制信号,决定访问模式(00: 字访问,01: 字节访问,10: 半字访问)。

- WE是一个写使能信号,1表示写入,0表示读出。

详细设计

- 地址处理:

- 字节访问:Addr的低2位用于选择4个RAM中的一个(Addr[1:0]),高10位用于RAM内部地址(Addr[11:2])。

- 半字访问:Addr的最低位用于选择4个RAM中的一个(Addr[0]),Addr[1]作为片选信号(选择两个RAM中的一个对),高10位右移1位后用于RAM内部地址(Addr[11:2] >> 1)。

- 字访问:忽略Addr的低2位,高10位右移2位后用于RAM内部地址(Addr[11:2] >> 2),每次访问两个RAM(连续地址的两个块)。

- 数据处理:

- 写入时,根据Mode将Din拆分成多个8位数据块,并写入相应的RAM。

- 读取时,从相应的RAM读取数据,并根据Mode合并成32位数据。

- 电路实现:

- 使用多路选择器(Multiplexer)和地址解码器(Decoder)来处理地址和控制信号。

- 使用数据选择器(Data Selector)和合并器(Merger)来处理数据。

MIPS RAM封装引脚说明

- Addr:12位,字节地址输入。

- 字访问:忽略Addr[1:0]。

- 半字访问:Addr[1]作为片选信号,Addr[0]选择RAM。

- 字节访问:Addr[1:0]选择RAM。

- Din:32位,写入数据。

- 根据Mode拆分写入相应的RAM。

- Dout:32位,读出数据。

- 根据Mode从相应的RAM读取并合并。

- Mode:2位,访问模式控制位。

- 00:字访问

- 01:字节访问

- 10:半字访问

- WE:1位,写使能。

- 1:写入

- 0:读出

电路封装

- 地址解码和选择:

- 使用多路选择器根据Mode和Addr选择正确的RAM和地址。

- 数据写入和读取:

- 使用数据选择器拆分Din并写入相应的RAM。

- 使用数据合并器从相应的RAM读取数据并合并成Dout。

- 控制信号:

- 根据WE决定是读取还是写入。

字节、半字、字访问模式的实现:

想象一下,我们手头上有四块小黑板,每块小黑板只能写8个字(就像我们的1KB×8位RAM组件),但我们想要用它们来组成一个超级大的笔记本,这个笔记本一次可以写下32个字(就像我们的32位存储系统)。而且,我们还希望能够根据需要,以不同的方式在这个大笔记本上写字或者读字:一次写一个字(字访问)、一次写半个字(半字访问)或者一次只写一个单独的字(字节访问)。

字节访问模式

如果我们想一次只在这个大笔记本上写一个字,那么我们可以选择其中一块小黑板来写。这时,我们会用到地址的最低两位来决定是哪一块小黑板(因为我们有四块,所以刚好可以用两位地址来表示)。比如,地址的最后两位是00,那我们就选第一块小黑板;如果是01,就选第二块,以此类推。

半字访问模式

如果我们想一次写半个字(也就是16个字中的一部分),那么我们可以选择两块相邻的小黑板来写。这时,地址的最低位会告诉我们是从哪一块小黑板开始写的,而因为我们是写半个字,所以实际上会用到两块小黑板的前8个字或者后8个字。地址的第二低位(从0开始数第二位)就像一个开关,帮助我们选择是哪一对小黑板(第一和第二块,或者第三和第四块)。

字访问模式

如果我们想一次写一个完整的字(32个字),那么我们需要用到所有的四块小黑板。这时,我们可以忽略地址的最低两位,因为它们不会帮助我们选择小黑板(因为我们已经决定要用全部四块了)。我们只需要用剩下的地址位来决定在这四块小黑板上的哪个位置开始写字。

实现过程

1. 存储单元

假设我们有4个小的存储单元(可以想象成4个抽屉),每个存储单元可以存放8位数据(就像每个抽屉里可以放8个小物件)。

2. 地址与选择

我们有一个12位的地址(Addr),用于指定要访问的数据位置。这个地址同时用于选择存储单元和在该单元内的具体位置。

- 字节访问:使用地址的最低2位(Addr[1:0])来选择4个存储单元中的一个,剩下的10位(Addr[11:2])用于在该单元内定位数据。

- 半字访问:地址的最低位(Addr[0])用于选择存储单元对中的第一个或第二个(因为半字是16位,需要两个8位的存储单元)。地址的第二低位(Addr[1])作为一个“片选”信号,帮助我们选择哪一对存储单元(比如第一和第二单元,或第三和第四单元)。剩下的10位右移1位(Addr[11:2] >> 1)用于定位数据,因为每个半字跨越两个存储单元。

-

字访问:忽略地址的最低2位(Addr[1:0]),因为它们不会帮助我们选择存储单元(因为字是32位,需要四个存储单元)。剩下的10位右移2位(Addr[11:2] >> 2)用于定位数据,因为每个字跨越四个存储单元。

3. 数据处理

- 写入:根据访问模式,将32位的输入数据(Din)拆分成适当的块,并写入到选定的存储单元中。

- 读取:从选定的存储单元中读取数据,并根据访问模式将它们组合成一个32位的输出数据(Dout)。

4. 控制信号

- Mode:一个2位的控制信号,用于指示访问模式(00=字,01=字节,10=半字)。

- WE:一个写使能信号,用于指示是读取(WE=0)还是写入(WE=1)操作。

实现步骤(简化版)

- 选择存储单元:使用地址的最低几位和Mode信号来选择正确的存储单元或单元对。

- 定位数据:根据访问模式和地址的其余部分,计算存储单元内的数据位置。

- 数据处理:根据WE信号,执行读取或写入操作,并相应地处理数据。

- 输出:将处理后的数据作为32位的输出数据(Dout)。

电路展示:

948

948

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?