数据类型

Verilog数据类型

变量类型

线网类型

它们都是四值逻辑:1,0,x,z

reg,integer和time等变量类型可以用来存储组合逻辑/时序逻辑

reg在DC综合会变成latch和ff

说到这里:防止出现 latch:default/else

wire用于建模结构化描述中的连接线路和总线

线网的值由driver决定

驱动可以是门 || 模块的实例化描述 || 连续赋值的输出

变量只能用过程赋值来赋值

变量类型保存在 initial、always、task、function内赋的值

类型是integer/time的变量一般像有相同数量位数的reg一样工作

在表达式中integer的值时有符号数,而reg/time是无符号数

用reg描述逻辑,integer描述循环变量和计算,real在系统模型中使用,time和realtime保存测试装置的仿真时间

SystemVerilog新添加的数据类型

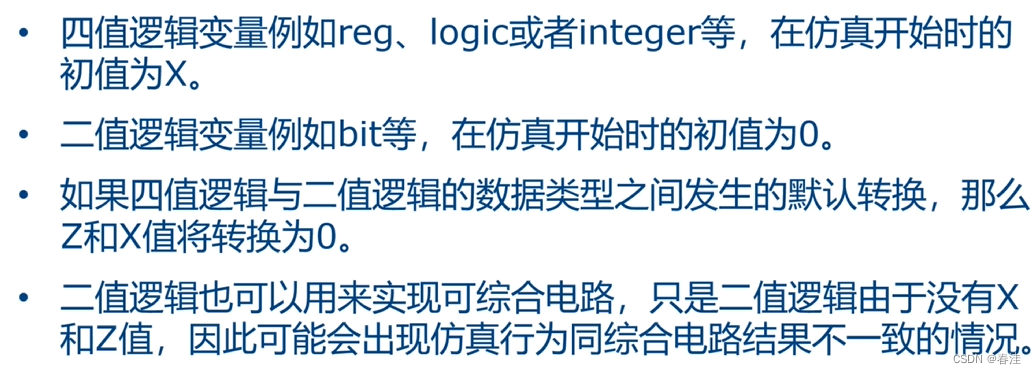

Verilog并没有严格区分信号的类型,变量和线网类型均是四值逻辑

高阻态在电路中表现为 没有驱动:悬空

一个ff在没有rst时输出表现为x,若d端没有输入时输出表现为z

------------------------------

SV将硬件信号区分为“类型”和“数据类型”

类型:variables wire

SV中碰到一个变量是由variables表示而非reg

reg与variables有何区别?

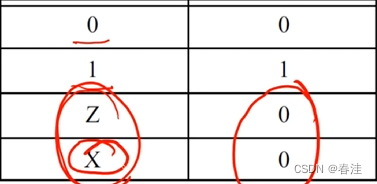

数据类型:四值逻辑类型 logic 二值逻辑类型 bit

线网赋值还是只能 assign

变量类型可以使用 连续 和 过程 赋值

---------------------------------

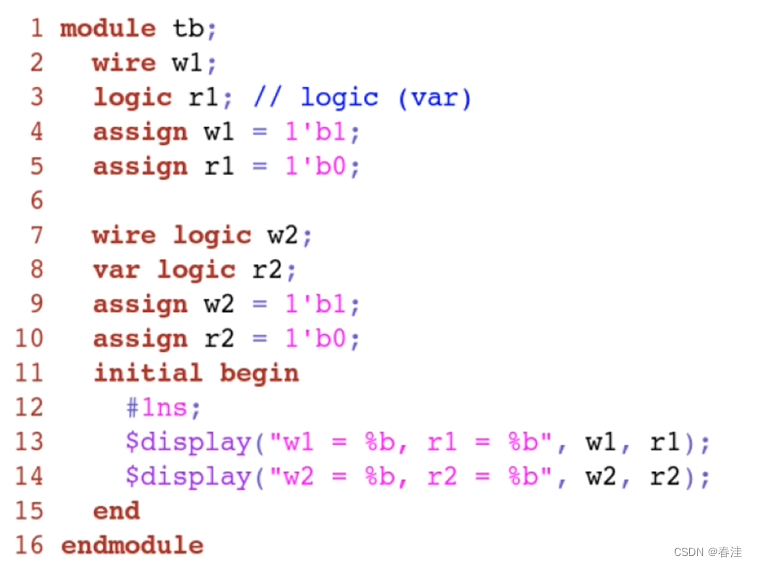

以后的tb文件多用logic而非wire

当多驱动的时候或者设计模块是inout的时候用wire

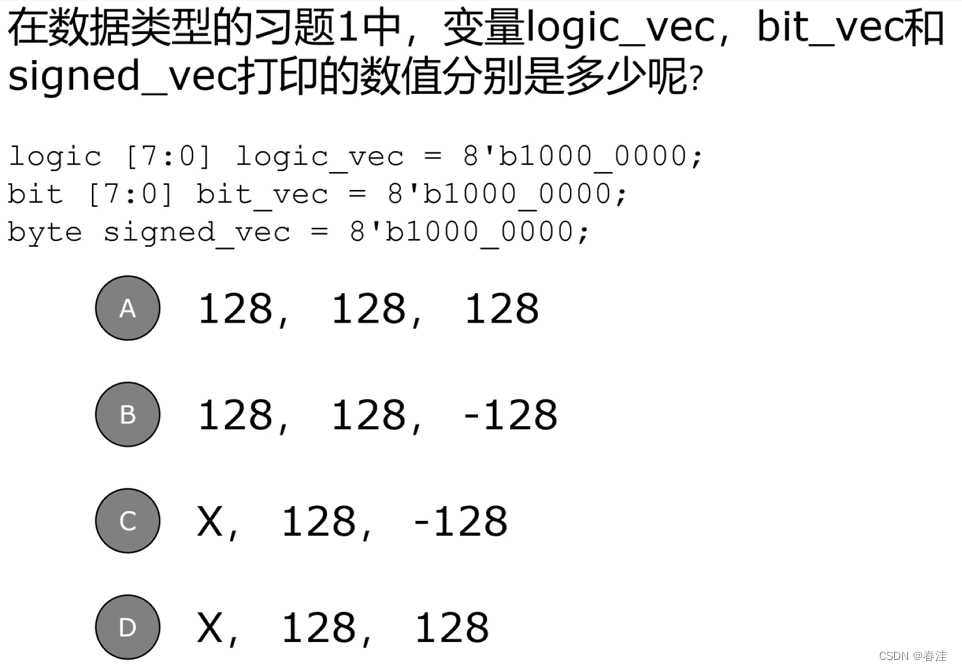

logic默认为无符号数

eg:logic可被连续赋值

---------------------------------------------

在Verilog中,reg不一定会被DC为register,它只是用来表示与wire相对应的一个变量

在SV中,我们可以直接使用logic来达到通用的存储硬件数据的目的

一个多位logic的各个bit的值是相互独立的

比如:

logic [63:0] addr 你要是16进制的,且这个值是0000_0000_0000_000X

你就不知道这个X用二进制展开后哪个bit是x,可能是0xxx,可能是000x等等,‘ 你需要通过查看波形来确定具体的x值

换句话说,你例化的这个64bit的addr相当于64个相互独立的register,互不影响

------------------------------------------

logic虽然只是表示一种数据类型,但是在声明时,他会默认表示为var类型

也可以显式声明它为wire:

(var) logic [63:0]addr

wire logic [63:0] data

----------------------------------------------

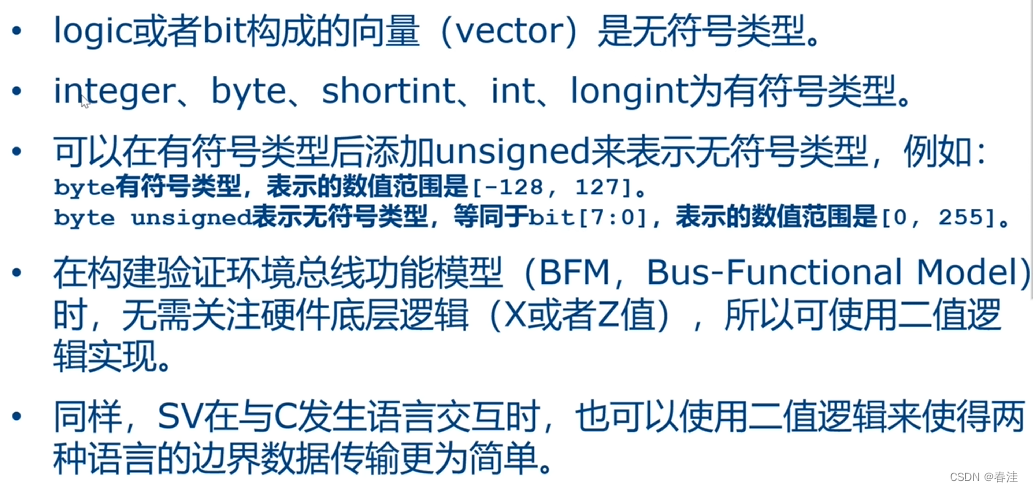

硬件层面的表述电路必须使用四值逻辑

如果用二值逻辑会出现什么事?

无法表述 不上电 或 没有复位 的情况:没有x和z

你可以综合出来它(如果正好不涉及亚稳态/无驱动,那你就综合成功了),但是你可能会出现一点问题:模型失真,也就是亚稳态/无驱动/无复位 情况

二值逻辑一般用在不需要表述硬件电路/会使用抽象级电路的时候-----验证的时候!

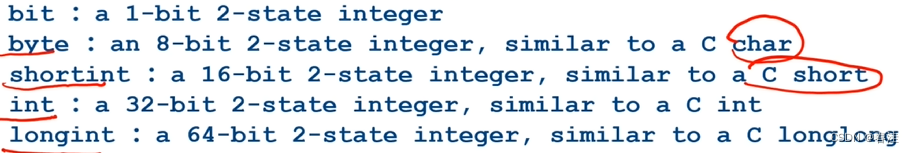

有符号和无符号

有符号数和无符号数之间不可计算,需要转化为同类型

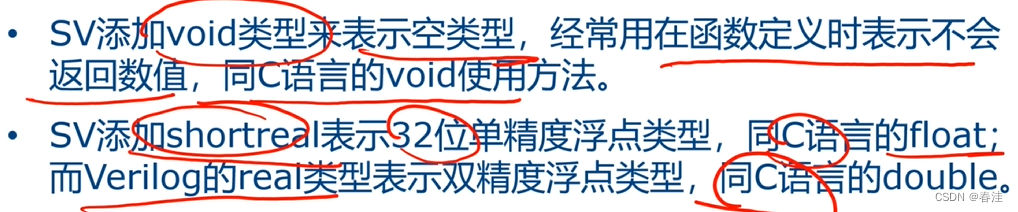

SV中的四值逻辑没有直接与C语言之间做映射

eg:

四值转二值的规则:

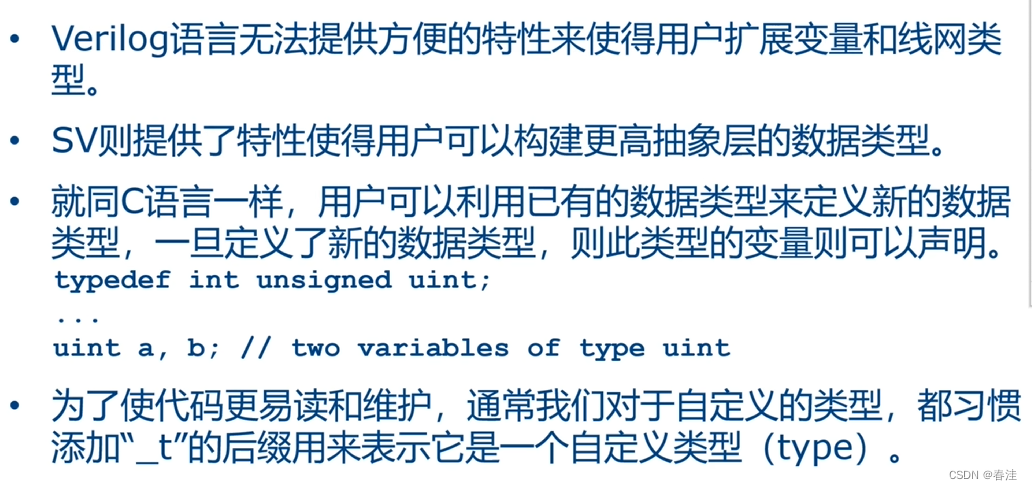

自定义类型

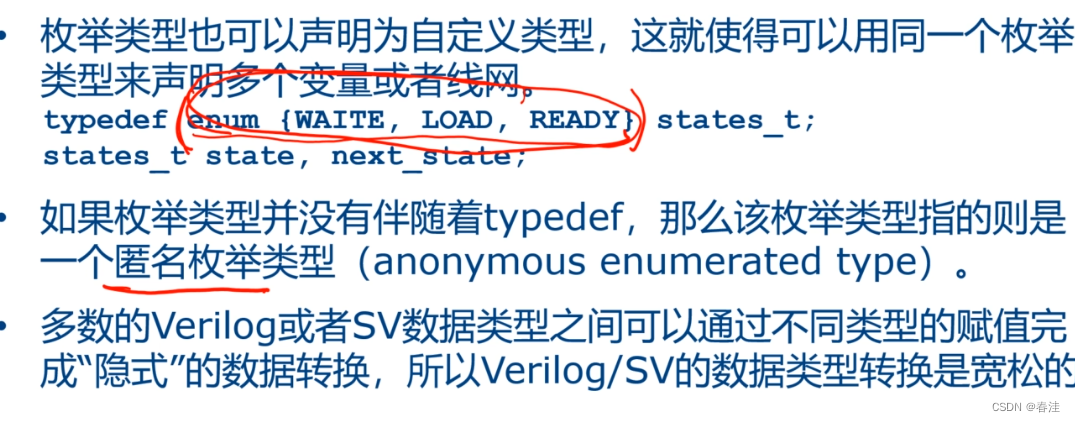

和C相似:typedef

下图中:枚举类型RGB的初始值是red

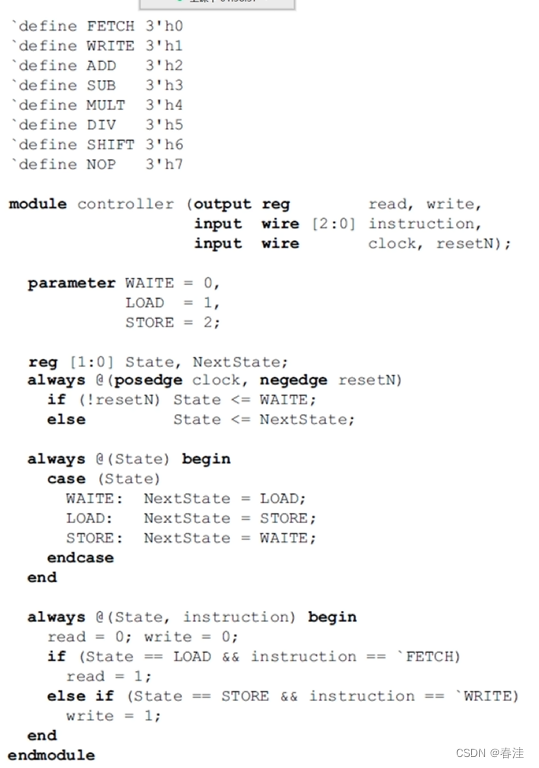

verilog中替代enum的方法:参数化

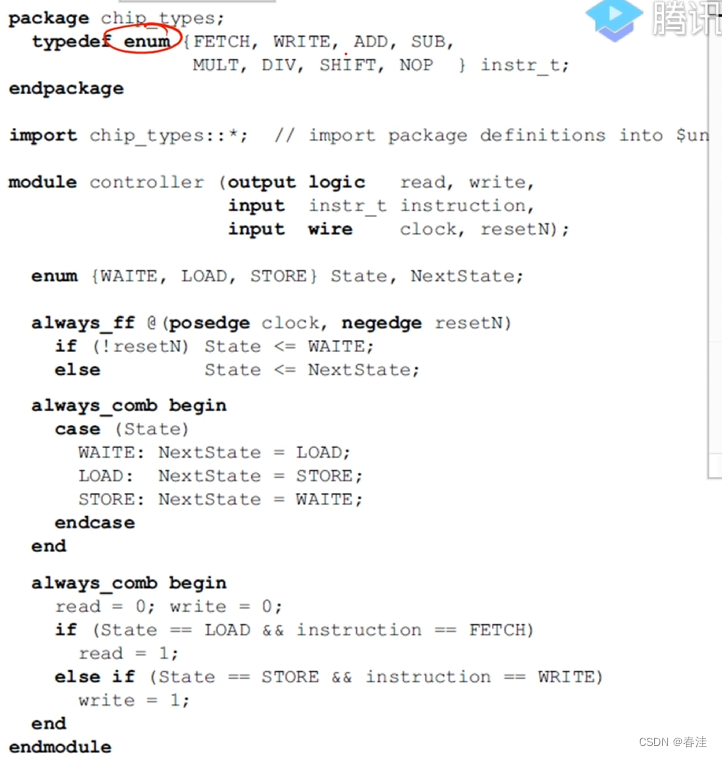

SV中的改动:

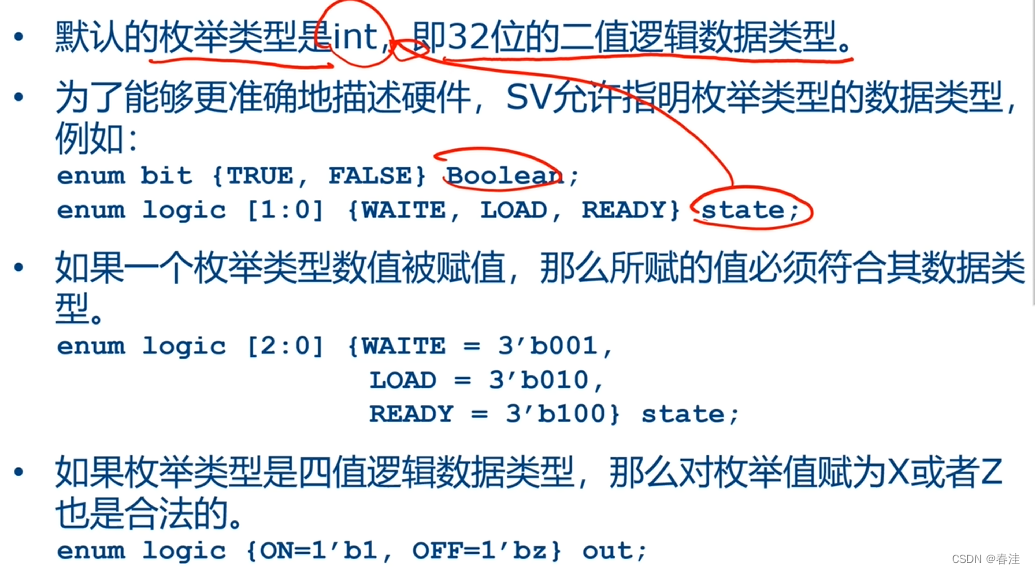

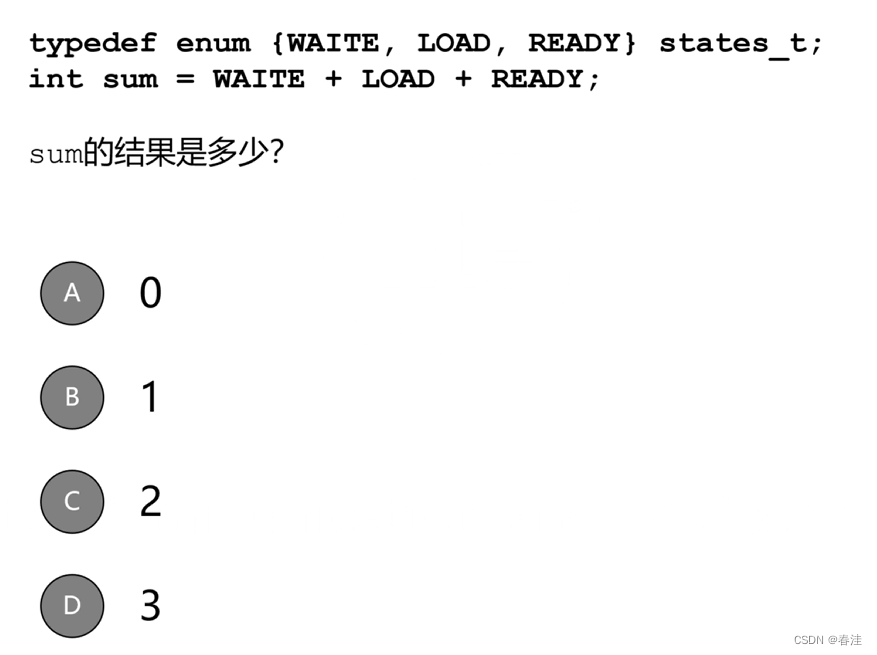

用enum代替了之前的define,这里的enum为缺省类型

下面我们用enum {wr , ld , stro} 例化了两种变量

如果大括号里面后边俩没定义初始值,那就递增处理

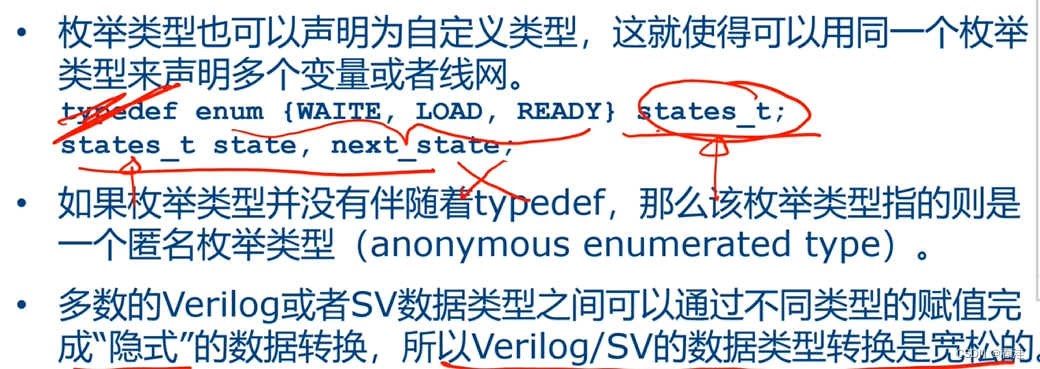

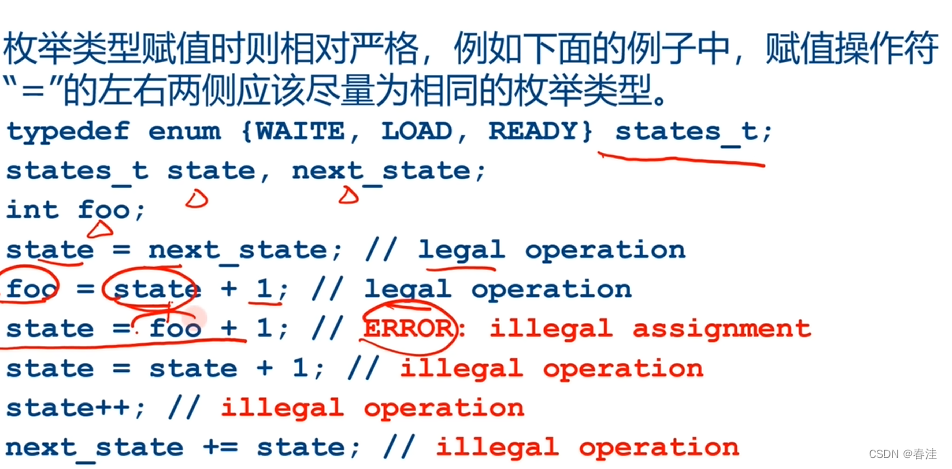

整型不能直接赋值给枚举类型

枚举类型可以隐式地转化为整型,反之不成立

下面第二个error:右边的state因为 + 1 而默认成了整型,但是左侧的state却是枚举类型

选D

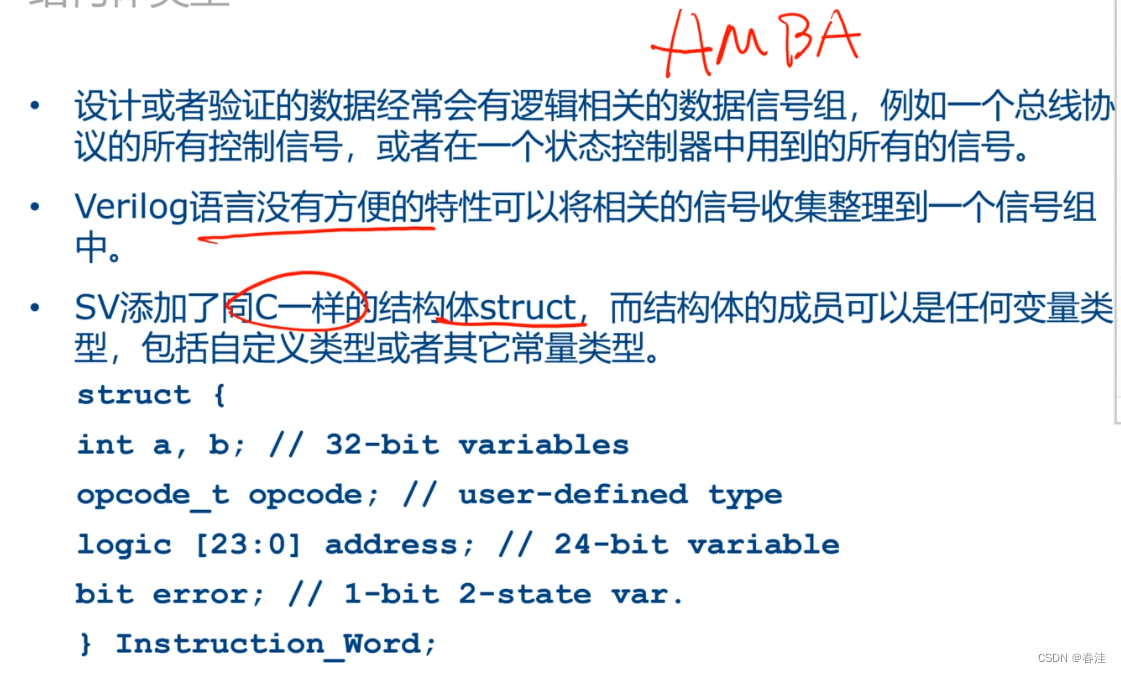

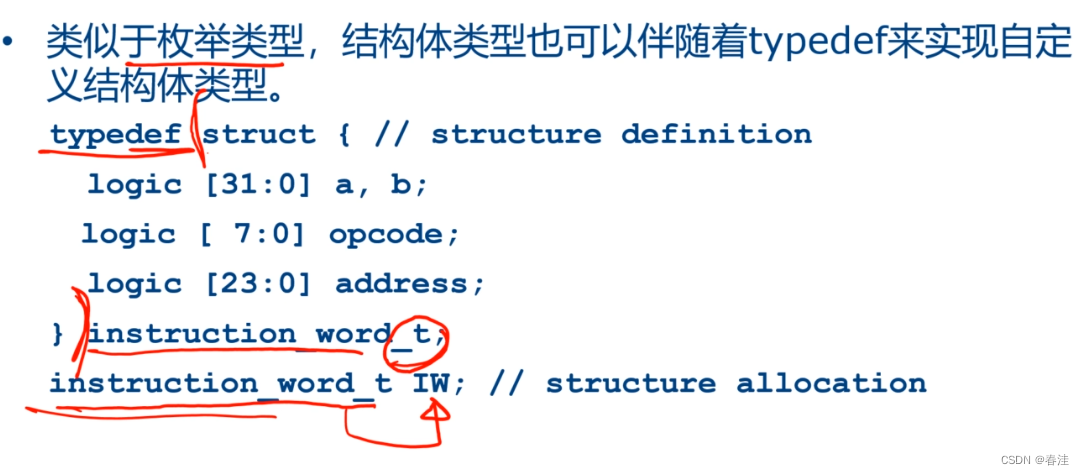

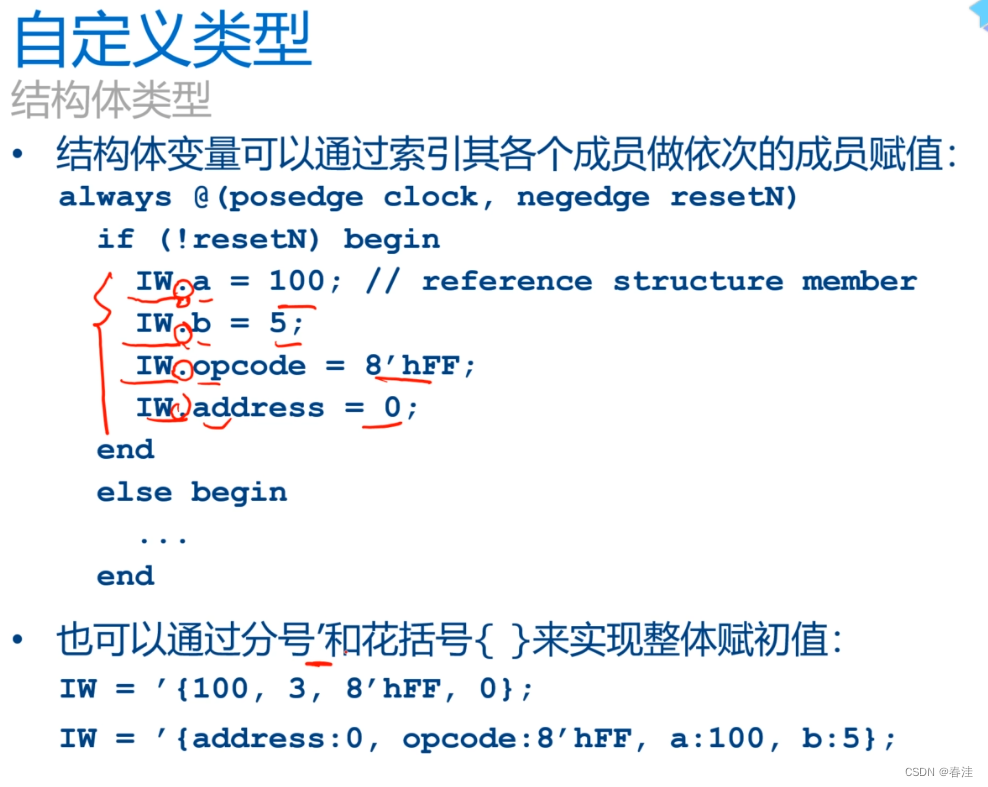

struct不叫类型,struct + {}是类型,且是一个匿名的结构体类型,它的变量叫做Instruction_Word

画圈的是类型

typedef经常和 enum 还有 struct一起出现

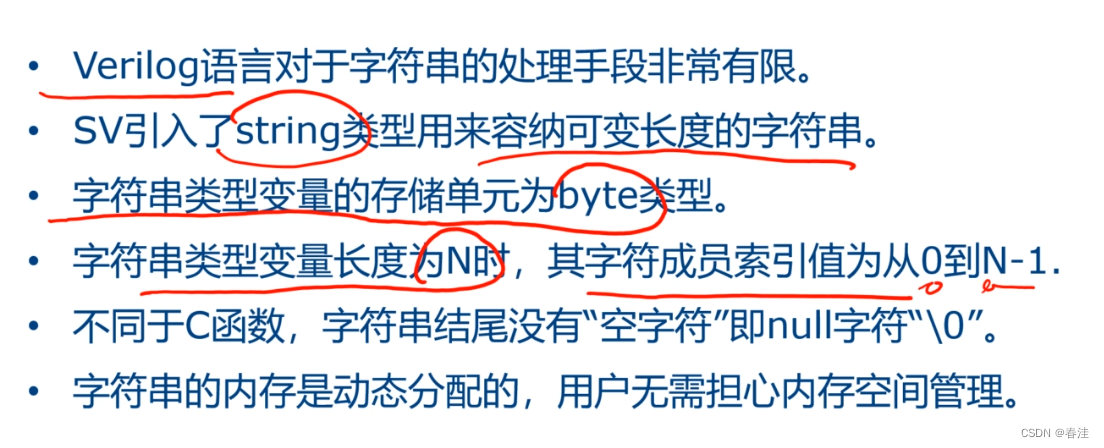

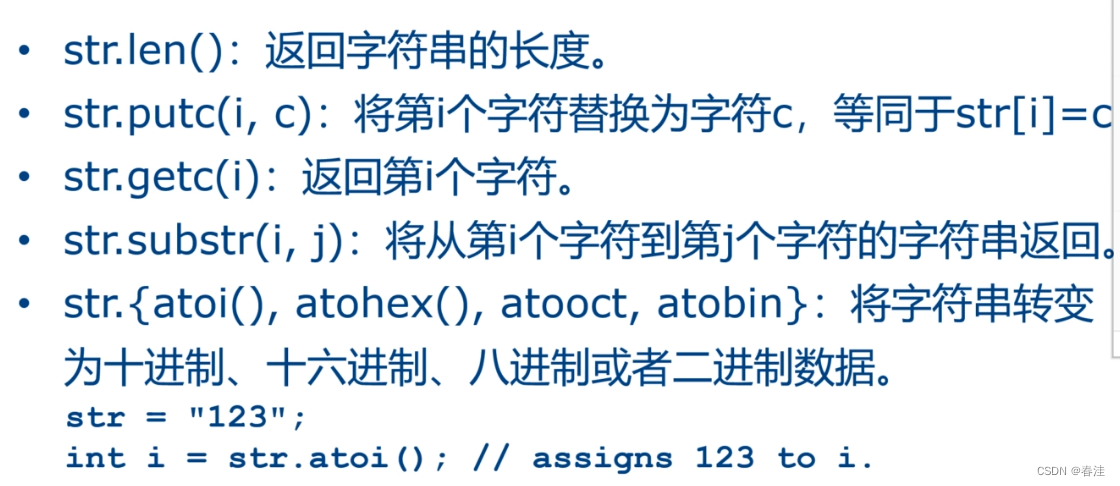

字符串类型

如何判断一个字符串为不为空?

sizeof()(对array类型)

size()

string == ""

string[0]当string为空时结果如何?非法!

V0实验1,2可以看一看

2249

2249

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?