- 施密特触发器电路设计与仿真前介绍

密特触发器可以将非矩形脉冲变成矩形脉冲,这种单元通常有两个稳定状态,从一个状态到另一个状态的转换取决于输入信号的幅度,因此施密特触发器又称为鉴幅器。

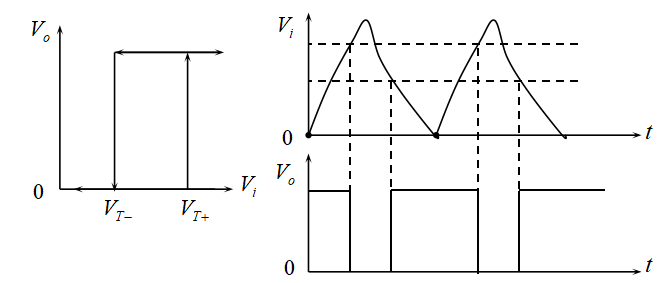

众所周知CMOS反向器和逻辑门都有一个阈值电压VT,当输入电压从低电平上升到VT或从高电平下降到VT时电路的状态将发生变化;而施密特触发器有两个阈值电压,分别称为正向阈值电压VT+和负向阈值电压VT-,在输入信号从低电平上升到高电平的过程中使电路状态发生变化的输入电压称为正向阈值电压,而在输入信号从高电平下降到低电平的过程中使电路状态发生变化的输入电压称为负向阈值电压,正向阈值电压与负向阈值电压之差称为回差电压VH。图1为施密特触发器的电压传输特性,也称为迟滞回线。

图1 施密特触发器的电压传输特性 图2施密特触发器的整形功能

从图1可以看出,当输入信号大于VT+时,输出电压由低电平变为高电平;只有当输入信号小于VT-时,输出电压才由高电平变为低电平,而当输入信号处于VT+和VT-之间时,输出是不变的,即具有记忆功能。由此可见,施密特触发器究其本质而言是一种阈值开关电路,又是一种双稳态多谐振荡器,具有突变的输入/输出特性,这种特性可以广泛应用在阻止当输入电压出现微小变化而引起输出电压改变的场合。具体包括以下几种应用:

1、可以把边沿变化缓慢的周期性信号变换为边沿很陡的矩形脉冲信号,即输入的信号只要幅度大于VT+,即可在施密特触发器的输出端得到同等频率的矩形脉冲信号;

2、当输入电压由低向高增加,到达VT+时,输出电压发生突变,而输入电压Vi由高变低,到达VT-,输出电压发生突变,因而出现输出电压变化滞后的现象,可以看出对于要求一定延迟启动的电路,它是特别适用的;

3、矩形脉冲经传输后经常会发生波形畸变,比如当传输线上的电容较大时,波形的上升沿将明显变缓;而当传输线较长,而且接收端的阻抗与传输线的阻抗不匹配时,在波形的上升沿和下降沿将产生振荡现象;另外当其他脉冲信号通过导线间的分布电容或公共电源线叠加到矩形脉冲信号时,信号上将出现附加的噪声等等,以上这些情形都可以通过用施密特反相触发器整形而得到比较理想的矩形脉冲波形。

二、施密特触发器电路设计与仿真

1.施密特电路设计

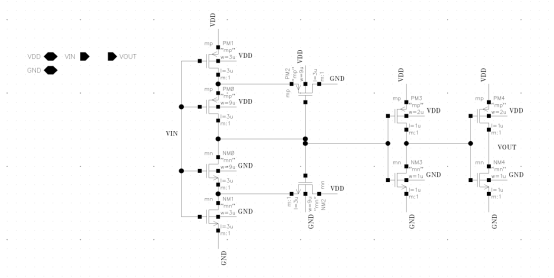

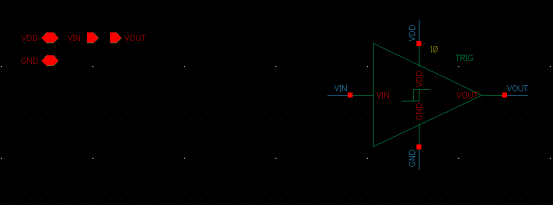

本次设计的施密特触发器,如图3所示。

首先自己的file下新建一个cell名为RIRG的schematic,mp、mp器件均通过快捷键i在st02库中调用。VDD、GND的pin类型为“inputOutput”,VIN为“input”,VOUT为“output”,然后完成下图的电路绘制。(注意:在新建file时候要关联st02工艺库)

图3本次设计的施密特触发器的电路结构

图中施密特触发器后面的输出加上两个反相器起到波形整形作用,另外可以加大输出驱动能力。完成后Check and save,无报错后进入仿真。

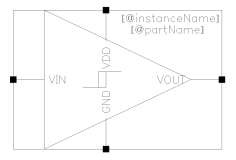

- 施密特电路symbol

通过“Create”中的“Cell view”的From cell view完成图4的symbol

图4本次设计的施密特触发器的symbol

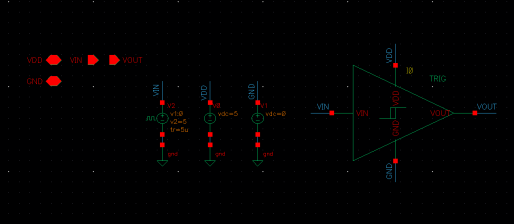

2.仿真准备

1)首先在自己的file下新建一个TRIG_tb用来仿真

2)完成如下图5仿真的搭建

图5 本次设计的施密特触发器的仿真电路

- 激励信号的添加的方法一(VDD和VIN及GND的pin无需添加)

输入信号:分析电路的VIN需要添加一个三角波信号,可通过调用analogLib中的vpulse,设置如图6,周期为1us、延迟时间为1u、上升时间为5us、下降时间为5us、脉冲宽度为0s,通过上述设置其实是将一个用于添加矩形波信号的vpulse,变成一个三角波。

电源信号:可通过调用analogLib中的vdc,设置如图7和8,VDD为直流电5V,GND为0V

图6 VIN信号的设置 图7 VDD信号的设置 图8 GND信号的设置

- 激励信号的添加的方法二

通过ADE中setup Analog stimuli对pin添加激励信号的方式,信号添加如下图9、10、11

图5 本次设计的施密特触发器的仿真电路

图9 VIN信号的设置 图10 VDD信号的设置 图11 GND信号的设置

3.仿真步骤

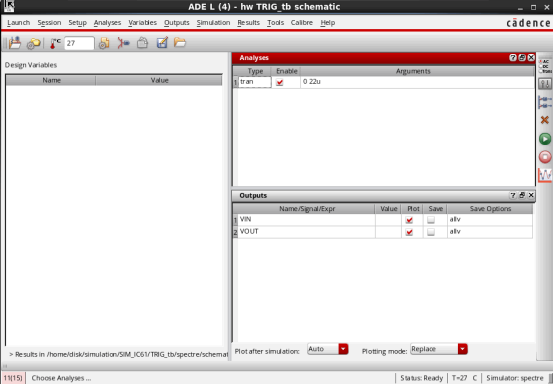

(1)打开仿真工具ADE L

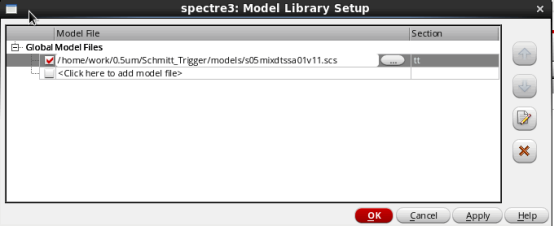

(2)仿真模型文件的选择,点击...在model文件中找到后缀为.scs的文件。

- 仿真类型和时间的确定

瞬态仿真时长为22u

- 输出信号的选择

输入VIN和VOUT

仿真环境设置如图12,右击Analyses的空白处添加信号类型为tran,时长为22u。

图12 仿真环境设置

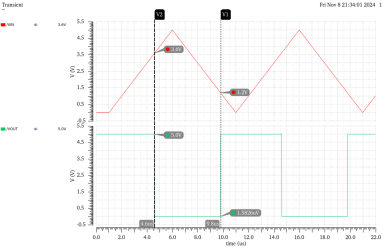

(5)仿真运行和波形分析

在以上准备工作完成后就可以进行仿真了,得到图13所示的仿真结果。

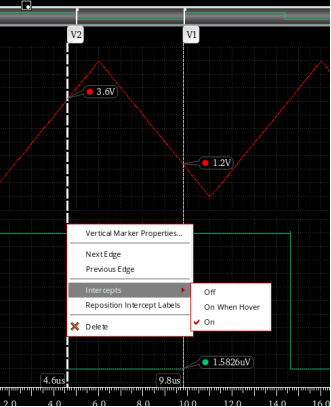

图13 仿真结果

3.仿真结果分析

从图10中发现每次进行跳变的电压值都保持在3.6v和1.2v左右,说明是此触发器的负向阈值电压为3.6v,正向阈值电压为1.2v。当输入信号大于3.6v的时候,输出电压由高电平变为低电平,当输入信号小于1.2v以后输出电压由低电平转换为高电平,完成波形变换的功能。

仿真小技巧,右击V1(V2)选择intercepts 中改为on,这样V1和V2均可显示,如图14所示。

图14 V1和V2均可显示

三、施密特触发器的版图设计与验证

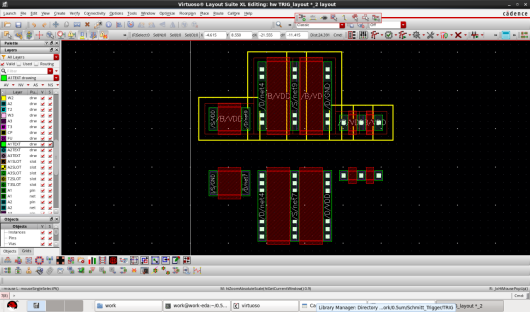

在TRIG电路下通过Layout XL,不要在仿真电路下生成。

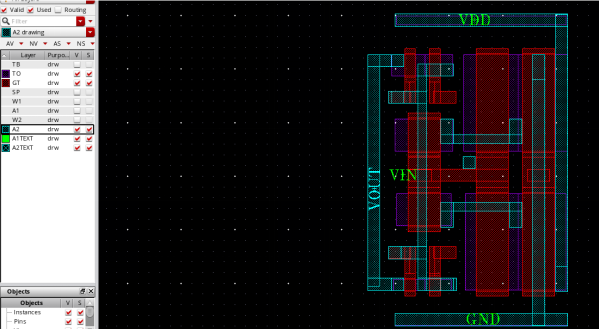

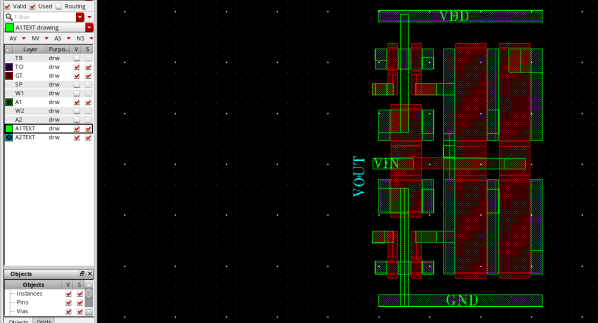

版图布局方式一

首先调用版图,完成如图15所示的布局

图15 版图的布局

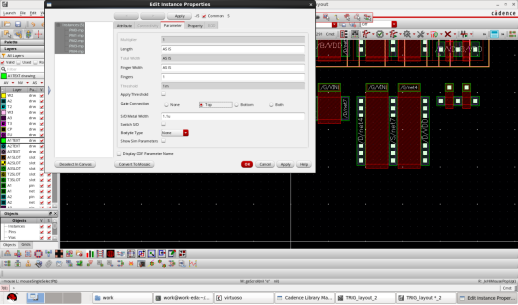

选中PMOS器件,点击“Q”将Gate connection设置为top(自动生成TG到M1层),如16所示

图 16 TG_M1自动生成

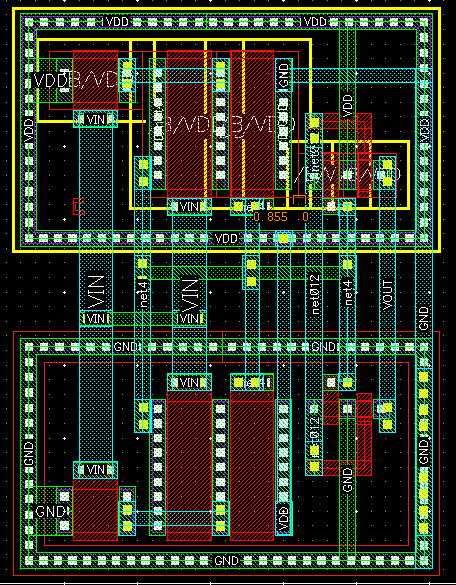

在完成布局后,将PMOS和NMOS放在相应的衬底中,例如:将PMOS在N_ring中。根据EDA软件相同名称的线连接到一起。

图 17 版图布局及连线

完成版图布局之后通过快捷键L,将PIN的名称标上,如图18所示

图18 Label标

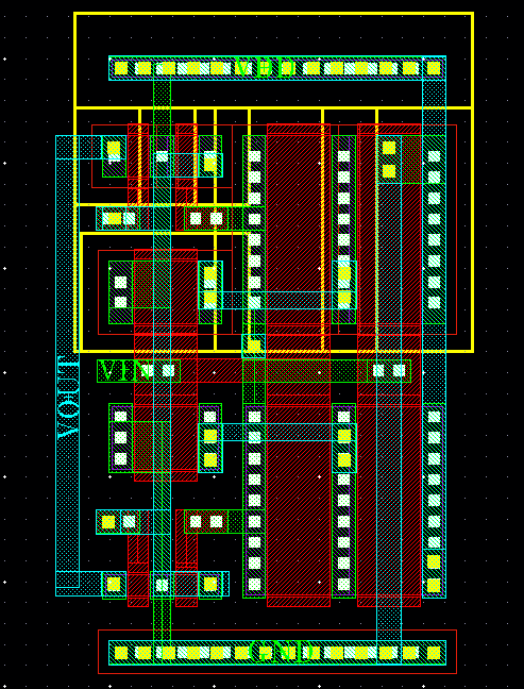

无保护环情况,版图布局方式二(进阶版)

整体版图

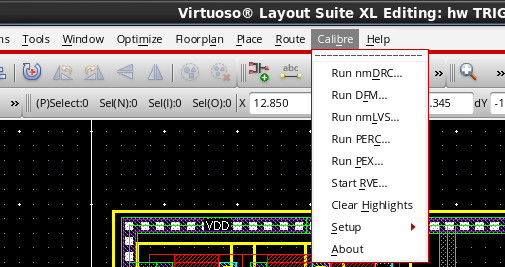

3.2版图验证的LVS和DRC验证

1)打开主栏中的Caliber 中的Run_nmLVS,如图19所示

图19 LVS和DRC的位置

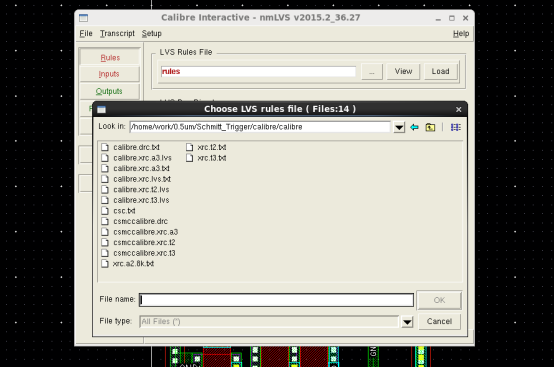

2)点击Rules 添加LVS Rules File 文件,点击三个点找到在caliber文件下后缀名.lvs的文件。

图20 添加LVS Rules File 文件

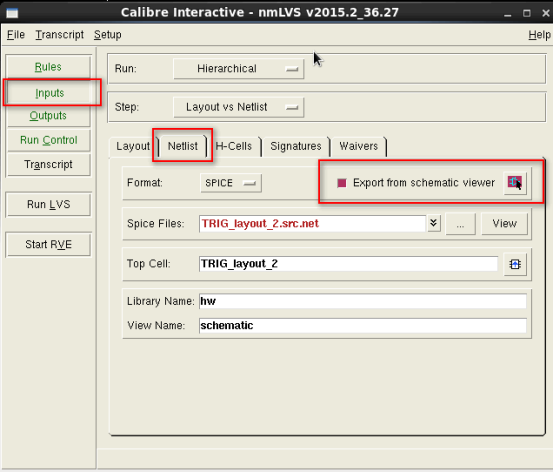

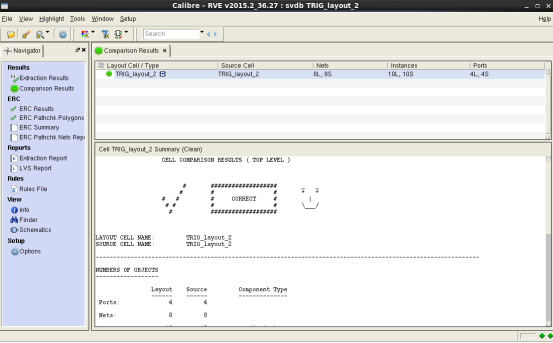

- 添加版图要比对的电路文件,完成后点击“Run Lvs”。结果如图21所示

图21 LVS结果

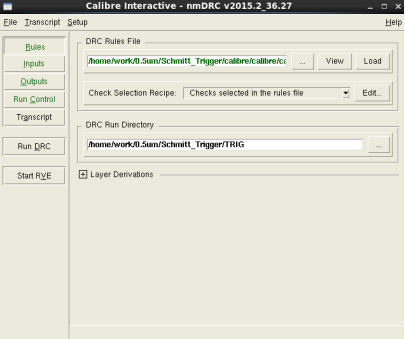

- 同样打开DRC,添加DRC工艺规则文件,如图22所示

图22 DRC工艺规则文件

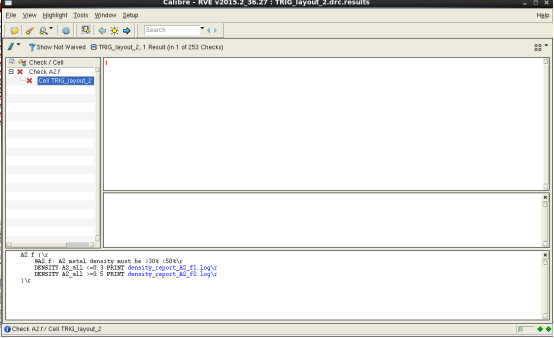

- DRC验证结果,如图23所示,除密度以外无任何报错。

图23 DRC验证结果

7151

7151

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?