DMA原理

DMA全称:直接存储器访问

用于在外设与存储器之间以及存储器与存储器之间提供高速数据传输。可以在无需任何 CPU 操作的情况下通过 DMA 快速移动数据。通过硬件实现。

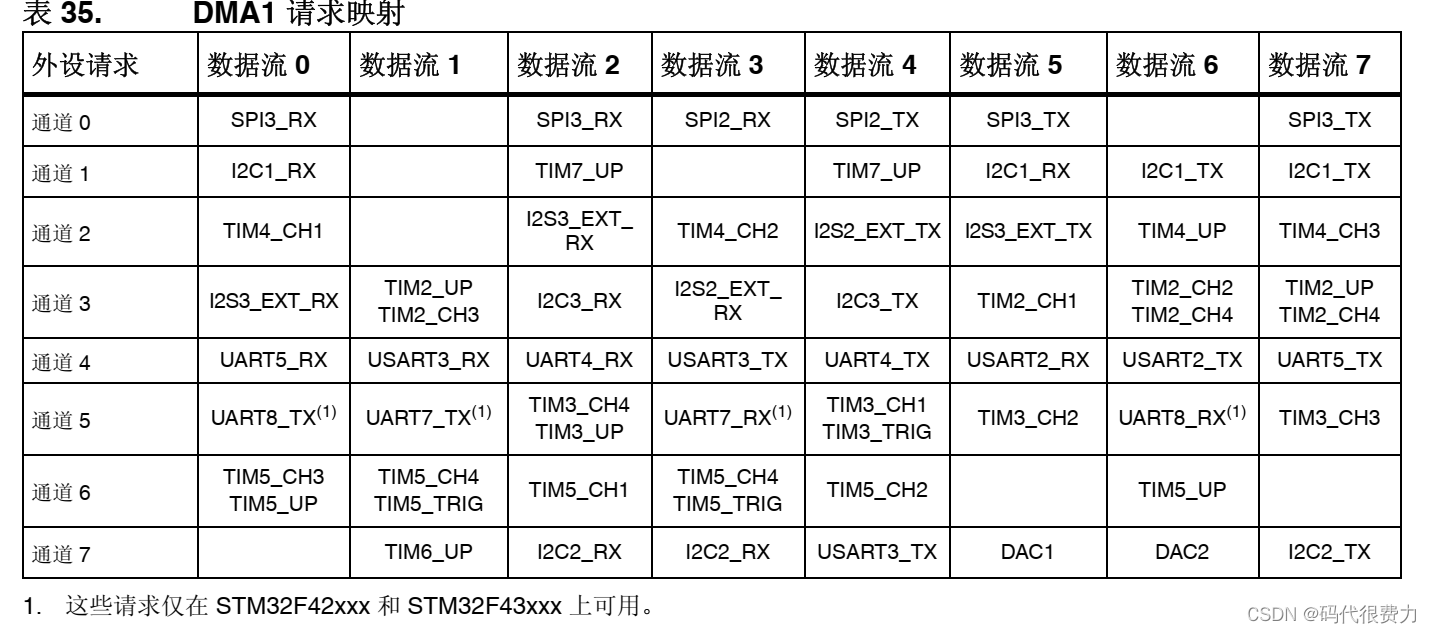

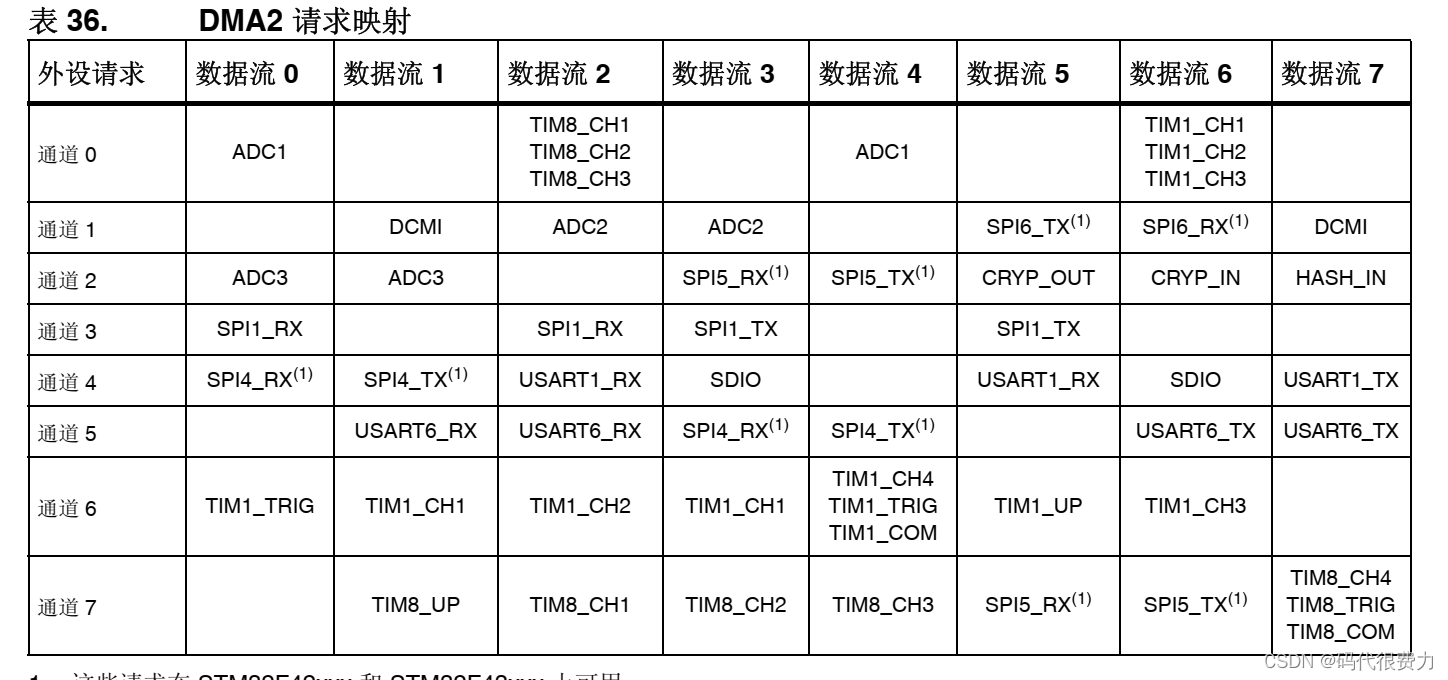

STM32F4最多有2个DMA控制器,两个 DMA 控制器总共有 16 个数据流(每个控制器 8 个),每一个 DMA 控制器都用于管理一个或多个外设的存储器访问请求。每个数据流总共可以有多达 8 个通道(或称请求)。每个通道都有一个仲裁器,用于处理 DMA 请求间的优先级。

DMA主要特性

它可以执行下列事务:

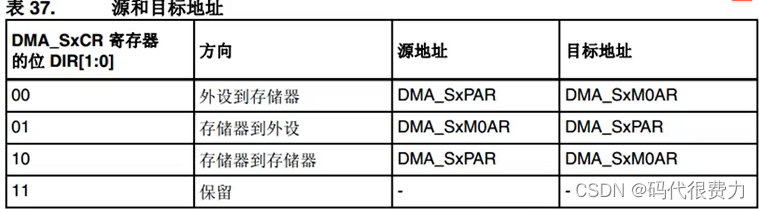

● 外设到存储器的传输

● 存储器到外设的传输

● 存储器到存储器的传输(仅限DMA2控制器,不能使用循环模式和直接模式)

要传输的数据项的数目可以由 DMA 控制器或外设管理:

— DMA 流控制器:要传输的数据项的数目是 1 到 65535,可用软件编程

— 外设流控制器:要传输的数据项的数目未知(无法使用循环模式)并由源或目标外设控制,这些外设通过硬件发出传输结束的信号

DMA每个数据流有两种传输模式:FIFO模式和直接模式

FIFO模式:若源设置为8位(1字节),目标传输宽度32位(4字节),则源需要传输4个字节,而FIFO则是接收源中的字节,当4字节接收满,才会直接传输到目标位置。

直接模式:每个DMA请求会立即启动寄存器对存储器的传输。但如果配置了存储器到外设的传输数据时,DMA会将一个数据从存储器预加载到FIFO内,一旦外设触发DMA请求则会立即传输数据。

● 对源和目标的增量或非增量寻址

● 支持 4 个、 8 个和 16 个节拍的增量突发传输。突发增量的大小可由软件配置,通常等于外设 FIFO 大小的一半

● 每个数据流都支持循环缓冲区管理

● 5 个事件标志( DMA 半传输、 DMA 传输完成、 DMA 传输错误、 DMA FIFO 错误、直接模式错误),进行逻辑或运算,从而产生每个数据流的单个中断请求

DMA通道选择

单次传输和突发传输

单次传输:每个 DMA 请求产生一次字节(8bit)、半字(16bit)或字(32bit)的数据传输。

突发传输:每个 DMA 请求相应地生成 4 个、 8 个或 16 个节拍的字节、半字或字的传输。

“节拍”通常指的是一次突发中的传输次数。在 STM32 中,这由 NBURST[3:0](Number of Burst Beats)参数控制,它决定了一次突发中传输的数据单元数量。如果设置 NBURST = 4,则表示一次突发将连续传输 4 个数据单元。

MBURST[1:0](Memory Burst)参数控制突发次数,若配置为2则表示这种突发将会发送两次

选择突发配置必须要遵守 AHB 协议,即突发传输不得越过 1 KB 地址边界,因为可以分配给单个从设备的最小地址空间是 1 KB。这意味着突发块传输不应越过 1 KB 地址边界,否则就会产生一个 AHB 错误,并且 DMA 寄存器不会报告这个错误。

FIFO

用于在源数据传输到目标之前临时存储这些数据。

每个数据流都有一个独立的 4 字(16字节) FIFO,阈值级别可由软件配置为 1/4、 1/2、 3/4 或满。(若阈值配置为1/2,则FIFO接收到8个字节的数据才会传输)

选择 FIFO 阈值(DMA_SxFCR 寄存器的位 FTH[1:0])和存储器突发大小(DMA_SxCR 寄存器的 MBURST[1:0] 位)时需要小心: FIFO 阈值指向的内容必须与整数个存储器突发传输完全匹配。如果不是这样,当使能数据流时将生成一个 FIFO 错误( DMA_HISR 或 DMA_LISR寄存器的标志 FEIFx),然后将自动禁止数据流。

所有这些情况下,突发大小与数据大小的乘积不得超过 FIFO 大小

DMA事务

DMA 事务由给定数目的数据传输序列组成。要传输的数据项的数目及其宽度( 8 位、 16 位或 32 位)可用软件编程。

循环模式

循环模式开启后,要传输的数据数目 传输完成后,会重新加载继续响应DMA请求。

双缓冲模式

使能双缓冲模式会自动使能循环模式,并在每次事物结束时交换存储器指针

即:目标地址有两处,一处满了,会自动进入第二处

DMA中断

使用时要清除标志位

DMA优先级

DMA数据流有4个优先级(非常高、高、中、低),由软件 控制,在相同的优先级内,数据流编号小的优先级高。

可编程数据宽度、封装/解封、字节库

要传输的数据项数目必须在使能数据流之前编程到 DMA_SxNDTR(要传输数据项数目位,NDT)中,当流控制器是外设且 DMA_SxCR 中的 PFCTRL 位置为 1 时除外。

当使用内部 FIFO 时,源和目标数据的数据宽度可以通过 DMA_SxCR 寄存器的 PSIZE 和MSIZE 位(可以是 8、 16 或32 位)编程。

源和目标数据的宽度尽量一致

仅在使用FIFO的前提下,允许源和目标数据的宽度不一致。

这是个人的一个学习笔记,如果能指错误就再好不过的了。

1237

1237

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?