EMC 整改以 “先定位干扰源与耦合路径,再针对性施策” 为核心,优先低成本、易实施的措施,核心逻辑是 “抑制干扰源、切断耦合路径、保护敏感器件”。

一、整改前核心步骤

- 定位干扰源:通过近场探头、频谱分析仪,锁定高频时钟、开关电源、高速信号线等辐射 / 传导干扰源头。

- 识别耦合路径:判断干扰是通过传导(电源线、信号线)还是辐射(空间、PCB 走线)传播。

- 确认敏感点:找到受干扰的敏感器件(如模拟电路、复位电路)或信号(如小弱信号、时钟信号)。

二、分场景整改关键措施

1. 传导干扰整改(电源线 / 信号线)

- 电源入口加装电源滤波器,需匹配阻抗,涵盖差模 + 共模抑制。

- 信号线串磁环(多绕 2-3 圈)或加装信号滤波器,减少线上传导噪声。

- 采用隔离器件(光耦、隔离变压器),切断不同电路间的传导路径。

2. 辐射干扰整改(PCB / 空间)

- PCB 优化:缩短高频走线、减小回路面积,高频信号紧邻地平面,遵循 3W 规则。

- 屏蔽措施:强辐射模块加屏蔽罩并接地,线缆套金属屏蔽层(两端接地)。

- 滤波辅助:关键信号并高频滤波电容(0.1μF 陶瓷电容),就近接地。

3. 敏感器件 / 信号防护

- 敏感器件远离干扰源(如晶振、开关电源),间距≥25mm。

- 敏感信号走内层(利用地平面屏蔽),或采用差分线传输。

- 复位、模拟信号串联小阻值限流电阻,并联 TVS 管(防静电 / 浪涌)。

4. 接地与屏蔽整改

- 地平面无裂缝,数字地与模拟地单点 / 星形连接,降低接地阻抗。

- 屏蔽机箱缝隙加导电衬垫,孔洞加装金属网 / 波导通风口,避免电磁泄漏。

- PCB 地平面与机箱可靠连接(多点接地),泄放内部干扰电流。

三、整改优先级原则

- 先软件后硬件:调整时钟频率、信号边沿陡峭度(软件优化),成本最低。

- 先布局后布线:优化器件布局(远离干扰源),再调整走线,无需额外成本。

- 先滤波后屏蔽:优先加装电容、磁环、滤波器(低成本易实施),屏蔽作为最后手段(成本较高)。

四、常见失效点整改技巧

- 时钟信号:串 22-100Ω 限流电阻,加屏蔽罩,走线远离板边。

- 开关电源:输出端并联电解电容(滤低频)+ 陶瓷电容(滤高频),外壳接地。

- IO 接口:加装 ESD 防护器件(TVS 管),信号线串磁环,接口处并滤波电容。

P1:电子设备中主要骚扰源

答案:电子设备的主要骚扰源包括:

- 电磁骚扰:时钟信号(高频)、开关电源(快速开关)、数字电路的电平跳变(如 IO 口);

- 传导骚扰:电源线上的纹波、接地不良引入的噪声;

- 辐射骚扰:PCB 走线的天线效应、未屏蔽的高频信号回路;

- 静电放电(ESD):人体 / 设备接触产生的静电脉冲。

P2:怎样减小 DC 模块的骚扰

答案:

- 电源输出端并联滤波电容(如电解电容 + 陶瓷电容,滤除低频 / 高频纹波);

- 模块输入 / 输出端串联磁珠 / 电感,抑制高频噪声传导;

- 模块外壳(若金属)接地,屏蔽辐射;

- 优化模块内部 PCB 布线,缩短高频回路,减小寄生电感 / 电容。

P3:PCB 上的辐射源究竟在哪里

答案:PCB 的辐射源主要是:

- 高频信号走线:如时钟线、高速数据线(等效为 “微天线”,辐射电磁场);

- 未接地的导体:悬空的铜箔、未端接的走线(易产生天线效应);

- 电流回路:大电流 / 高频电流的回路(如电源回路),形成磁场辐射;

- 接口电路:IO 口、电源接口的未屏蔽走线,向外辐射噪声。

P4:怎样控制 PCB 板的电磁辐射

答案:

- 布线优化:缩短高频走线、减小回路面积、走差分线(抵消辐射);

- 接地设计:铺地平面(减小接地阻抗)、数字 / 模拟地分开后单点连接;

- 滤波措施:关键信号串磁珠、电源 / IO 口并滤波电容;

- 屏蔽处理:对高频区域做局部屏蔽罩并接地;

- 端接匹配:高速信号(如时钟)做阻抗匹配,避免反射噪声。

P5:多层线路板是解决电磁兼容问题的简单方法

答案:是(相对简单有效)。原因:

- 多层板可单独铺电源 / 地平面,减小回路阻抗,抑制辐射;

- 信号层与地平面紧邻,可降低走线的天线效应;

- 数字、模拟电路可分层布局,减少跨区域干扰;

- 电源层与地层形成的电容,可辅助滤除电源噪声。

P6:怎样处理地线的裂缝

答案:地线裂缝(地平面断开)会增大接地阻抗、形成辐射回路,处理方法:

- 若为设计失误,补焊跨接导线(连接裂缝两侧的地平面);

- 若无法补焊,在裂缝附近增加接地过孔,减小地阻抗;

- 后续设计避免地平面分割,必须分割时用宽走线 / 敷铜带连接分割区域。

P7:怎样降低时钟信号的辐射

答案:

- 采用差分时钟(如 LVDS),两根线的辐射相互抵消;

- 时钟线紧邻地平面,缩短走线长度,减小回路面积;

- 时钟源(晶振)加屏蔽罩并接地;

- 时钟信号串限流电阻 / 磁珠,降低信号边沿陡峭度(减小高频谐波);

- 时钟线做阻抗匹配,避免反射产生的噪声辐射。

P8:为什么 IO 接口的处理特别重要

答案:IO 接口是设备与外部连接的通道,易成为干扰的 “出入口”:

- IO 口的信号(如串口、USB)易向外辐射噪声,或从外部引入干扰;

- IO 线通常较长,等效为天线,辐射 / 接收能力强;

- IO 口若未做防护(如 ESD、滤波),易导致设备抗扰度不足,甚至损坏芯片。

P9:屏蔽机箱在电磁兼容中扮演的角色

答案:屏蔽机箱的核心角色是隔离内外电磁骚扰:

- 阻止内部的电磁辐射向外泄漏;

- 阻挡外部的电磁干扰进入设备内部;

- 为内部电路提供 “低阻抗接地参考”,辅助抑制辐射;

- 若机箱接地良好,还可泄放静电(ESD),保护内部电路。

P10:用金属制作的机箱就是屏蔽箱吗?

答案:不一定。金属机箱需满足屏蔽条件才是有效屏蔽箱:

- 机箱需是连续的导电体(无过大缝隙、孔洞),否则电磁信号会从缝隙 / 孔洞泄漏;

- 机箱的导电性能良好(如铜、铝),且厚度足够(至少大于骚扰信号波长的 1/100);

- 机箱需可靠接地,否则无法有效泄放干扰电流。

P11:金属材料的屏蔽效果与什么有关?

答案:金属屏蔽效果主要与以下因素有关:

- 材料类型:导电率 / 磁导率越高(如铜、铝、钢),屏蔽效果越好;

- 材料厚度:厚度越大,对电磁波的衰减越强(需大于波长的 1/100);

- 频率:低频(磁场)依赖磁导率(如钢),高频(电场)依赖导电率(如铜);

- 结构完整性:缝隙、孔洞越小 / 越少,屏蔽效果越好。

P12:孔洞的泄漏与什么因素有关?

答案:孔洞的电磁泄漏主要与以下因素有关:

- 孔洞尺寸:尺寸越接近骚扰信号的波长(或 1/2 波长),泄漏越严重;

- 孔洞数量:多个孔洞的泄漏效果是叠加的,数量越多泄漏越强;

- 频率:高频信号更容易从孔洞泄漏(波长更短,易匹配孔洞尺寸);

- 孔洞形状:长条形缝隙的泄漏比圆形孔洞更严重(等效为 “缝隙天线”)。

P13:怎样解决缝隙的泄漏

答案:解决缝隙泄漏的方法:

- 缝隙处加装导电衬垫(如导电橡胶、金属簧片),填充缝隙并保持导电连续性;

- 减小缝隙宽度,或用金属胶带 / 导电胶密封缝隙;

- 缝隙处增加接地连接点(如螺丝间距≤波长的 1/20),降低缝隙的天线效应;

- 关键区域的缝隙采用焊接密封(永久连接)。

P14:机箱上的孔洞怎样处理

答案:处理机箱孔洞的方法:

- 孔洞尺寸小于骚扰信号波长的 1/20(高频场景需更小);

- 孔洞处加装金属网 / 屏蔽罩(网孔尺寸远小于波长);

- 用导电材料填充非必要孔洞;

- 若为散热孔,采用波导通风口(只允许空气通过,阻挡电磁波)。

P15:怎样解决贯通导体泄漏的问题

答案:贯通导体(如电缆、导线穿过机箱)易泄漏电磁信号,处理方法:

- 导体穿过机箱处加装滤波连接器 / 馈通滤波器,滤除导体上的高频噪声;

- 导体在机箱内的部分屏蔽并接地(如套金属波纹管,两端接地);

- 采用光纤传输(非导体,无电磁泄漏)替代电信号传输;

- 贯通导体尽量短且少,必要时做信号隔离(如光耦)。

P16:怎样评价屏蔽机箱的效能

答案:通过屏蔽效能(SE) 评价,单位为分贝(dB),公式:\(\text{SE} = 20\lg\frac{E_{\text{外}}}{E_{\text{内}}}\)(电场)或 \(20\lg\frac{H_{\text{外}}}{H_{\text{内}}}\)(磁场),测试方法:

- 辐射法:外部施加已知强度的电磁信号,测量机箱内部的信号强度,计算衰减量;

- 传导法:通过贯通导体注入噪声,测量机箱内外的噪声衰减;

- 标准测试:依据 GB/T 12190、IEC 61000 等标准,在暗室中测试不同频率下的屏蔽效能。

P17:PCB 的接地对机箱泄漏有什么影响?

答案:PCB 接地是机箱屏蔽效能的关键支撑,影响如下:

- 若 PCB 接地不良(如地阻抗高),内部电磁噪声会通过 PCB 与机箱的缝隙 / 孔洞泄漏;

- PCB 地平面与机箱可靠连接(多点接地),可将内部噪声泄放到机箱,避免向外部辐射;

- 若 PCB 地与机箱存在电位差,会形成 “接地回路”,反而通过机箱缝隙向外辐射噪声。

P18:为什么电源线的处理特别重要?

答案:电源线是电磁骚扰的 “主要传导 / 辐射通道”,原因:

- 电源线既会将设备内部的噪声传导到电网(骚扰其他设备),也会从电网引入外部干扰;

- 电源线通常较长,等效为 “高效天线”,易将内部噪声辐射出去,或接收外部辐射干扰;

- 开关电源等模块的高频噪声,易通过电源线向外传播,是电磁兼容测试(如传导、辐射)的高频失效点。

P19:怎样知道电源线导致的辐射发射会不会超标?

答案:通过电磁兼容测试验证:

- 依据标准(如 GB/T 17626、IEC 61000),在电波暗室中测试电源线的辐射发射(如 30MHz~1GHz 频段);

- 若无条件测试,可通过预测试工具(如近场探头)扫描电源线,若近场信号强度远高于标准限值(如 Class B 限值),则大概率超标;

- 对比同类合格产品的电源线辐射数据,辅助预判。

P20:怎样处理电源线的 EMC?

答案:核心是 “抑制传导 + 屏蔽辐射”:

- 在电源入口处加装电源滤波器(含差模 / 共模电感、电容),滤除线上的高频噪声;

- 电源线外层套金属屏蔽层(如编织网),并将屏蔽层两端可靠接地;

- 缩短电源线长度,或采用波纹金属管包裹电源线,减小天线效应;

- 电源线上串磁环(多绕几圈),抑制共模辐射。

P21:怎样测量滤波器的插入损耗?

答案:插入损耗(IL)是滤波器对噪声的衰减能力,测量方法(依据 GB/T 7343):

- 搭建测试系统:信号源→测试夹具(含滤波器)→频谱分析仪 / 网络分析仪;

- 先测 “无滤波器时” 的信号传输增益 \(G_1\);

- 接入滤波器后,测 “有滤波器时” 的信号传输增益 \(G_2\);

- 计算插入损耗:\(\text{IL} = 20\lg\frac{G_1}{G_2}\)(单位:dB),需覆盖滤波器的工作频率范围。

P22:测量差模插入损耗的注意事项?

答案:差模是线对线的噪声,测量需避免共模干扰:

- 测试夹具需采用平衡传输结构(如差分探头、平衡线缆),模拟差模信号路径;

- 确保测试系统的接地参考一致,避免引入共模噪声;

- 信号源输出纯差模信号(避免信号不平衡),可通过平衡变压器产生差模信号;

- 重复测量多次,取平均值,减少测试误差。

P23:测量共模插入损耗的注意事项?

答案:共模是线对地的噪声,测量需隔离差模信号:

- 测试夹具需采用共模注入结构(如通过共模变压器,将信号注入线 - 地之间);

- 确保测试系统的地线阻抗低且统一(如采用接地平板),避免地线干扰;

- 抑制差模信号的影响,可在测试回路中加入差模扼流圈;

- 测试时远离其他接地导体,避免共模信号被分流。

P24:怎样选择一个合适的滤波器?

答案:按 “干扰类型 + 频率 + 电气参数” 选择:

- 明确干扰类型:是差模干扰(选差模电感 + X 电容)还是共模干扰(选共模电感 + Y 电容);

- 匹配干扰频率:滤波器的截止频率需覆盖干扰的主要频段;

- 满足电气参数:额定电压、电流需大于实际工作值,阻抗需与电源 / 负载匹配;

- 考虑安装形式:如 PCB 插装、线缆式、面板式,需适配设备结构;

- 参考 EMC 标准:选择通过对应标准(如 CE、FCC)认证的滤波器。

P25:按照厂家给的插损指标选择滤波器肯定可以通过试验吗?

答案:不一定。原因:

- 厂家插损指标是理想测试条件下的结果(如匹配负载、标准测试夹具),实际设备的负载 / 布线环境与理想条件存在差异;

- 实际干扰可能包含滤波器未覆盖的频段,或干扰强度超过滤波器的衰减能力;

- 设备内部的其他干扰源(如 PCB 辐射)可能同时存在,仅靠滤波器无法完全解决问题。→ 需结合实际测试验证,必要时调整滤波器参数或补充其他 EMC 措施。

P26:在普通的环境中能进行 CE102 的摸底吗?

答案:很难。CE102 是电源线传导发射测试(频段 10kHz~10MHz),对测试环境要求高:

- 普通环境存在背景噪声(如电网噪声、其他设备干扰),会掩盖电源线的真实发射信号;

- 测试需要屏蔽室 + LISN(线路阻抗稳定网络),普通环境无法提供稳定的测试阻抗和无干扰的背景;→ 若要摸底,需在尽可能远离干扰源的环境中,使用 LISN + 频谱分析仪,且测试结果仅作参考,最终需在标准实验室验证。

差模与共模的核心知识点

-

规律与可预测性

- 差模电流:受基尔霍夫定律支配,规律明确、易预测;

- 共模电流:无明确规律,本身不易预测。

-

电流的产生与转换

- 共模电流由差模电流衍生产生;

- 共模电流可反向转换为差模电流,进而干扰电路功能。

-

辐射特性(差模)若两个导体形成的回路面积很小,差模电流的辐射会因电流相互抵消而减弱。

-

辐射贡献占比PCB 及连接电缆的共模辐射,是电磁辐射发射的主要来源(比差模辐射贡献更大)。

-

辐射效率(共模 vs 差模)共模电流的辐射效率远高于差模电流:

- 例:50MHz 频率下,10cm² 回路的 20mA 差模电流,在 10m 处场强为 42dB μV/m;

- 而 1m 长电缆仅需 20μA 共模电流(差模电流的 1/1000),即可产生同等场强。

单板中的敏感器件 / 信号知识点

单板中易受电磁干扰影响的敏感器件或信号主要包括:

- 锁相环电路:对相位、频率稳定性要求高,易受噪声干扰;

- WIFI 模块:高频无线通信模块,对电磁辐射 / 接收敏感;

- 模拟信号:电压 / 电流幅度较小,抗干扰能力弱;

- 复位信号:逻辑电平敏感,干扰易导致设备异常复位;

- 小弱信号:信号幅度极低,外部干扰易掩盖有效信号;

- 时钟电路:高频且是系统时序基准,干扰会导致时序紊乱。

EMC 对策(切断 / 减少耦合的方法)知识点

EMC 中切断或减少干扰耦合路径的核心方法,分为传导耦合和辐射耦合两类,基础手段是 “接地、屏蔽、滤波”:

-

针对传导耦合的方法通过抑制干扰的传导路径,常用措施:

- 加装滤波电容、滤波器;

- 使用共模线圈(抑制共模干扰);

- 采用隔离变压器(隔离电路间的传导干扰)。

-

针对辐射耦合的方法通过削弱电磁辐射的传播 / 接收,常用措施:

- PCB 布线:相邻层垂直走线(减少层间耦合)、遵循 3W 规则(走线间距≥3 倍线宽,减少串扰);

- 接地 / 屏蔽:增加屏蔽地线、辐射 / 敏感信号布在内层(利用地层屏蔽);

- 布局 / 线缆:磁性器件合理布局、辐射强信号远离板边 / 缝隙、使用 9/10 双绞线(抵消辐射)。

-

EMC 基础手段整体 EMC 防护的核心三类措施:接地、屏蔽、滤波(上述方法均围绕这三类展开)。

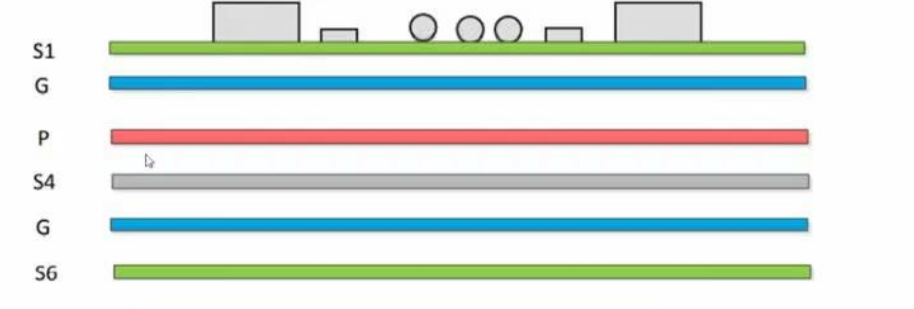

多层板 EMC 叠层的一般原则知识点

多层 PCB 板为提升 EMC 性能,叠层需遵循以下原则:

- 元件面与地平面相邻:元件面(信号层)紧邻地平面,利用地平面实现屏蔽,并提供连续的信号参考平面;

- 信号层尽量与地平面相邻:所有信号层优先与地平面配对,减少信号辐射与串扰;

- 避免信号层直接相邻:防止两层信号直接耦合,降低串扰风险;

- 电源层与对应地平面相邻:主电源层与对应的地平面紧邻,利用层间电容滤波,同时减小电源回路阻抗;

- 兼顾层压结构:控制 PCB 翘曲度(≤0.75%),保证结构稳定性;

- 采用偶数层结构:适配制造工艺,平衡成本、层压难度与翘曲度。

PCB 布局一般原则知识点

PCB 布局需遵循以下核心原则,以保障电路功能与 EMC 性能:

- 按信号流向与功能分区:参照原理功能框图,依据信号传输方向布局,将各功能模块电路分区放置;

- 敏感 / 干扰模块分开布局:同一 PCB 上,数字电路与模拟电路、高速电路与低速电路、干扰源与敏感电路需分开布置,避免相互干扰;

- 焊接面避放敏感 / 强辐射器件:单板焊接面(如背面)避免放置敏感器件或强辐射器件,减少焊接 / 操作对器件的影响;

- 最小化敏感 / 强辐射信号的回路面积:敏感信号、强辐射信号的电流回路面积需尽可能小,降低辐射与串扰风险;

- 强辐射 / 敏感器件远离板边 / 接口:晶体、晶振、继电器、开关电源等强辐射 / 敏感器件,需远离板拉手条、对外接口连接器,推荐距离≥1000mil(约 25.4mm)。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?