一、SOI MOSFET的结构设计,满足以下几点要求:

- n沟道SOI MOSFET

- 沟道长度45 nm

- 多晶硅栅

- 栅氧化层/硅界面电荷密度

cm3

- (选做)判断所生成的SOIMOSFET是否是全耗尽SOI,如果不是,请调整为全耗尽型。

go atlas simflags="-p 8"

mesh space.mult=1.0

mesh space.mult=1.0

x.mesh loc=0.00 spac=0.005

x.mesh loc=0.035 spac=0.005

x.mesh loc=0.08 spac=0.001

#近漏端网格加密,考虑非理想因素

x.mesh loc=0.09 spac=0.001

x.mesh loc=0.10 spac=0.005

x.mesh loc=0.115 spac=0.005

y.mesh loc=0.00 spac=0.005

#沟道处网格加密

y.mesh loc=0.015 spac=0.005

y.mesh loc=0.02 spac=0.005

y.mesh loc=0.025 spac=0.001

y.mesh loc=0.06 spac=0.005

y.mesh loc=0.1 spac=0.005

#

region num=1 y.min=0 silicon

#

region num=2 x.min=0 y.min=0 y.max=0.025 material=SiO2

#

region number=3 x.min=0.035 x.max=0.08 y.min=0 y.max=0.02 material=Poly

#

region num=4 x.min=0 y.min=0.05 y.max=0.06 material=SiO2

#

region number=5 x.min=0.035 x.max=0.080 y.min=0 y.max=0.015 material=aluminum

#

region number=6 x.min=0.005 x.max=0.025 y.min=0 y.max=0.025 material=aluminum

#

region number=7 x.min=0.090 x.max=0.110 y.min=0 y.max=0.025 material=aluminum

#定义电极

elect reg=5 name=gate

#x.min=0.035 length=0.045 y.min=-0.005 y.max=-0.005

elect num=2 name=source x.min=0.005 x.max=0.025 y.min=0 y.max=0.025

elect num=3 name=drain x.min=0.090 x.max=0.110 y.min=0 y.max=0.025

electrode bottom name=substrate

doping uniform region=1 p.type conc=2e18

#doping uniform region=1 x.min=0 x.max=0.115 y.min=0.070 y.max=0.100 p.type conc=2e13

doping uniform region=1 x.min=0.005 x.max=0.035 y.min=0.025 y.max=0.040 n.type conc=1e22

doping uniform region=1 x.min=0.080 x.max=0.110 y.min=0.025 y.max=0.040 n.type conc=1e22

save outf = mosfet.str

#tonyplot mosex.str

开头go atlas simflags="-p 8"定义cpu8核运行atlas,默认是一核

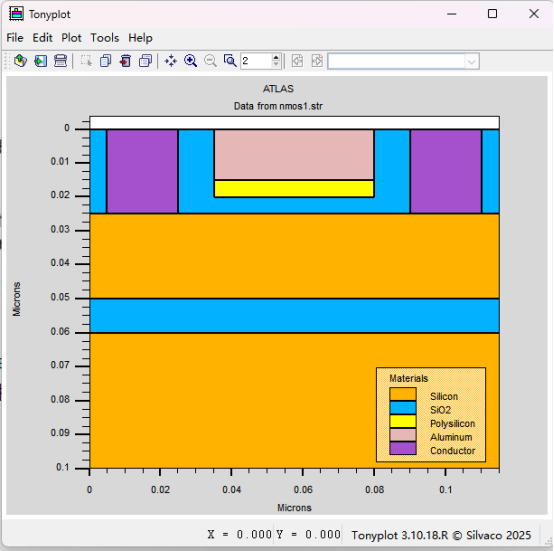

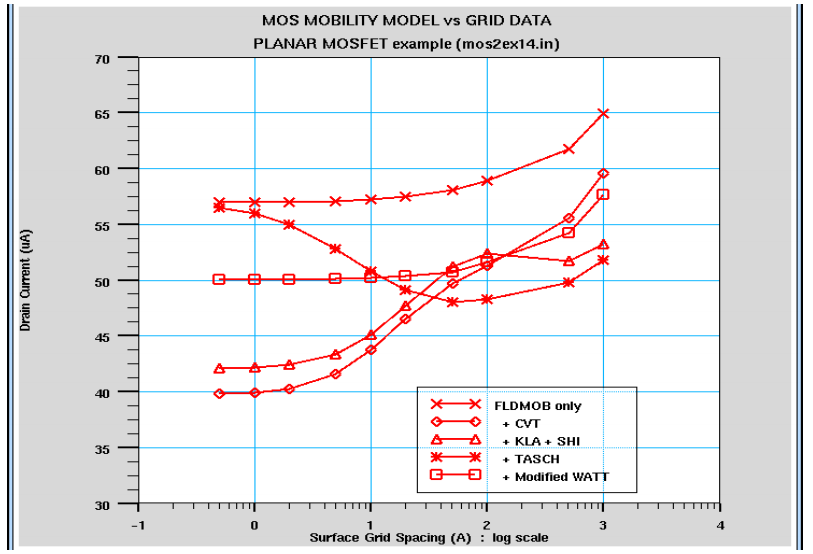

网格定义;①在沟道y=0.025处进行了适当网格加密②y坐标在0.02和0.015处多定义了两处,因为这两处是下文多晶硅和铝的region的边界

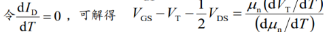

在MOS器件的模拟中,加密网格的关键区域包括:

①栅极下方通道处的垂直网格间距非常小。所需的网格大小取决于所选的横向场或表面迁移率模型。

②深亚微米器件中沟长调制、GIDL等效应明显。为了精确获得漏端耗尽区、电场等参数的变化,确定沟道的夹断点等等,我认为还需要加密漏端和沟道结合处的横向纵向网格。

atlas用户手册里面SOImos的部分还建议mesh在栅氧化层下方和埋氧化层上方都进行加密,对于FDSOI只有栅氧化层下方形成导电沟道所以加密栅氧化层表面就好了。

region定义;atlas后定义的region会自动覆盖之前的region,所以先定义大的region再定义小的

定义电极;点击定义可以直接指定整块region,也可以定义xy的矩形区域,gate是用前面铝的region定义的,方便后边修改沟道长度

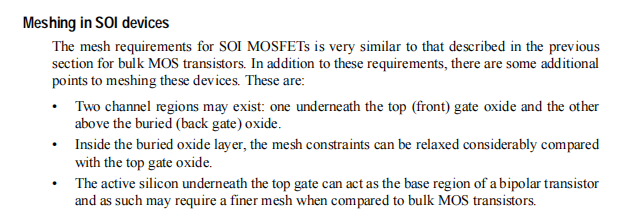

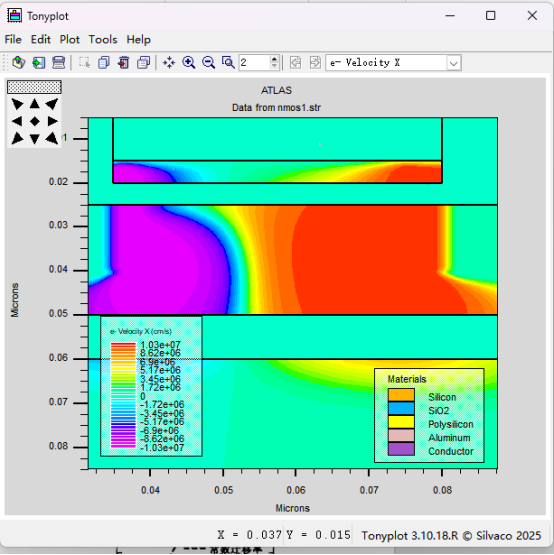

运行上面代码得到·下面的器件结构

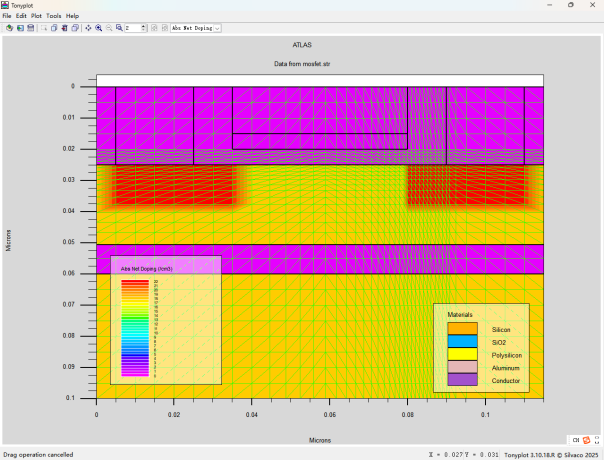

这时候可以加几行solve init,给能够让mos工作在线性区或者饱和区的VD和VG,输出该VD和VG电压下面的str文件,tonyplot-contuors里可以看到工作在线性区时候沟道电子浓度。

看到整个SO2埋层上方电子浓度都在cm-3以上,这就算是FDSOI了

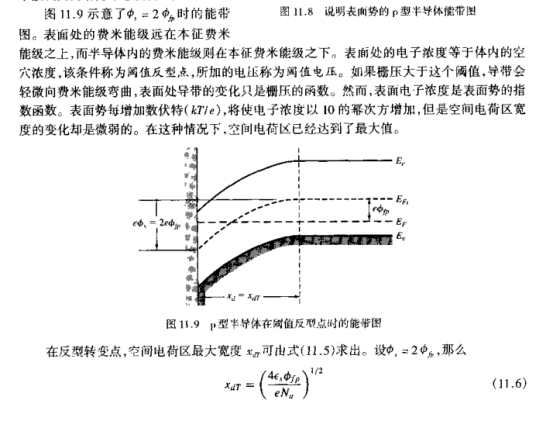

如果一开始耗尽区没有展宽到下面的sio2埋层,可以通过调整p衬底掺杂浓度调整耗尽区宽度。对于低频信号,只要VG>VTH沟道反型层形成,耗尽区宽度就一直保持在最大值xd

Faifp的影响几乎忽略,从公式可以看到减小NA可以增大xd。

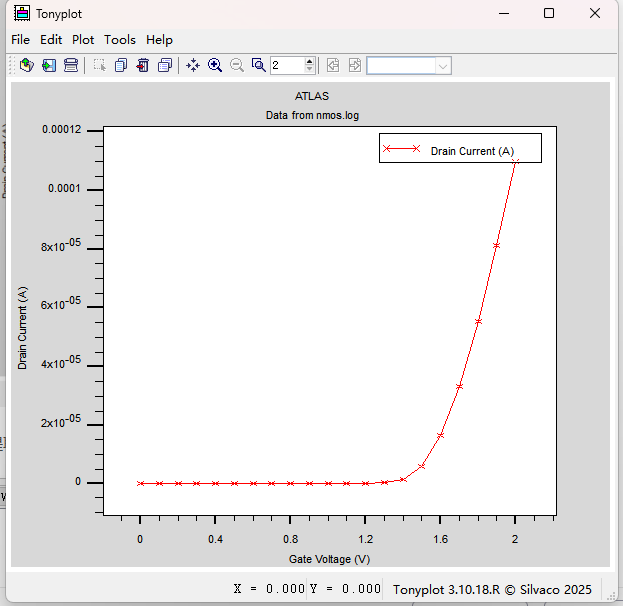

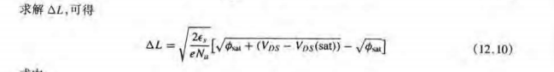

二、仿真转移特性曲线

转移特性曲线是ID随VG的变化曲线

model mos

#model kla shi auger hcte.el print temperature=300

#界面电荷 SiO2 和 Si 的接触是不理想的,存在界面态,固定的界面电荷,譬如悬挂键和可动离子

interface qf=1e11

method newton

#method gummel newton

#求解初始状态

solve init

solve vdrain=0.5

#存储结果

log outf=nmos.log

#设置栅压起始栅压为0 伏最终栅压为1.5伏研究转移特性

solve vgate=0 vstep=0.1 vfinal=1.5 name=gate

output ex.velocity

save outf=nmos.str

log off

#开启电压提取:

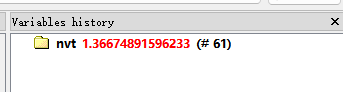

extract name="nvt"(xintercept(maxslope(curve(abs(v."gate"),abs(i."drain"))))- abs(ave(v."drain"))/2.0)

tonyplot nmos.log

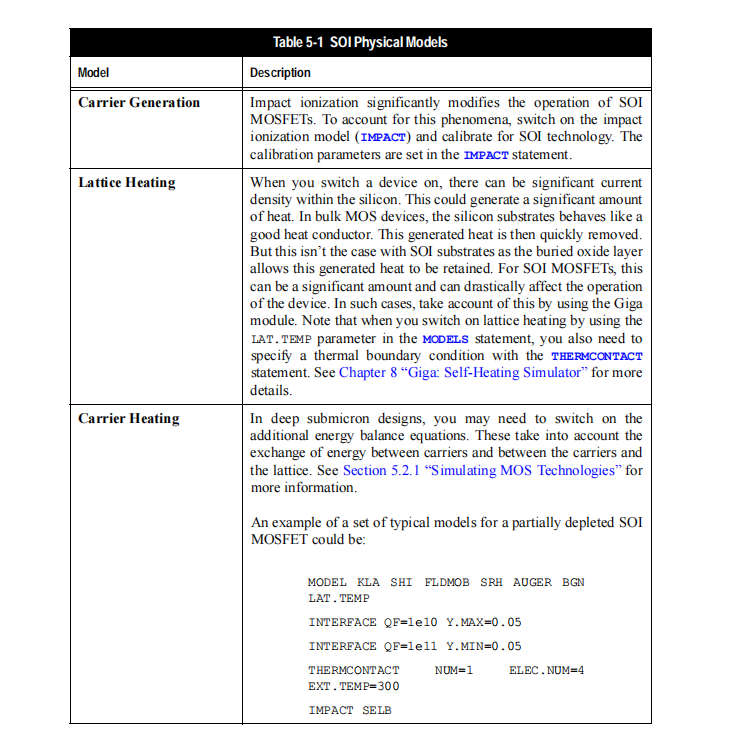

#quit定义物理模型:model mos

这是atlas自带的mos模型。

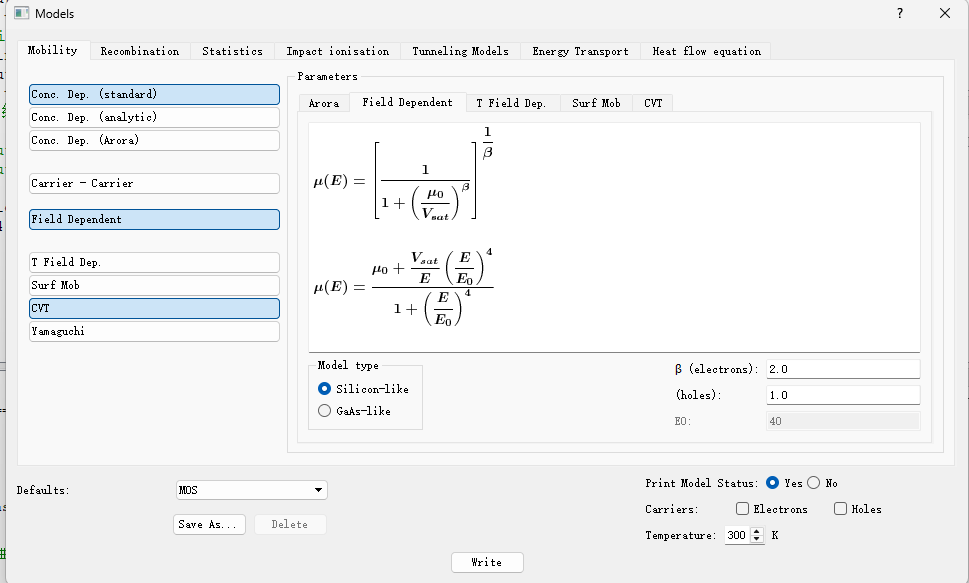

S-Pisces提供了专门用于模拟MOS设备的物理模型。大多数这些模型都可以通过models语句调用。通过指定MOS参数,可以启用一组默认的物理模型,这些模型对于MOS模拟特别有用。MOS参数支持Shockley-Read-Hall(SRH)、Fermi统计(FERMI)和Lombardi位移率模型(CVT),这些模型适用于横向场依赖性。要设置默认的MOS模拟模型,可以使用:model MOS PRINT。横向场依赖的位移率模型对于模拟MOS设备尤为重要。S-Pisces目前支持几种不同的横向场依赖位移率模型。CVT参数选择Lombardi CVT模型。YAMA参数选择Yamaguchi模型。TASCH参数选择TASCH模型。WATT参数选择WATT表面模型,该模型在Mobility语句中使用额外的MOD参数时,可以以更精确的方式运行。您会发现,Mobility语句可以用来修改各种模型的某些参数,将不同的模型应用于不同的区域,或将不同的模型应用于电子。

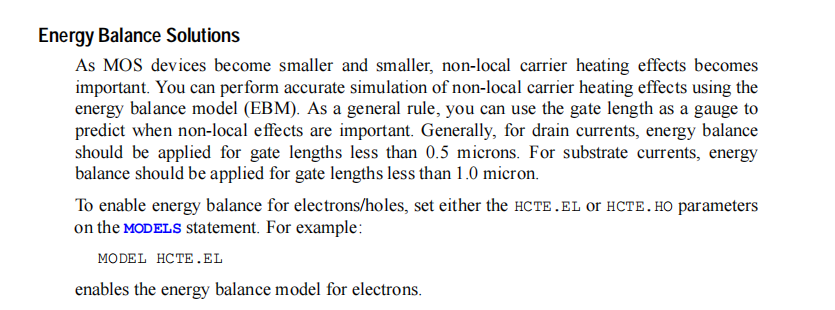

随着MOS设备尺寸的不断缩小,非局部载流子加热效应变得越来越重要。可以使用能量平衡模型(EBM)来准确模拟这种效应。通常,可以通过栅极长度来预测何时非局部效应变得显著。对于漏电流,当栅极长度小于0.5微米时,应应用能量平衡。对于衬底电流,当栅极长度小于1.0微米时,也应应用能量平衡。为了启用电子或空穴的能量平衡,可以在MODELS语句中设置HCTE.EL或HCTE.HO参数。例如:model HCTE.EL为电子启用能量平衡模型。

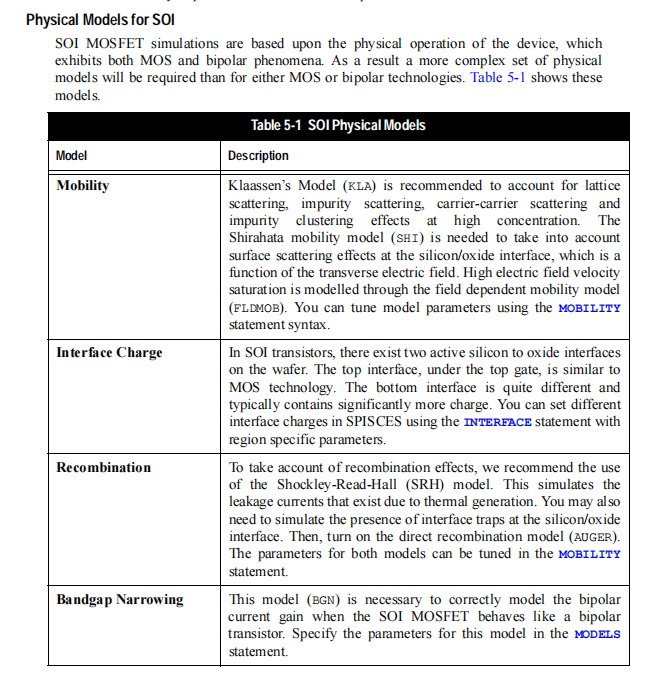

atlas用户手册5.2节里有关于SOI器件仿真的介绍,里面给出了几种SOImos跟体mos相比可能需要的模型。

Klaassen模型(KLA)用于考虑晶格散射、杂质散射、载流子-载流子散射以及高浓度下的杂质聚集效应。Shirahata电迁移率模型(SHI)用于考虑硅/氧化物界面处的表面散射效应,该效应与横向电场有关。高电场速度饱和通过场依赖电迁移率模型(FLDMOB)进行建模。

在SOI晶体管中,晶圆上存在两个活性硅与氧化物的界面。位于顶栅下方的上界面类似于MOS技术。而下界面则大不相同,通常含有更多的电荷。您可以通过使用带有区域特定参数的interface语句,在SPISCES中设置不同的界面电荷。

为了考虑复合效应,我们建议使用Shockley-Read-Hall(SRH)模型。该模型可以模拟由热生成引起的泄漏电流。此外,还需模拟硅/氧化物界面处的陷阱。然后,开启俄歇复合模型(AUGER)。这两个模型的参数可以在MOBILITY语句中进行调整。

当SOI MOSFET表现得像双极晶体管时,此模型(BGN)对于正确建模双极电流增益是必要的。请在MODELS语句中指定此模型的参数。

冲击电离显著改变了SOI MOSFET的工作方式。为了解释这一现象,开启冲击电离模型(IMPACT),并针对SOI技术进行校准。校准参数在Impact语句中设置。

当你开启设备时,硅内部可能会产生显著的电流密度,这会导致大量热量的产生。在体MOS器件中,硅基板作为良好的热导体,能够迅速将这些热量散出。然而,在SOI基板中,由于埋入的氧化层,产生的热量难以有效散发。对于SOI MOSFET而言,这种热量积累可能非常显著,严重影响设备的正常运行。在这种情况下,建议使用Giga模块来处理这一问题。需要注意的是,当你通过MODELS语句中的LAT.TEMP参数开启晶格加热时,还需要使用THERMCONTACT语句指定热边界条件。更多详情,请参阅第8章“Giga:自热模拟器”。

在深亚微米设计中,可能需要打开附加的能量平衡方程。这些方程考虑了载流子之间以及载流子与晶格之间的能量交换。有关更多信息,请参见第5.2.1节“模拟MOS技术”。

上述物理模型和数值方案应该使S-Pisces能够研究所有重要的SOI现象,包括耗尽效应或部分耗尽。

数值求解:采用GUNMEL-NEWTON方法

SOI器件模拟中的一个重要问题是数值方法的选择。在SOI技术中,通道(或体)区域的电位通常被称为“浮动”。这是因为该区域没有与任何电极直接接触。因此,当在接触点施加或增加偏压时,可能会出现收敛问题。这是因为数值解算方案中用于( ,n,p)的初始猜测可能不准确,特别是在“浮动”区域。如果使用碰撞电离模型,这种情况尤为明显。为了克服初始猜测不准确的问题,在等温漂移-扩散模拟中可以采用以下数值方法:GUMMEL-NEWTON方法。该方法首先进行GUMMEL迭代,以获得NEWTON解算方案的改进初始猜测。尽管这种方法更为稳健,但其速度比单独使用NEWTON方案要慢。有关可用数值方案的更多信息,请参阅atlas手册第21章:“数值技术”。

,n,p)的初始猜测可能不准确,特别是在“浮动”区域。如果使用碰撞电离模型,这种情况尤为明显。为了克服初始猜测不准确的问题,在等温漂移-扩散模拟中可以采用以下数值方法:GUMMEL-NEWTON方法。该方法首先进行GUMMEL迭代,以获得NEWTON解算方案的改进初始猜测。尽管这种方法更为稳健,但其速度比单独使用NEWTON方案要慢。有关可用数值方案的更多信息,请参阅atlas手册第21章:“数值技术”。

定义界面电荷:interface qf=1e11

在漏极电压VD=0.5下解VG,从0解到1.5,这里注意VD不能给太大,保证VD在0~VG-VTH的范围内,不然VD>VG-VTH,看不到导通特性

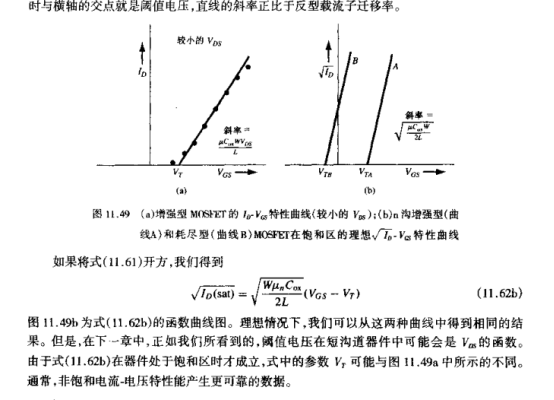

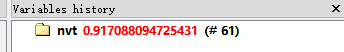

EXTRACT提取阈值电压:这里是用提取曲线中斜率最大处电压值的方法,作为阈值电压。后面仿真发现这种方法提取阈值电压的值可能会随着解VG的区间和步进有小范围的波动。

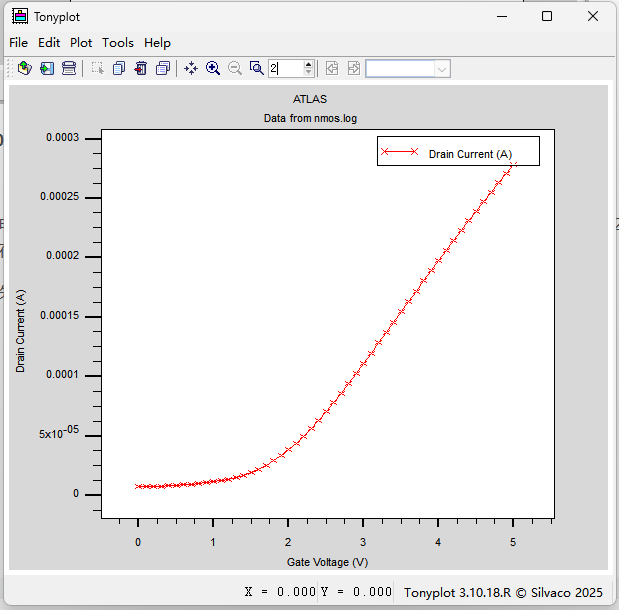

得到的转移特性曲线是这样的

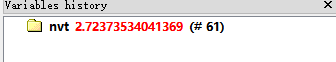

提取的阈值电压(可能不是上面这段代码的截图因为截图太多了这个代码的结果找不到了)

提取到的阈值电压是正值,所以器件是增强型。

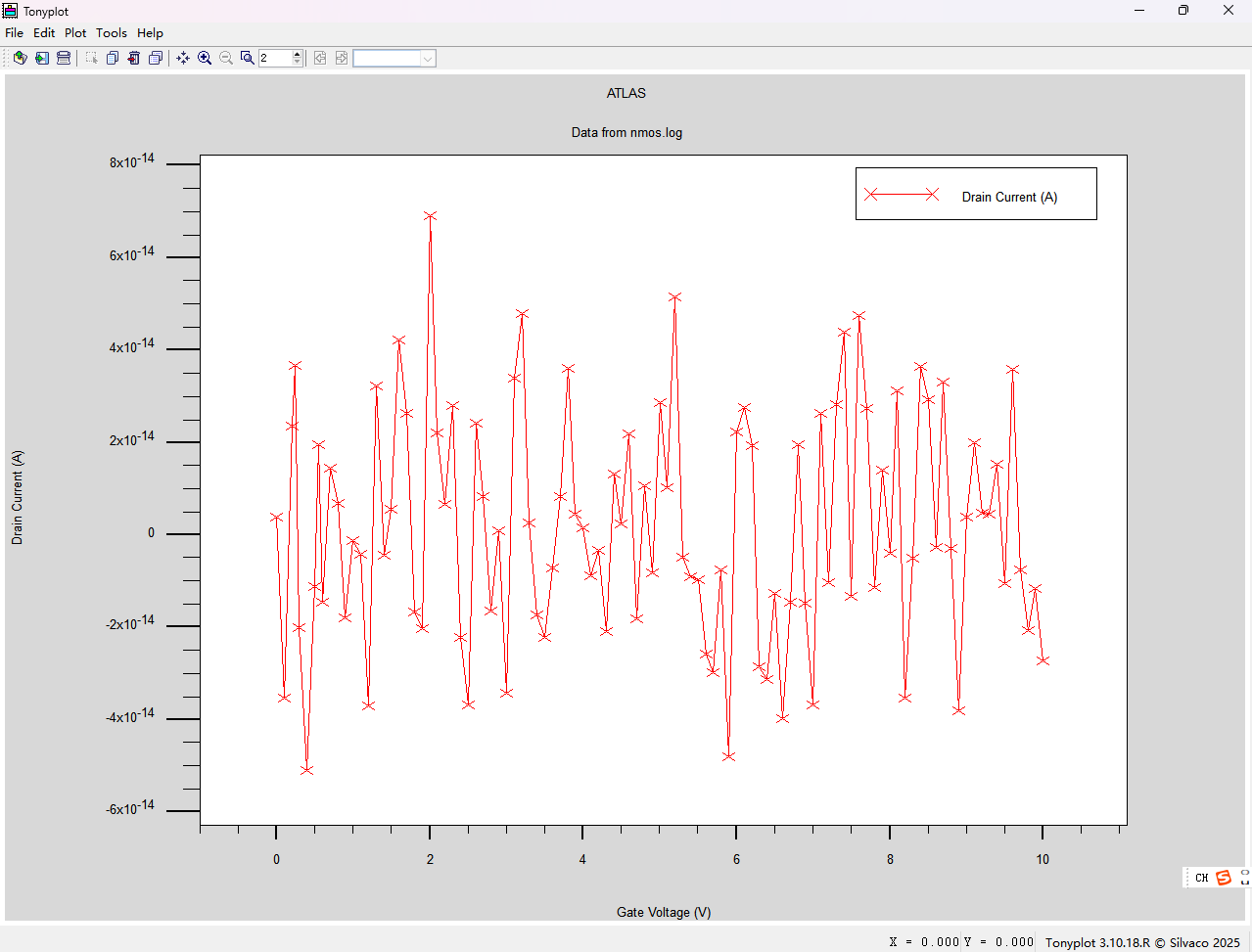

如果NA掺杂浓度调的很大,S之间D可能会不导通,ID乱跳像下面一样,可能有两个原因

①是VTH会随着NA增大,如果下面solve施加的栅极电压 VG 未同步提高,可能无法达到新的阈值电压,导致沟道无法形成。

②如果扩大了VD解得范围还是这样,说明不是阈值电压太大的原因,这时候适当降低VD就可以仿真出来正常曲线,但是原因还没有找到。可能是因为漏极空间电荷区有关?

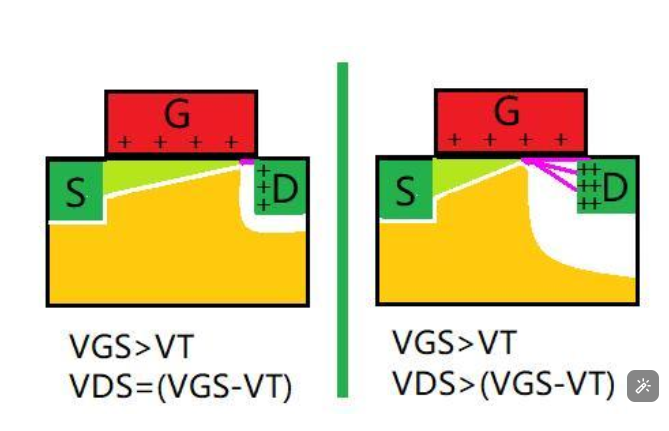

工作在饱和区的mos,即使沟道夹断,依然能够导电,是因为随着靠近漏极的沟道越来越细,很多高速的电子冲过来,一部分挤过夹断点进入漏端空间电荷区,然后被漏极正电场高速收集(形成示意图中紫色电流)。所以可能是因为VD太高漏端空间电荷区太宽的原因?

5.24这里是仿真收敛性的问题,具体可以看一下软件下面跑的过程。

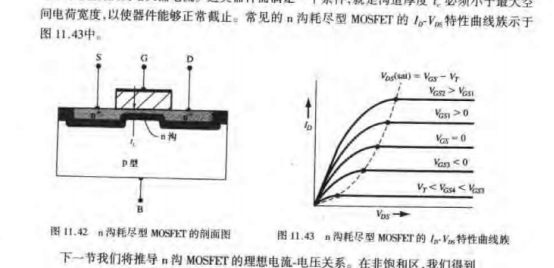

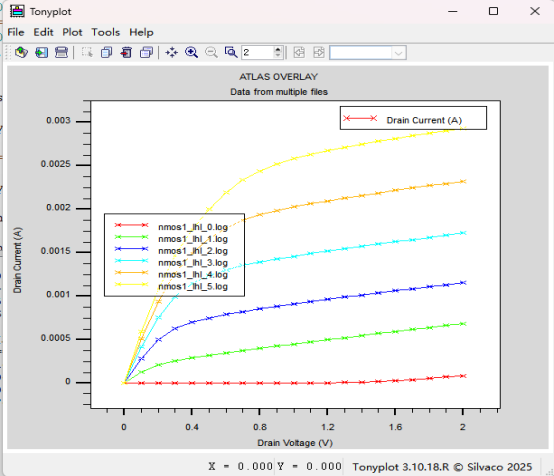

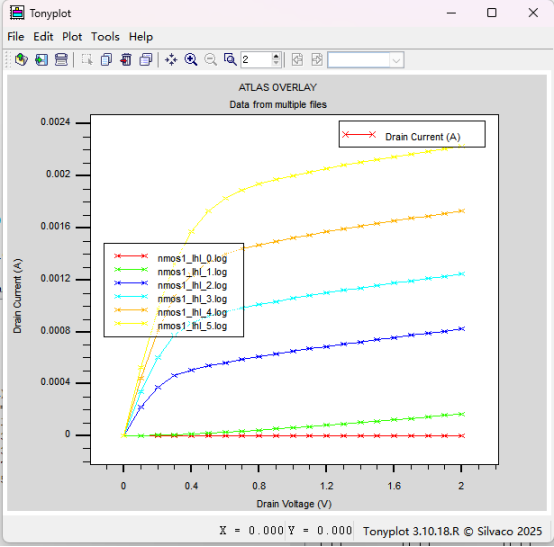

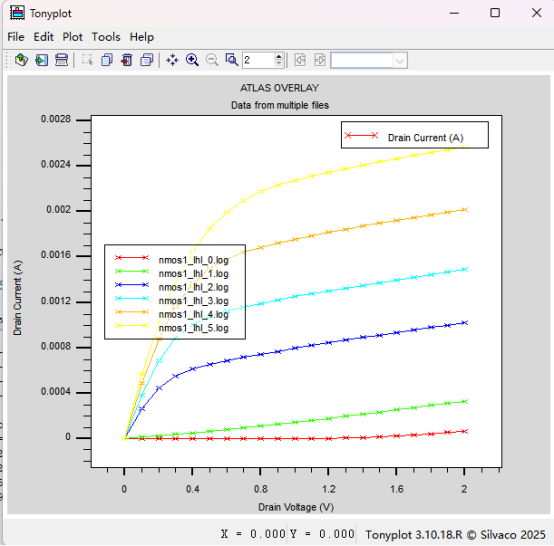

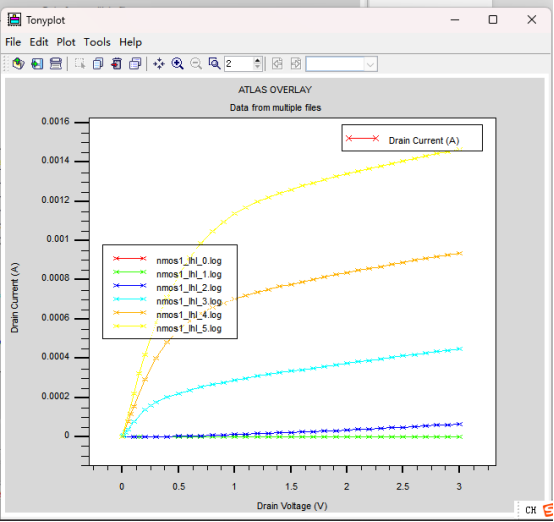

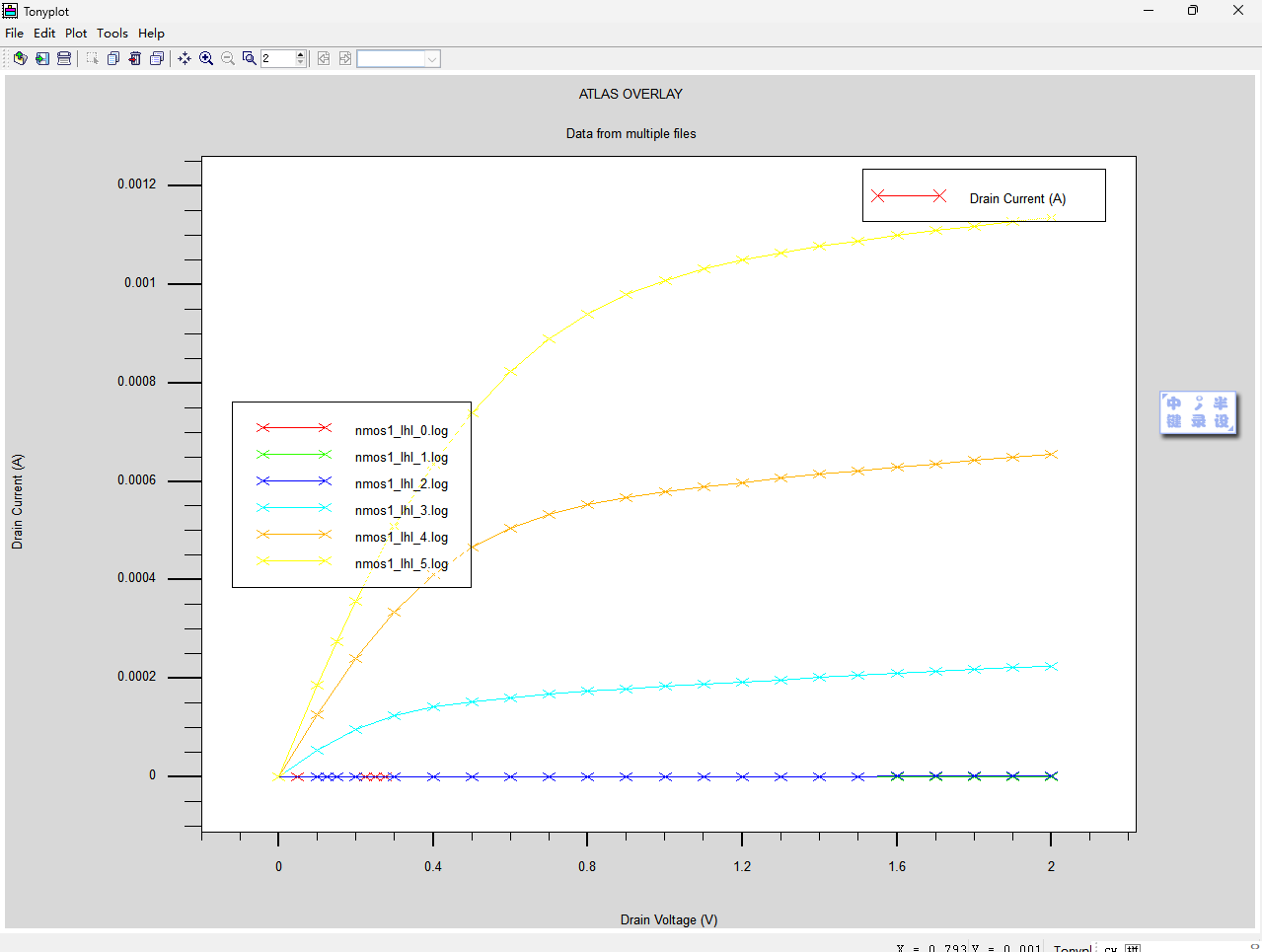

三、仿真输出特性曲线

moefet的输出特性曲线是ID随VD的变化关系

代码

# 使用 CVT 模型分析 MOS

models mos print numcarr=2

#model kla shi auger hcte.el print temperature=300

method gummel newton

solve init

#设置栅极电压

solve vgate=0.5 outf=solve_tmp0_Lhl

solve vgate=1 outf=solve_tmp1_Lhl

solve vgate=2 outf=solve_tmp2_Lhl

solve vgate=2.5 outf=solve_tmp3_Lhl

solve vgate=3 outf=solve_tmp4_Lhl

solve vgate=3.5 outf=solve_tmp5_Lhl

#加载文件和步进 Vd

#设置栅极电压为 solve vgate=0.5 时研究输出特性

load infile=solve_tmp0_Lhl

log outf=nmos1_lhl_0.log

#设置漏极电压起始电压为 0 伏最终电压为1后续同样设置

solve name=drain vdrain=0 vfinal=2 vstep=0.1

#设置栅极电压为 solve vgate=1 时研究输出特性

load infile=solve_tmp1_Lhl

log outf=nmos1_lhl_1.log

solve name=drain vdrain=0 vfinal=2 vstep=0.1

#设置栅极电压为 solve vgate=1.5 时研究输出特性

load infile=solve_tmp2_Lhl

log outf=nmos1_lhl_2.log

solve name=drain vdrain=0 vfinal=2 vstep=0.1

#设置栅极电压为 solve vgate=2 时研究输出特性

load infile=solve_tmp3_Lhl

log outf=nmos1_lhl_3.log

solve name=drain vdrain=0 vfinal=2 vstep=0.1

#设置栅极电压为 solve vgate=2.5 时研究输出特性

load infile=solve_tmp4_Lhl

log outf=nmos1_lhl_4.log

solve name=drain vdrain=0 vfinal=2 vstep=0.1

#设置栅极电压为 solve vgate=3.0 时研究输出特性

load infile=solve_tmp5_Lhl

log outf=nmos1_lhl_5.log

solve name=drain vdrain=0 vfinal=2 vstep=0.1

tonyplot -overlay -st nmos1_lhl_0.log nmos1_lhl_1.log nmos1_lhl_2.log nmos1_lhl_3.log nmos1_lhl_4.log nmos1_lhl_5.log

quit用mos模型分析,

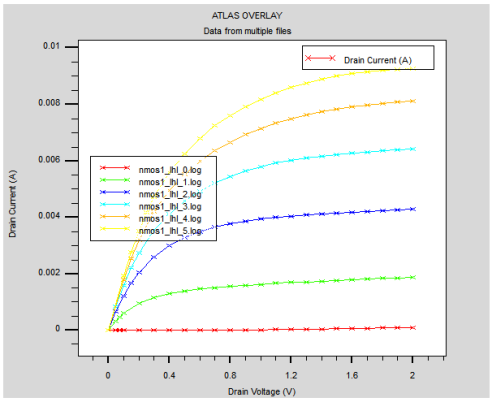

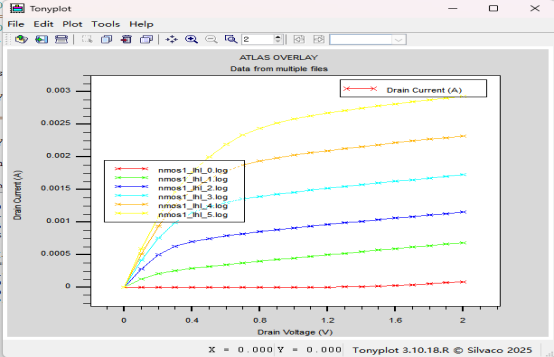

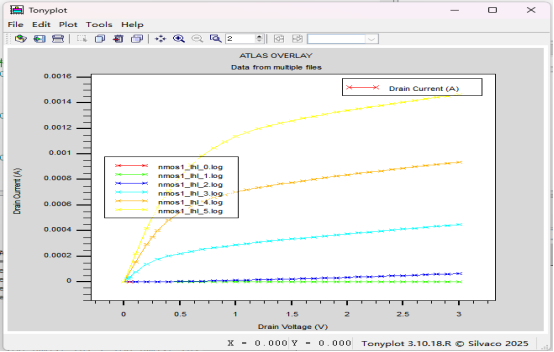

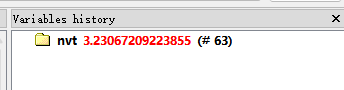

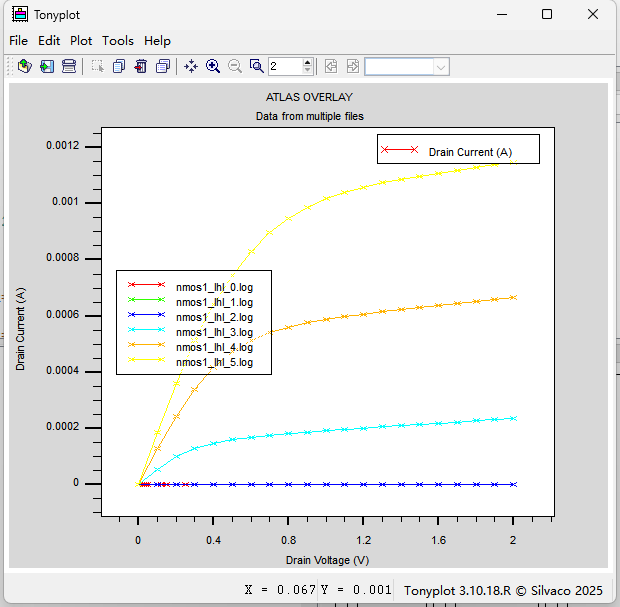

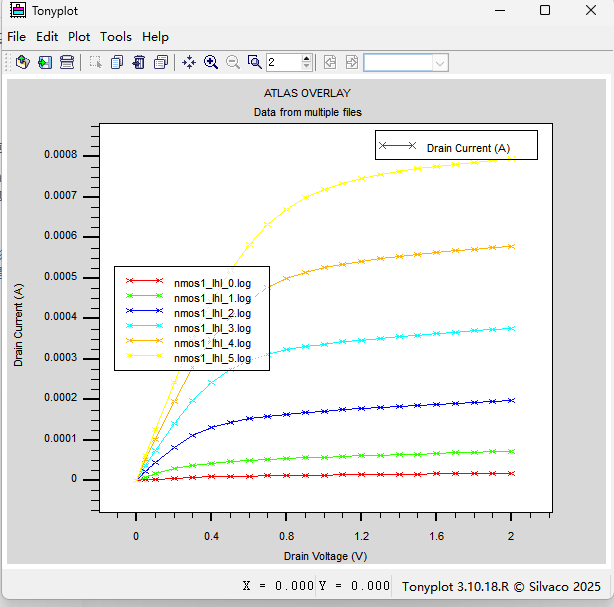

先给不同栅极电压保存到master结构文件,再在不同的栅压下步进解VG,tonyplot-overlay在一张图里,得到下面的输出特性曲线:

一开始仿真得到的曲线可能出现①饱和区斜率大于零②截止区漏电流的问题,下面分析两个比较重要的因素对输出特性曲线的影响;

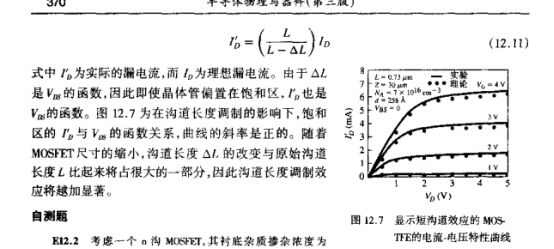

①沟道长度调整效应

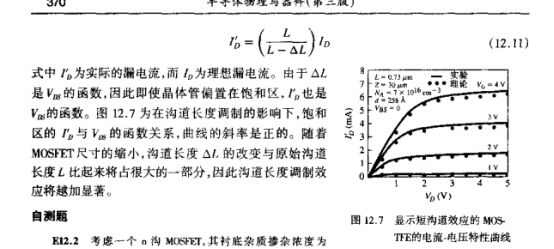

理想的输出特向曲线,饱和区电流不随VD变化,斜率是零,实际可能会受到沟道长度调制的影响,理想的输出特向曲线,饱和区电流不随VD变化,斜率是零,实际可能会受到沟道长度调制的影响,这是由于漏端耗尽区随着反偏电压增大延伸到沟道区,导致栅极实际可调控的沟道长度减小,对钩道的控制能力削弱。现代半导体器件中,栅极尺寸很小,采用finfet,或者nanosheet,ribbon,nanowire结构的GAAfet晶体管,可以增大栅极对沟道的控制能力,减小了短沟道造成效应的影响,使得晶体管尺寸可以沿着摩尔定律进一步缩小。

上面两段摘自尼曼半导体器件物理第12章

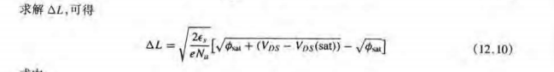

实际沟道是理想沟道长度上再减去ΔL,所以由于沟道长度调制,实际的饱和区电流是在理论值上叠加一段,而且这个叠加的值随VD增大而增大,这就出现了饱和区电流大于零的斜率。同时阈值电压VT也会随着VD增大而减小,进一步增大了ID

NA越大,ΔL越小ID越接近真实值;VD越大,ΔL越大,ID越大,输出特性曲线斜率越大,所以VD大到一定值就可能出现漏电流。

②漏极PN结反向产生电流

截止区漏电流可能是因为漏端PN结反向产生电流,想办法降低PN结反偏时候的产生电流即可。半导体物理刘恩科第六章,

漏端n+p结,所以沟道掺杂的NA越大反偏产生就电流越小。

③DIBL效应,短沟器件的沟道势垒是由栅源电压(Vgs)和栅漏电压(Vgd)决定的。如果漏极电压升高,漏极PN结耗尽区会横向延伸进入gate下面,所以在Vg比较低的情况下,沟道表面势垒由于电场增加而降低,载流子还是能溜过去,也叫亚阈值漏电。

综合上面两种因素,衬底掺杂浓度NA越大曲线越接近理想情况

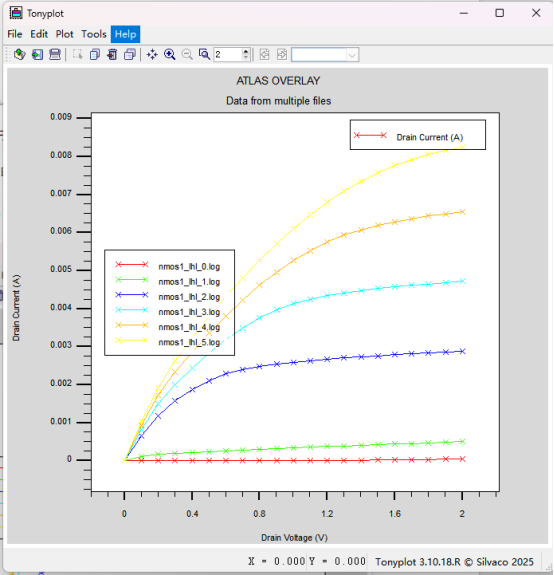

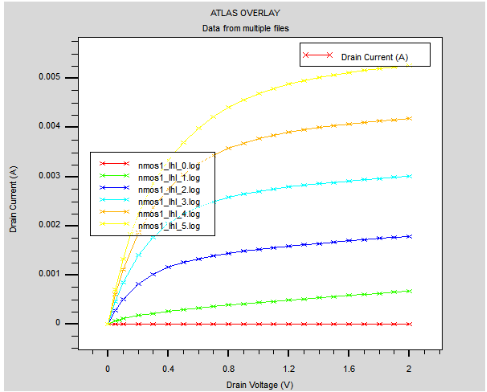

四、饱和区漏极电流的影响因素

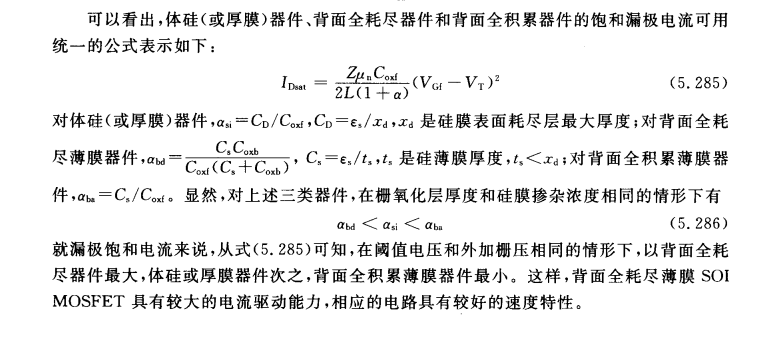

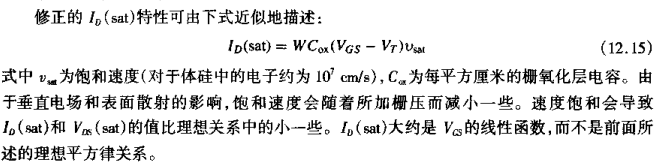

理想情况下普通器件mos和全耗尽、全积累mos器件饱和区漏电流公式:

从公式可以看到,理论上栅极电压,阈值电压沟道宽长比,un电子迁移率,栅氧化层厚度,P衬底掺杂,sio2-si界面电荷这些因素都会影响饱和区电流。下面逐个进行分析:

①栅极电压VG,显而易见,栅压越大ID在饱和区电流值就越大。

②沟道宽长比,W沟道宽度/L沟道长度,ID正比于沟道宽长比。

沟道长度45nm,NA=2E18时

改变沟道长度,45nm变为65nm,NA=2E18,宽长比减小,ID减小

③un电子迁移率,随p衬底掺杂浓度增大而减小,ID反比p衬底掺杂浓度;但是实际电场强度很大的时候,晶格原子温度增大,si的声学波散射增大,迁移率下降,漂移速度达到饱和。这部分放在非理想因素里讨论。

④栅氧化层厚度,栅氧化层厚度越大会同时使得Cox越小,阈值电压VT越大,但两者对ID的影响趋势是相同的,得到ID随栅氧化层厚度减小而增大;

Dox=0.005

Dox=0.0025

Dox=0.0005

⑤绝缘层相对介电常数(k)值,k值越大,ID公式中COX项分子就越大,由于阈值电压Vth=VFB+V0+2VB=Vms-(Q总/Cox)+2VB,因此阈值电压减小,ID公式当中电压平方项增大,所以ID会增大。90nm以下mos氧化层厚度进一步减小,容易发生沟道电子到栅极的隧穿,由于Sio2的相对介电常数比较小为3.9,因此相同的mos结构电容下,使用高k介质材料制作的氧化层厚度更大,换用高k栅介质,可以在保持或增大栅极电容的同时使介质保持足够的物理厚度限制隧穿效应,降低栅极漏电流。

使用material region=2 permittivity=10.0改变栅氧化层材料的相对介电常数。

下面是氧化层材料k值为3.9和10时的输出特性曲线。

permittivity=10.0

⑥P衬底掺杂浓度越大,faifp越大,阈值电压也就越大,ID随p衬底掺杂浓度增大而减小;随p衬底掺杂浓度减小而增大;

NA=2E18

NA=1E19

⑦表面电荷对ID的影响有以下两个方面,首先,二氧化硅层中界面电荷带正电,引起半导体表面能带向下弯曲,起到降低阈值电压的作用,

当表面电荷Q超过10的12次方时,还会对表面电子的迁移率造成影响,这主要是因为表面散射的影响,此外还有热散射时杂志再分布的影响。此时的表面迁移率约为体内的一半,降低了ID。

仿真结果显示,表面电荷越大,ID越大;表面电荷越小,ID越小;可能是表面电荷对阈值电压的影响其主要作用。

绝缘层材料晶格的常数,温度、偏压、辐照等因素都会影响SiO2-绝缘层系统表面和内部电荷分布情况。

Q=1E11 沿用上一步骤的掺杂NA=1E19

改变interface qf=5e12

⑧多晶硅一侧功函数,多晶硅功函数可以根据掺杂发生改变。进而影响阈值电压。

workfunction=4.5

workfunction=5.0

可能由于钉扎效应的原因,改变栅极功函数对阈值电压和饱和区电流的影响不是很明显。

⑨阈值电压VT,阈值电压越大,同一栅压下饱和电流越小,改变P衬底掺杂,栅氧化层厚度,sio2-si界面电荷,多晶硅功函数。都会改变阈值电压。这几个上面都讨论过了。

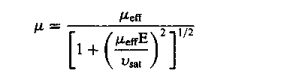

非理想因素

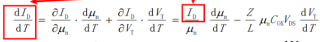

①un电子迁移率,随p衬底掺杂浓度增大而减小,ID反比p衬底掺杂浓度;但是实际电场强度很大的时候,随着温度增大,si的声学波散射增大,迁移率下降,漂移速度达到饱和,这时候的载流子称为热载流子。(可以计算一下电子迁移率在1e3的时候,速度已经远远高于饱和速度1e7)应该考虑电子的有效迁移率,这时候的迁移率公式:

atlas-commond里还可以看到,如果使用自带的mos模型,在迁移率模型里面已经引入了场迁移率模型的公式:

由于速度饱和,饱和电流公式可以修正为

速度饱和会导致ID比理想值小一点。

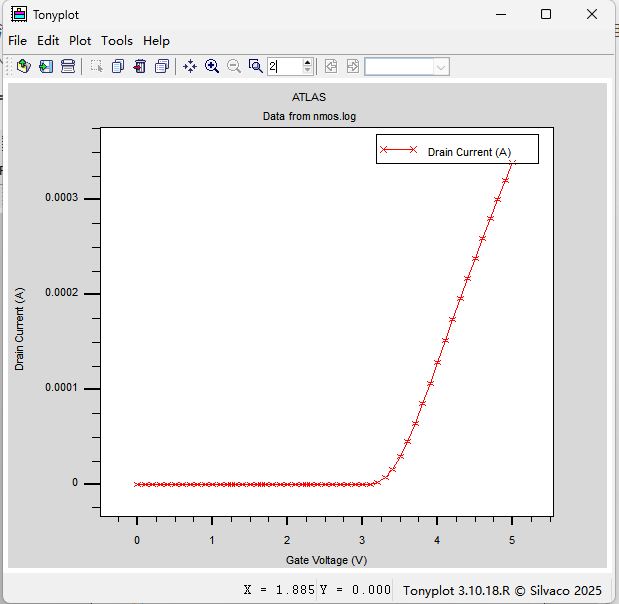

tonyplot中查看电子沿沟道方向速度,大部分电子速度已经达到10的7次方,达到了饱和速度。

应变硅技术可以引入沟道应力来提高沟道载流子迁移率,减小由于器件尺寸缩小导致的迁移率下降,沟道的张应力可以提高nmos的电子迁移率,可以通过Si3N4应力帽技术实现,或者在沟道中埋入一层SiGe,参考atlas例程mosex12、mosex13。

②沟道长度调制

理想的输出特向曲线,饱和区电流不随VD变化,斜率是零,实际可能会受到沟道长度调制的影响,

由于沟道长度调制,实际的饱和区电流是在理论值上叠加一段,而且这个叠加的值随VD增大而增大,这就出现了饱和区电流大于零的斜率。同时阈值电压VT也会随着VD增大而减小,进一步增大了ID。

环境因素也会影响上面提到的这些参数,特别是温度。

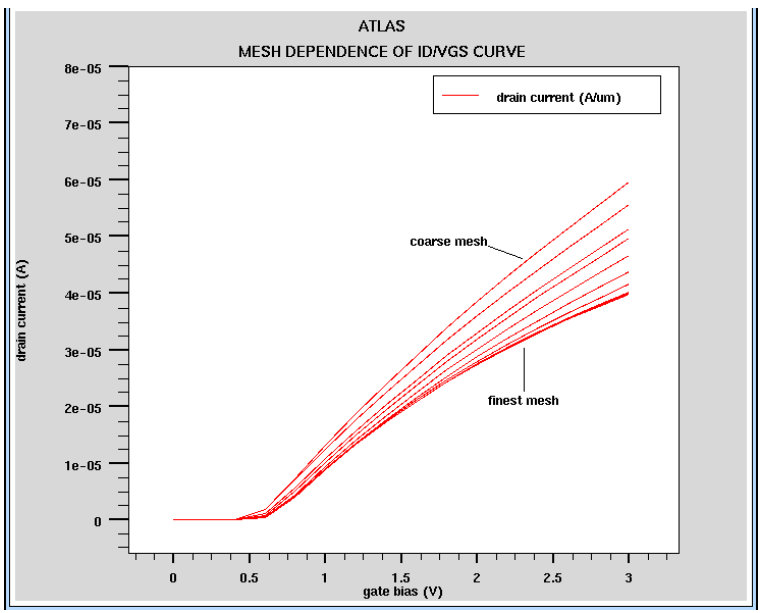

温度可以影响MOS管下面两个因素

1. 阈值电压V_th的温度依赖性

MOS管的阈值电压通常具有负温度系数,即当温度升高时,V_th会降低。主要原因如下:

载流子浓度增加:随着温度升高,半导体材料内的热激发载流子增加,使得沟道更容易形成,从而降低V_th。

界面态变化:MOS管栅极氧化层与半导体界面可能会受到温度的影响,导致界面态密度变化,使得阈值电压发生漂移。

半导体材料的温度特性:硅等半导体材料的能带结构受温度影响较大,高温下,导带和价带间的带隙会缩小,从而影响MOS管的导通特性。

在高温环境下,阈值电压的降低可能导致MOS管更容易误导通,使得漏极电流I_D增大

2. 导通电阻的温度变化

MOS管导通后,漏源电阻R_DS(on)会影响其电压损耗和功率消耗。一般而言,R_DS(on)具有正温度系数,即温度升高时,R_DS(on)也会增大。这一现象的主要机理包括:

载流子迁移率降低:温度升高会增强晶格的散射效应,导致载流子的运动受限,从而降低载流子迁移率,提高沟道电阻。

寄生效应增强:在高温环境下,MOS管内部的寄生元件(如体二极管)的影响会变得更加显著,可能导致漏源电阻

沟道载流子浓度分布变化:随温度上升,半导体中的载流子分布发生改变,使得沟道电阻增大,从而影响导通状态下的电压降

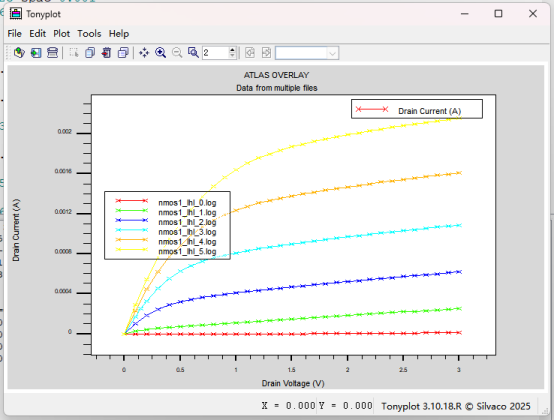

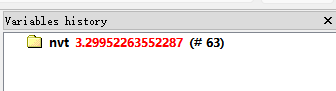

只考虑对上面两个参数的影响,温度越大,mosfet输出特性曲线饱和区电流越小。

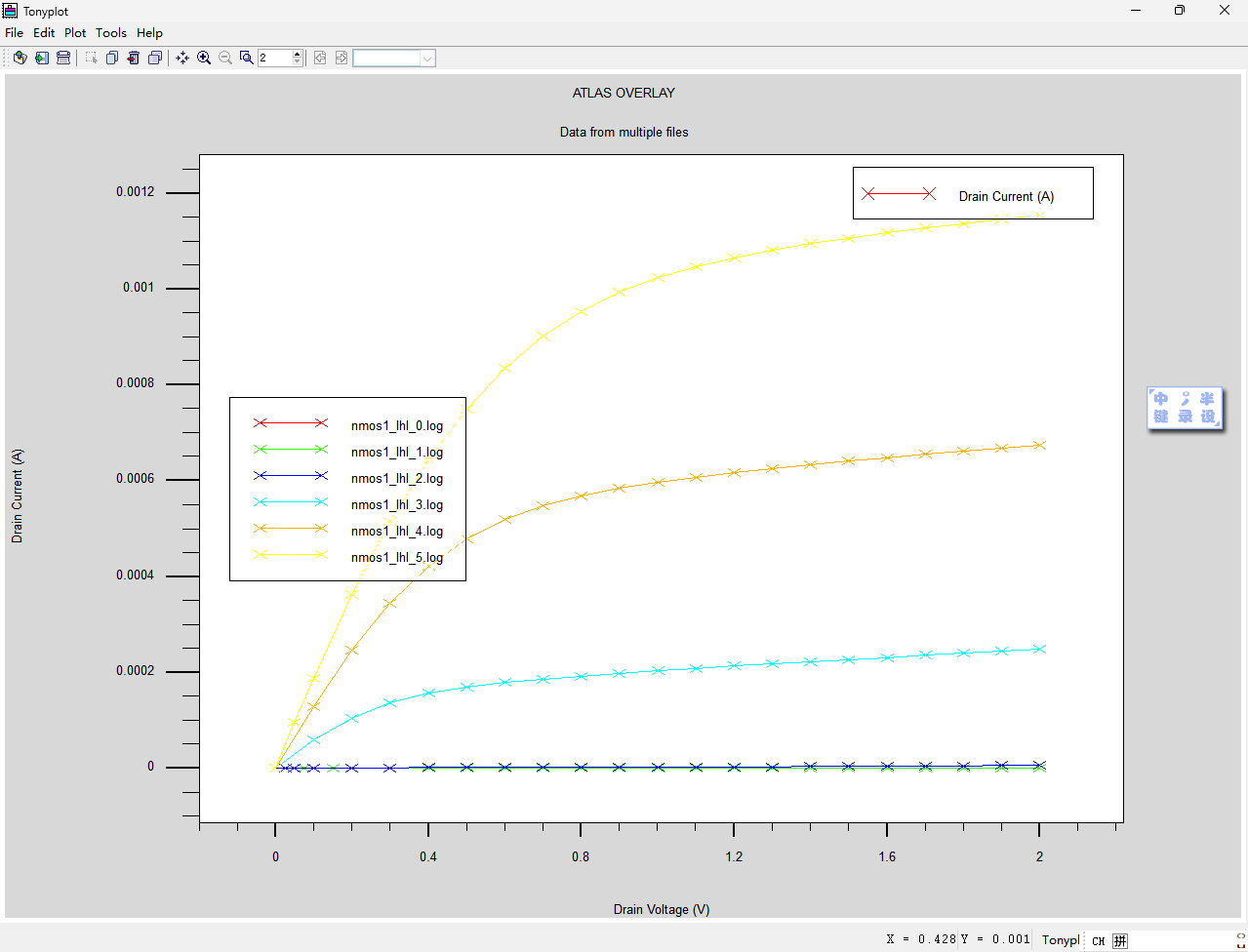

T=300K,跑出来的阈值电压和输出特性曲线

T=1000K,跑出来的阈值电压和输出特性曲线

当满足上式时,漏极电流的温度系数为零,温度对漏极电流无影响。

总的说来,MOSFE漏极电流随温度变化较小,有较好的温度稳定性

仿真中使用的模型不同以及网格精度也会影响载流子迁移率等因素,影响漏极电流。发现有些非理想因素引入和不引入阈值电压和电流都会有很大差别。

上面提到的所有影响因素,在原先代码上更改对应的参数就可以,代码太多这里就不一一列举了。

Windows版silvaco2018安装

926

926