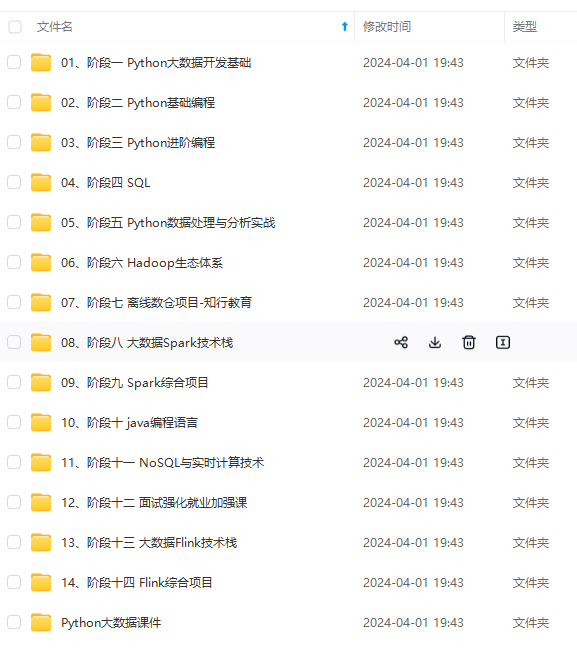

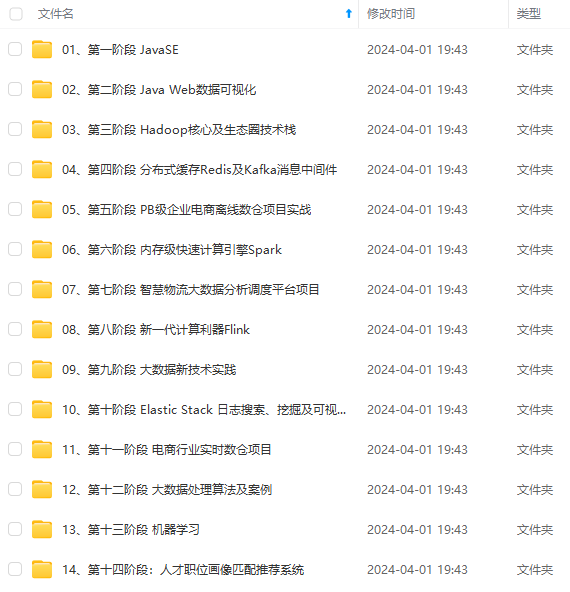

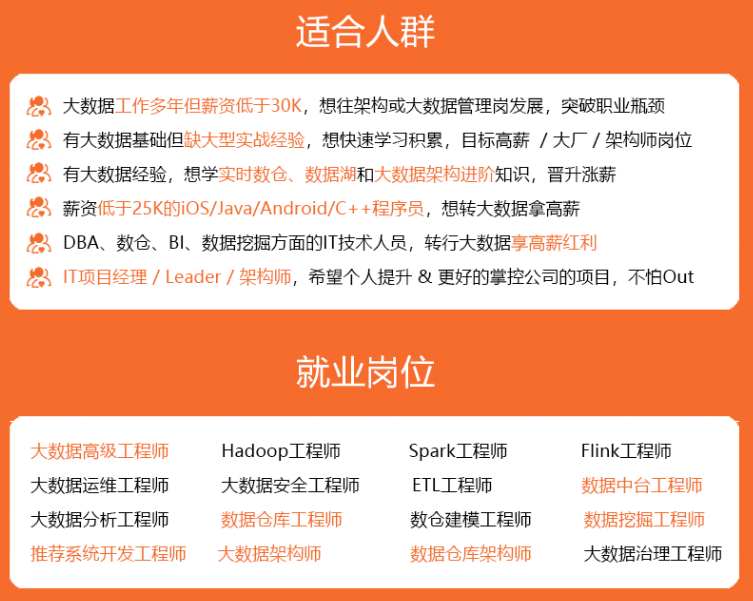

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

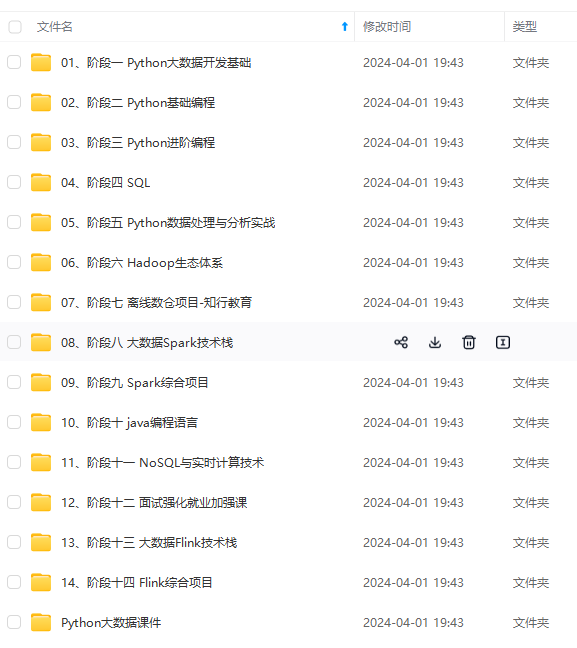

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

系列目录与传送门

一、CLB概述

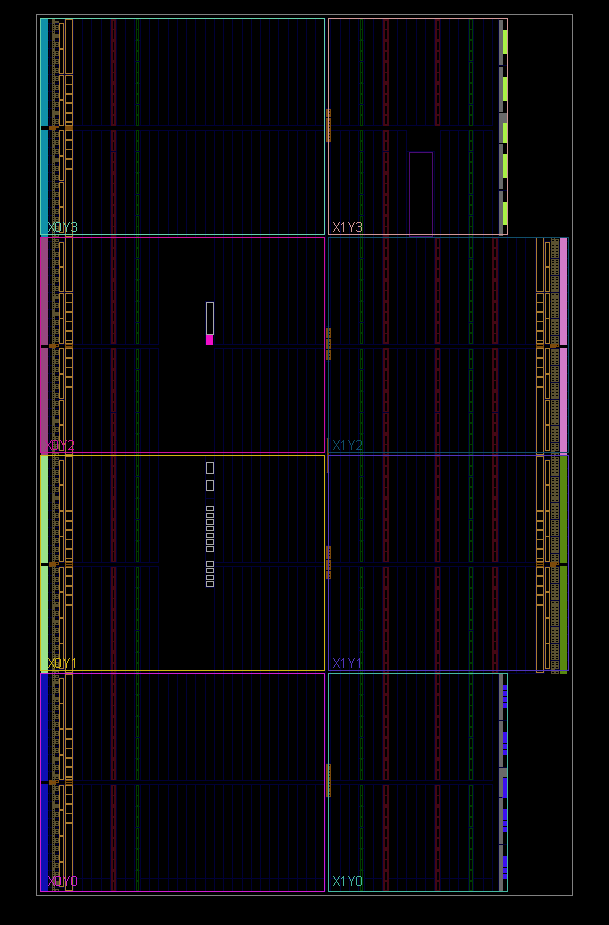

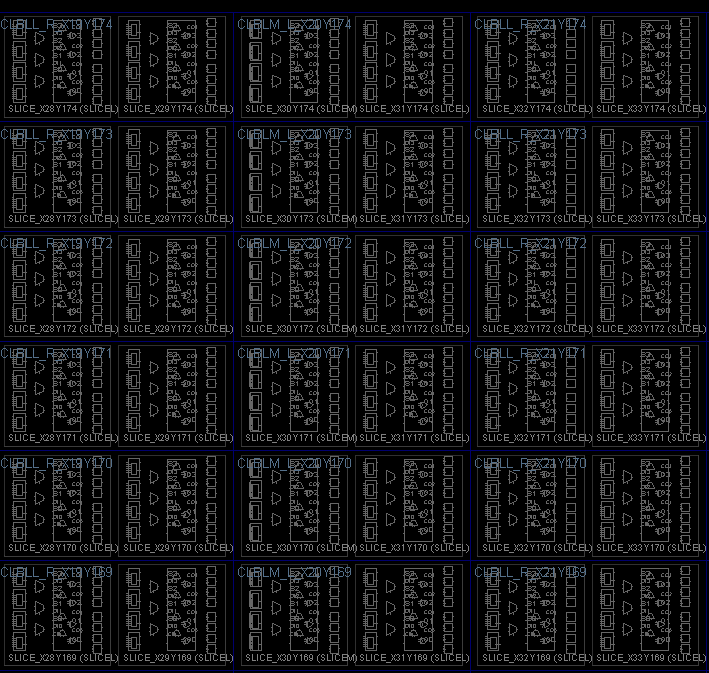

我们可以用vivado打开一个器件的device视图:

可以看到这些花里胡哨的五颜六色就分别代表了FPGA的底层硬件单元,主要有:可编程输入输出单元(IOB)、可编程逻辑单元(CLB)、时钟管理单元(MMCM/PLL)、BRAM、布线资源、内嵌的底层功能单元和内嵌专用硬件模块。其中最为主要的是可编程输出输出单元(IOB)、可编程逻辑单元(CLB)和布线资源。

而我们今天的主角可编程逻辑单元CLB则在上图中蓝色的若隐若现的位置,我们需要把它放大才能更好地观察:

蓝色框中的就是CLB,同时也可以发现,CLB是由两个不的元素组成,这个元素我们称之为SLICE。

如果把FPGA实现的电路看做是积木拼成的摩天大楼,那么CLB就是实现大楼的最基本元素–砖块。 但是我们盖楼不可能只使用一种砖块,同样的为了实现各种功能的电路,我们也要把CLB切成了更小的块以便灵活组合实现更复杂的电路。

所以,CLB实际上是四种基本元素的集合----查找表LUT,进位链CARRY4,多路选择器Multiplexer以及存储单元FF。有了这四种基本元素后,我们就可以灵活组合实现各种时序逻辑和组合逻辑了。

二、SLICEM与SLICEL

一个CLB是由2个SLICE组成的,SLICE根据其中的LUT6能实现的功能可以分为以下两种:

- SLICEM(M:Memory):其内部的LUT可以读也可以写,可以实现移位寄存器和DRAM等存储功能,还可以实现基本的查找表逻辑

- SLICEL(L:Logic): 其内部的LUT只可以读,只能实现基本的查找表逻辑

CLB的组成可以是上图的1个SLICEM + 1个SLICEL,或者是2个SLICEL,但是不会是2个SLICEM 。一般情况下,CLB中比例SLICEL:SLICEM = 2:1。

总结一下:1个CLB = 2个SLICE = 2 ×(4个LUT + 3个MUX + 1个CARRY4 + 8个FF),这就是CLB和SLICE的架构了。

三、查找表LUT

本章节只是大概阐述,详细内容强烈推荐阅读:从底层结构开始学习FPGA----LUT查找表

查找表Look-up Table,本质上就是1个6输入,64深度的ROM(SLICEM中的则是RAM,因为可读)。通过将所有结果保存在其内部,使用时通过由输入构建的地址线对其进行查找,从而实现6输入的函数逻辑。

比如,你要实现功能:y = a | b ^ c & d & e & f。输入一共6个,可能的结果就是2的6次方64个,我把这64个结果全部存到LUT里,只要在使用的时候根据输入(也就是地址),拿出存在对应位置的结果就行了,这就是LUT实现各种函数的原理。

需要注意的是SLICEM中的查找表,除了读功能外还具备写功能,这就使得其内部的LUT由一个ROM变成了一个RAM,这也是其实现移位寄存器功能和分布式DRAM功能的原因。

3.1、移位寄存器SRL

本章节只是大概阐述,详细内容强烈推荐阅读:从底层结构开始学习FPGA----移位寄存器

SLICEM可以在不使用触发器的条件下配置为32位移位寄存器(注意:只能左移)。这样,每个LUT可以将串行数据延迟1到32个时钟周期。移位输入D(LUT DI1脚)和移位输出Q31(LUT MC31脚)可以进行级联,以形成更大的移位寄存器。一个SLICEM的4个LUT6级联可以实现128个时钟周期的延时。多个SLICEM也可以进行组合。但SLICEM之间没有直接连接以形成更长的移位寄存器,在LUT B/C/D处的MC31输出也没有。由此产生的可编程延迟可用于平衡数据pipeline的时间。

那这种 Shifter Register 可以用来做什么呢?Xilinx Guide 中也给出了回答:

- Delay or latency compensation

- Synchronous FIFO

- content addressable memory (CAM)

3.2、分布式DRAM

本章节只是大概阐述,详细内容强烈推荐阅读:从底层结构开始学习FPGA----分布式RAM(DRAM,Distributed RAM)

SLICEM 中的 LUT 除了用作移位寄存器外,还可以被配置为Distributed RAM(DRAM)。DRAM 的 write 是同步的,read 则是异步的。注意这里所说的同步异步不是跨时钟域的概念,而是类似于组合逻辑和时序逻辑的概念。可以理解为,write 是时序逻辑,只有在时钟有效沿且 write enable 为1时,数据才会被写入。而 read 则和时钟无关,只要地址有效,数据就会在当前周期输出。如果想要同步输出,我们可以自己在输出端加 register。

DRAM的概念是相对于BRAM来说的,BRAM是FPGA底层的固有的硬件单元,而DRAM则是使用LUT配置而成的,其位置和使用会稍微灵活一些,但是也有其他不足,两者的使用需要权衡。

DRAM可以分为以下几种:

- Single-port:Write 和 Read 共享一组地址线。也就是说 write 和 read 不能同时进行。

- **Dual-port:**一个 port 用来 write 和 read,另一个 port 只有 read。

- **Simple dual-port:**一个 port 用来 write,一个 port 用来 read

四、多路选择器MUX

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

!**

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

3916

3916

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?