FPGA图像缩放方案

我的主页目前有FPGA图像缩放专栏,改专栏收录了我目前手里已有的FPGA图像缩放方案,从实现方式分类有基于HSL实现的图像缩放、基于纯verilog代码实现的图像缩放;从应用上分为单路视频图像缩放、多路视频图像缩放、多路视频图像缩放拼接;从输入视频分类可分为OV5640摄像头视频缩放、SDI视频缩放、MIPI视频缩放等等;以下是专栏地址:

点击直接前往

自己写的HLS图像缩放方案

之前写过一篇自己写的HLS图像缩放的博客,该方案与官方的Video Processing Subsystem区别在于手写的看得到;以下是博客地址:

点击直接前往

3、设计思路详解

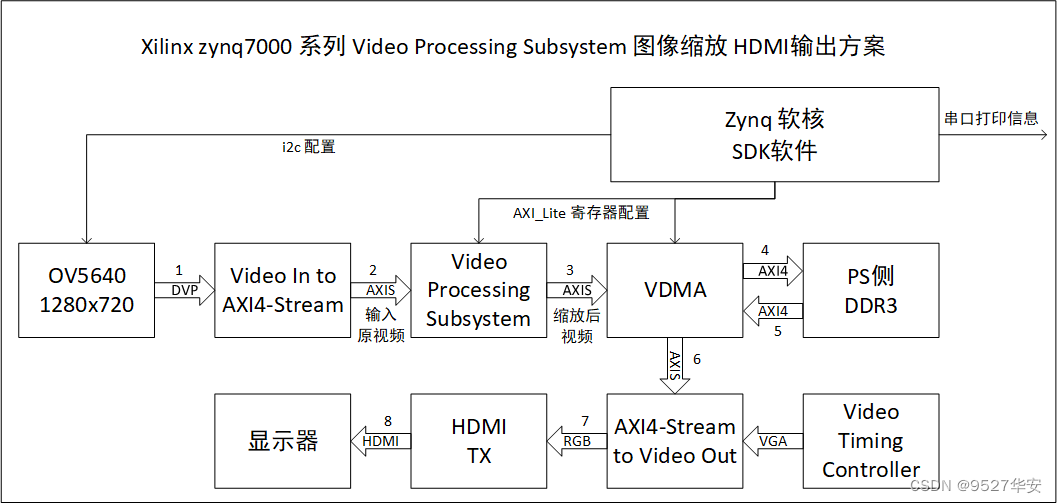

本文使用Xilinx Zynq7000系列FPGA Zynq7020实现Video Processing Subsystem图像缩放,输入视频源采用OV5640摄像头模组;FPGA采集OV5640摄像头视频DVP转RGB888,调用Zynq软核的片内i2c控制器将OV5640配置为1280x720@30Hz分辨率;然后调用Xilinx官方的Video In to AXI4-Stream IP核将RGB视频流转换为AXI4-Stream视频流;然后调用Xilinx官方的Video Processing Subsystem IP核将输入视频进行任意尺寸图像缩放操作,该操作通过Zynq软核SDK软件配置,其本质为通过AXI_Lite 做寄存器配置;然后调用Xilinx官方的VDMA IP将视频做PS侧DDR3的视频缓存操作,调用Zynq将VDMA配置为三帧缓存,其本质为通过AXI_Lite 做寄存器配置;然后调用Xilinx官方的Video Timing Controller IP和AXI4-Stream to Video Out IP将AXI4-Stream视频流转换为RGB视频流;然后添加自定义的HDMI发送IP将RGB视频转换为TMDS的差分视频送显示器显示;提供一套vivado2019.1版本的工程源码和技术支持;

工程源码设计框图如下:

框图解释:箭头表示数据流向,箭头内文字表示数据格式,箭头外数字表示数据柳巷的步骤;

Video Processing Subsystem 介绍

由于工程所用到的IP都是常用IP,所以这里重点介绍一下Video Processing Subsystem;

Video Processing Subsystem有缩放、去隔行、颜色空间转换等功能,这里仅使用图像缩放功能;其特点如下:

适用于Xilinx所有系列的FPGA器件;

支持最大分辨率:8K

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3060

3060

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?