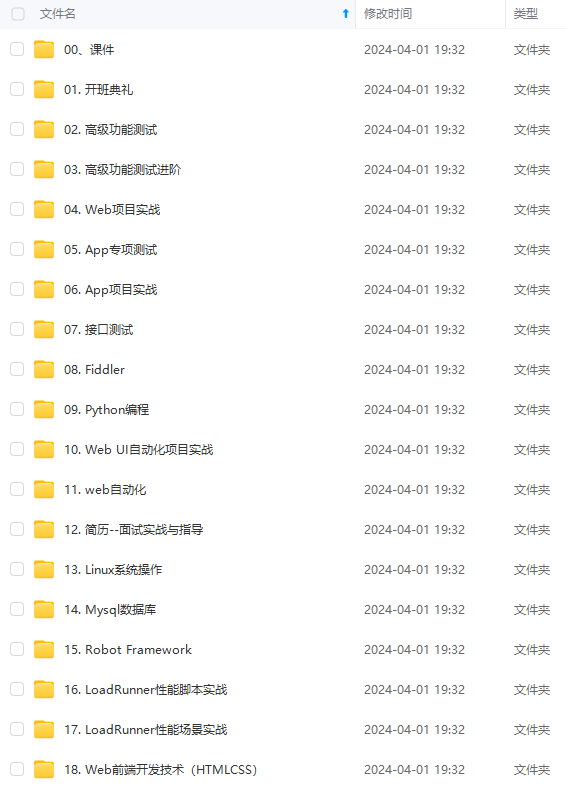

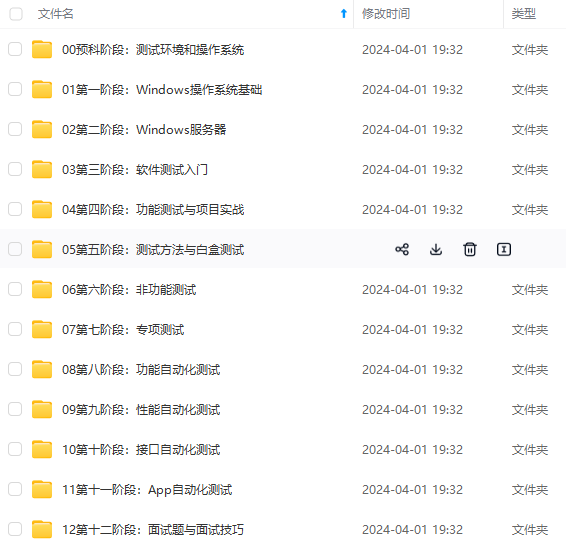

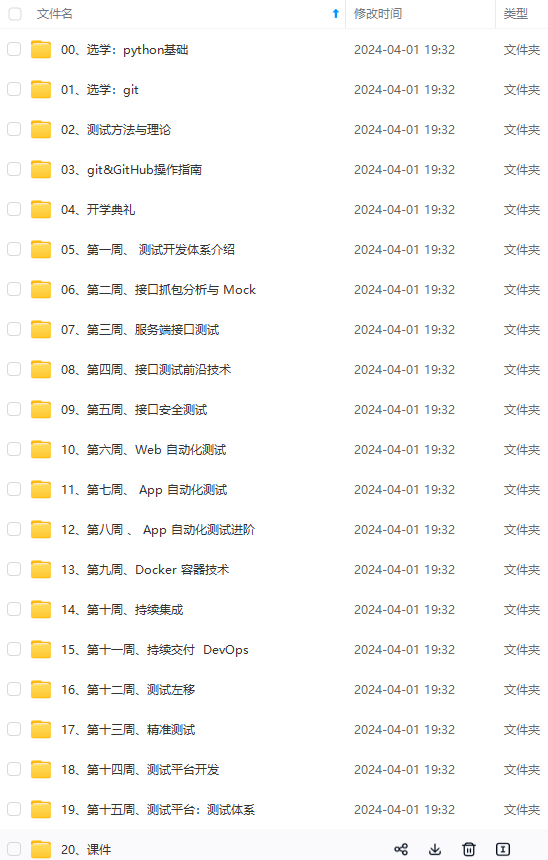

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上软件测试知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-l9iJpi3K-1594166729677)(en-resource://database/579:1)]](https://img-blog.csdnimg.cn/20200712083221520.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

-

主存与CPU之间的联系

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-tg67a4Wx-1594166729678)(en-resource://database/578:1)]](https://img-blog.csdnimg.cn/20200712083232873.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

-

主存中存储单元地址的分配

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-UQCRBBlL-1594166729679)(en-resource://database/580:1)]](https://img-blog.csdnimg.cn/2020071208324721.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

-

主存的技术指标

- 存储容量 主存存放二进制代码的总位数

- 存储速度

1、存取时间:存储器的访问时间、读出时间、写入时间

2、存取周期:连续两次独立的存储器操作,(读与写)所需的最小间隔时间 ;读周期 写周期 - 存储器的带宽 位/秒

2、半导体存储芯片简介

- 基本结构

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-63ppi4Dk-1594166729680)(en-resource://database/581:1)]](https://img-blog.csdnimg.cn/20200712083301334.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-djZ3B8EG-1594166729681)(en-resource://database/582:1)]](https://img-blog.csdnimg.cn/20200712083312935.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

3、随机存取存储器(RAM)

- 静态RAM(SRAM)

1、静态RAM基本电路

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-CCIFm1mZ-1594166729682)(en-resource://database/583:1)]](https://img-blog.csdnimg.cn/20200712083331330.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 动态RAM(DRAM)

1、动态RAM基本单元电路

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-XVwRt8lR-1594166729683)(en-resource://database/584:1)]](https://img-blog.csdnimg.cn/20200712083344171.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 动态RAM和静态RAM的比较

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-HDJprUJt-1594166729684)(en-resource://database/585:1)]](https://img-blog.csdnimg.cn/20200712083358165.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

4、只读存储器(ROM)

- 掩模ROM(MROM)

行列选择性交叉处有MOS管为“1”

行列选择线交叉处无MOS管为“0” - PROM(一次性编程)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Td0VUOps-1594166729685)(en-resource://database/587:1)]](https://img-blog.csdnimg.cn/20200712083413119.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- EPROM(多次性编程)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-U7eDBjkG-1594166729686)(en-resource://database/586:1)]](https://img-blog.csdnimg.cn/20200712083424322.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- EEPROM

电可擦写

局部擦写

全部擦写 - Flash Memory(闪速型存储器)

EPROM 价格便宜 集成度高

EEPROM 电可擦洗重写

比EEPROM快 具备RAM功能

5、存储器与CPU的连接

- 存储容量的扩展

用2片1K X 4位的存储芯片组成1K X 8位的存储器 - 子扩展(增加存储子的数量)

用2片1K X 8位的存储芯片组成 2K X 8位的存储器;两个芯片不能同时操作 - 字、位扩展

用8片 1K X 4位存储芯片组成4K X 8位的存储器

6、存储器的校验

- 编码的最小距离

任意两组合法代码之间二进制位数的最少差异

编码的纠错、检错能力与编码的最小距离有关

7、提高访存速度的措施

- 采用高速器件

- 采用层次结构 Cache-主存

- 调整主存结构

3、高速缓冲存储器

一、概述

避免CPU“空等”现象

二、Cache的工作原理

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-9SszjeV3-1594166729688)(en-resource://database/588:1)]](https://img-blog.csdnimg.cn/20200712083500208.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

三、Cache的基本结构

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-V2DjCBiz-1594166729689)(en-resource://database/589:1)]](https://img-blog.csdnimg.cn/20200712083510679.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

四、Cache的读写操作

- 读操作

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-reOq3i62-1594166729690)(en-resource://database/590:1)]](https://img-blog.csdnimg.cn/20200712083522109.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- “写操作” Cache和主存的一致性

- 写直达法(Write-through)

写操作时数据既写入cache又写入主存

写操作时间就是访问主存的时间,Cache块退出时,不需要对主存执行写操作,更新策略比较容易实现 - 写回法(Write-back)

写操作时只把数据写入Cache而不写入主存,当Cache数据被替换出去时才写回主存

写操作时间就是访问Cache的时间,Cache块退出时,被替换的块需写回主存增加了Cache的复杂性

- 写直达法(Write-through)

5、Cache的改进

- 1、增加Cache的级数

片载(片内)Cache - 2、统一缓存和分立缓存

指令Cache 数据Cache

与指令执行的控制方式有关(是否是流水线)

Cache-主存的地址映射

- 直接映射(离CPU近就采用这种方式)

某一主存块只能固定映射到某一缓存块 不灵活、速度快

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-WOrsmnnR-1594166729691)(en-resource://database/591:1)]](https://img-blog.csdnimg.cn/20200712083544576.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 全相联映射

某一主存块能映射到任一缓存块 成本高、速度低

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-PpjZ9TQf-1594166729692)(en-resource://database/592:1)]](https://img-blog.csdnimg.cn/20200712083558779.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 组相联映射

速度快、cache的命中率高

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-kpIB6V4K-1594166729693)(en-resource://database/593:1)]](https://img-blog.csdnimg.cn/20200712083616538.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 替换算法 (判断哪一个Cache块从Cache中退出)

1、先进先出(FIFO)算法

2、近期最少使用(LRU)算法

4、辅助存储器

一、概述

- 不直接与CPU交换信息

- 磁表面存储技术指标

- 记录密度

- 存储容量

C = n X k X s - 平均寻址时间

寻道时间+等待时间 - 数码传输率

- 误码率

出错信息位数与读出信息的总位数的比值

二、磁记录原理和记录方式

- 磁记录原理

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-GggkRASZ-1594166729694)(en-resource://database/595:1)]](https://img-blog.csdnimg.cn/20200712083635331.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-qD0bkGoM-1594166729695)(en-resource://database/594:1)]](https://img-blog.csdnimg.cn/20200712083646118.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

三、硬磁盘存储器

- 硬磁盘存储器的类型

- 固定磁头和移动磁头

- 可换盘和固定盘

- 硬磁盘存储器的结构

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-hheZXbtg-1594166729696)(en-resource://database/596:1)]](https://img-blog.csdnimg.cn/20200712083656940.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

五、输入输出系统

一、概述

1、输入输出系统的发展概况

- 早期

分散连接

CPU和I/O设备串行工作 - 接口模块和DMA阶段

总线连接

CPU和I/O设备并行工作,一个总线可以连接多个设备 - 具有通道结构的阶段

- 具有I/O处理机的阶段

2、输入输出系统的组成

- 一、I/O软件

1、 I/O指令 CPU指令的一部分

2、通道指令 通道自身的指令

指出数组的首地址、传送字数、操作命令 - 二、I/O硬件

设备 I/O接口

设备 设备控制器 通道

3、I/O设备与主机的联系方式

- 一、I/O设备编址方式

1、统一编址 用取数、存数指令

2、不统一编址 有专用的I/O指令 - 二、设备选址

用设备选择电路识别是否被选中 - 三、传送方式

1、串行

2、并行 - 四、联络方式

1、立即响应

2、异步工作采用应答信号

3、同步工作采用同步时标 - 五、I/O设备与主机的连接方式

1、辐射式连接(分散连接)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-ZHiTXHKC-1594166729697)(en-resource://database/597:1)]](https://img-blog.csdnimg.cn/20200712083712692.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

2、总线连接

便于增删设备

4、I/O设备与主机信息传送的控制方式

- 一、程序查询方式

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-2XE3SCsl-1594166729698)(en-resource://database/598:1)]](https://img-blog.csdnimg.cn/20200712083732146.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 二、程序中断方式

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-ZCIKTApZ-1594166729699)(en-resource://database/599:1)]](https://img-blog.csdnimg.cn/20200712083745128.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

程序中断方式流程

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Uwb53KcG-1594166729702)(en-resource://database/601:1)]](https://img-blog.csdnimg.cn/20200712083817364.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 三、DMA方式

主存和I/O之间有一条直接数据通道

不中断执行

周期挪用(周期窃取)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-gBxNWrEb-1594166729704)(en-resource://database/602:1)]](https://img-blog.csdnimg.cn/2020071208383050.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

二、外部设备

一、概述

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-1d0LGK94-1594166729705)(en-resource://database/603:1)]](https://img-blog.csdnimg.cn/20200712083838832.png)

外部设备大致分三类

1、人机交互设备

2、计算机信息存储设备

3、机-机通信设备 调制解调器等

二、输入设备

- 键盘

- 鼠标

- 触摸屏

三、输出设备

- 显示器

1、字符显示

2、图形显示

3、图像显示 - 打印机

1、击打式

2、非击打式

四、其他

- A/D、D/A 模拟/数字(数字/模拟)转换器

- 终端 由键盘和显示器组成

- 汉字处理

五、多媒体设备

三、I/O接口

一、概述

为什么要设置接口?

1、实现设备的选择

2、实现数据缓冲达到速度匹配

3、实现数据串——并格式转换

4、实现电平转换

5、传送控制命令

6、反映设备的状态

二、接口的功能和组成

- 总线连接方式的I/O接口电路

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-2bn6uRxe-1594166729706)(en-resource://database/604:1)]](https://img-blog.csdnimg.cn/20200712083900481.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 功能

1、选址功能

2、传送命令的功能

3、传送数据的功能

4、反映设备状态的功能 - 组成

1、设备选择电路

2、命令寄存器、命令译码器

3、数据缓冲寄存器

4、设备状态标记 - I/O接口的基本组成

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-9NEhx6U2-1594166729707)(en-resource://database/606:1)]](https://img-blog.csdnimg.cn/2020071208391435.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

三、接口类型

- 1、按数据传送方式分类

并行接口

串行接口 - 按功能选择的灵活性分类

可编程接口

不可编程接口 - 按通用性分类

通用接口

专用接口 - 按数据传送的控制方式分类

中断接口

DMA接口

四、程序查询方式

- 程序查询流程

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-C5Uw86u9-1594166729709)(en-resource://database/605:1)]](https://img-blog.csdnimg.cn/20200712083937704.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-rtjl2Tsz-1594166729710)(en-resource://database/607:1)]](https://img-blog.csdnimg.cn/20200712083949193.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 程序流程

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-VWTNOAHA-1594166729711)(en-resource://database/608:1)]](https://img-blog.csdnimg.cn/2020071208400837.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 程序查询方式的接口电路

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-gPmPLlCn-1594166729712)(en-resource://database/609:1)]](https://img-blog.csdnimg.cn/20200712084018864.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

五、程序中断方式

1、中断的概念

代办

2、I/O中断的产生

代办

3、程序中断方式的接口电路

代办

4、I/O中断处理过程

代办

5、中断服务程序流程

代办

六、DMA方式

1、DMA方式的特点

- 可直接从I/O设备传送到主存

- DMA与主存交换数据的三种方式

- 停止CPU访问主存

控制简单

CPU处于不工作状态或保持状态

未充分发挥CPU对主存的利用率 - 周期挪用(周期窃取)

1、 访存周期

2、DMA访问主存有三种可能- CPU此时不访存

- CPU正在访存

- CPU与DMA同时请求访存

- DMA与CPU交替访问

- 停止CPU访问主存

2、DMA接口的功能和组成

- 1、DMA接口功能

- 向CPU申请DMA传送

- 处理总线控制权的转交

- 管理系统总线、控制数据传送

- 确定数据传送的首地址和长度

修正传送过程中的数据地址和长度 - DMA传送结束时,给出操作完成信号

- 2、DMA接口的组成

3、DMA的工作过程

- DMA传送过程

预处理、数据传送、后处理

六、计算机的运算方法

1、无符号数和有符号数

一、无符号数

二、有符号数

- 机器数与真值

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-eKBko5Pl-1594166729713)(en-resource://database/610:1)]](https://img-blog.csdnimg.cn/20200712084038372.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 原码表示法

整数、小数、 - 补码表示法

- 移码表示法

2、数的定点表示和浮点表示

代办

3、定点运算

代办

4、浮点四则运算

代办

5、算数逻辑单元

7、指令系统

一、机器指令

二、操作数类型和操作种类

1、操作数类型

- 地址 无符号整数

- 数字 定点数、浮点数、十进制数

- 字符 ASCII码

- 逻辑数 逻辑运算

2、数据在存储器中的存放方式

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-cd8WWeT2-1594166729713)(en-resource://database/611:1)]](https://img-blog.csdnimg.cn/20200712084107345.png)

数据在存储器中的存放方式

- 字节编址,数据在存储器汇总的存放方式(存储字长64位,机器字长32位)

3、操作类型

- 1、数据传送

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-BehIiCd7-1594166729714)(en-resource://database/612:1)]](https://img-blog.csdnimg.cn/20200712084122348.png)

- 2、算术逻辑操作

加、减、乘、除、增1、减1、求补、浮点运算、十进制

与、或、非、异或、位操作、位测试、位清除 - 3、位移操作

算术移位、逻辑移位

循环移位 - 转移

无条件转移 JMP

条件转移

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-RjRzdZmf-1594166729715)(en-resource://database/613:1)]](https://img-blog.csdnimg.cn/20200712084132823.png)

三、寻址方式

1、指令寻址

代办

2、数据寻址

- 立即寻址

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-DRUm7qWe-1594166729716)(en-resource://database/614:1)]](https://img-blog.csdnimg.cn/20200712084149898.png)

- 直接寻址

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-gQcLsWey-1594166729717)(en-resource://database/615:1)]](https://img-blog.csdnimg.cn/202007120842023.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 隐含寻址

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-vjKyXlTs-1594166729718)(en-resource://database/616:1)]](https://img-blog.csdnimg.cn/20200712084211254.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

- 简介寻址

- 基址寻址

- 堆栈寻址

四、指令格式举例

1、设计指令格式时应考虑的各种因素

- 指令系统的兼容性

- 其他因素

操作类型 包括指令个数及操作的难易程度

数据类型 确定哪些数据类型可参与操作

指令格式 指令字长是否固定、操作码位数、是否采用扩展操作码技术;地址码位数、地址个数、寻址方式类型

寻址方式 指令寻址、操作数寻址

寄存器个数 寄存器的多少直接影响指令的执行时间

五、RISC技术

代办

八、CPU的结构和功能

1、CPU的结构

一、CPU的功能

- 控制器的功能

取指令 指令控制

分析指令

执行指令,发出各种操作命令 操作控制

控制程序输入及结果的输出 时间控制

总线管理 处理中断

处理异常情况和特殊请求 - 运算器的功能

实现算术运算和逻辑运算

二、CPU结构框图

- CPU与系统总线

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-is5fSxZb-1594166729719)(en-resource://database/617:1)]](https://img-blog.csdnimg.cn/20200712084228869.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

三、CPU的寄存器

- 用户可见寄存器

1、通用寄存器

2、数据寄存器

3、地址寄存器

4、条件码寄存器 - 控制和状态寄存器

1、控制寄存器

PC->MAR->M->MDR->IR

2、状态寄存器

状态寄存器 存放条件码

PSW寄存器 存放程序状态字 - 控制单元CU和中断系统

1、CU 产生全部指令的微操作命令序列

2、指令周期

网上学习资料一大堆,但如果学到的知识不成体系,遇到问题时只是浅尝辄止,不再深入研究,那么很难做到真正的技术提升。

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人,都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

aGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzMxMjE0Nzc5,size_16,color_FFFFFF,t_70)

三、CPU的寄存器

- 用户可见寄存器

1、通用寄存器

2、数据寄存器

3、地址寄存器

4、条件码寄存器 - 控制和状态寄存器

1、控制寄存器

PC->MAR->M->MDR->IR

2、状态寄存器

状态寄存器 存放条件码

PSW寄存器 存放程序状态字 - 控制单元CU和中断系统

1、CU 产生全部指令的微操作命令序列

2、指令周期

[外链图片转存中…(img-XwzpzWAI-1714986531488)]

[外链图片转存中…(img-OeHR0Q6D-1714986531489)]

网上学习资料一大堆,但如果学到的知识不成体系,遇到问题时只是浅尝辄止,不再深入研究,那么很难做到真正的技术提升。

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人,都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

321

321

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?