既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上Go语言开发知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

二、总线的连接方式

由于外设设备较多,且种类繁杂、速度各异,不能简单地把它们连到CPU上,因此必须寻找一种将外围设备同CPU连接起来的方法。这项工作一般都是由适配器部件来完成的,适配器通常也称为I/O接口。

根据连接方式不同,单处理机系统中采用的总线结构有两种:单总线结构和多总线结构。

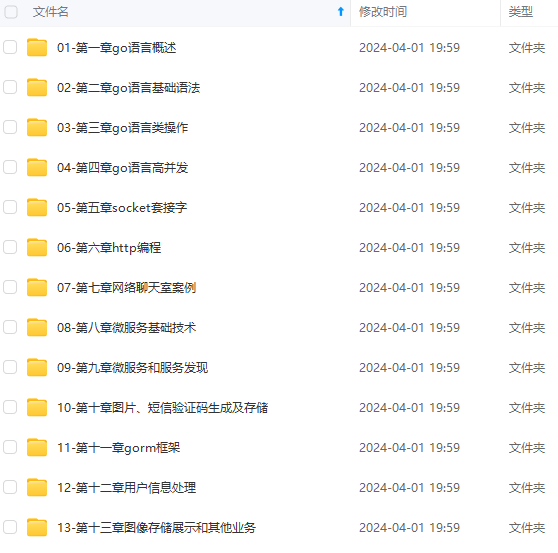

1. 单总线结构:

在许多单处理器的计算机中,使用单一的系统总线来连接CPU、主存和I/O设备,叫做单总线结构,允许I/O设备之间、I/O设备与CPU之间、I/O设备与主存之间直接交换信息。如下图所示:

这种结构简单,便于扩充,但缺点是所有的传送都通过这组共享的总线,因此极易形成计算机系统的瓶颈。

这类总线多数被小型计算机或微型计算机所使用。

2. 多总线结构:

多总线结构是CPU和cache之间采用高速的CPU总线。通过桥(具有缓冲、转换、控制功能的逻辑电路),CPU总线、系统总线和高速总线彼此相连。如下图所示:

多总线结构实现了高速、中速、低速设备同时连接到不同的总线上进行工作,极大地提高了总线的效率和吞吐量。

三、总线的内部结构

1. 早期:

早期的总线内部结构是处理器芯片引脚的延伸,是处理器与I/O设备适配器的通道,这种简单的总线一般也由50 —100条线组成。如下图所示:

这种总线结构的不足之处在于:

-

CPU总是唯一的主控者;

-

总线信号是CPU引脚信号的延伸,故总线结构与CPU紧密相关,通用性较差。

2. 当代:

当代流行的总线内部结构是一些标准总线,追求的是与硬件结构、CPU、技术无关的开发标准,并满足包括多个CPU在内的主控者环境的需求。如下图所示:

由上图可以看出,CPU和片内cache一起作为一个模块与总线相连。同时,在系统中允许有多个这样的处理器模块。而总线控制器完成几个总线请求者之间的协调与仲裁。

整个总线分成以下四个部分:

-

数据传送总线

由地址总线、数据总线、控制总线组成。为了减少布线,数据总线常常和地址总线采用多路复用的方式。 -

仲裁总线

包括总线请求线和总线授权线。 -

中断和同步总线

用于处理带优先级的中断操作,包括中断请求线和中断认可线。 -

公用线

包括时钟信号线、电源线、地线、系统复位线及加电或断电的时序信号线等。

大多数计算机采用了分层次的多总线结构。在这种结构中,速度差异较大的设备模块使用不用速度的总线,而速度相近的设备模块使用同一类总线。

四、总线的技术指标

总线的带宽指的是单位时间内总线上传送的数据量,即每秒钟传送MB的最大稳态数据传输率 [2] 。与总线密切相关的两个因素是总线的位宽和总线的工作频率,它们之间的关系:

总线的带宽=总线的工作频率*总线的位宽/8

或者 总线的带宽=(总线的位宽/8 )/总线周期

2、总线的位宽

总线的位宽指的是总线能同时传送的二进制数据的位数,或数据总线的位数,即32位、64位等总线宽度的概念。总线的位宽越宽,每秒钟数据传输率越大,总线的带宽越宽。

3、总线的工作频率

总线的工作时钟频率以MHZ为单位,工作频率越高,总线工作速度越快,总线带宽越宽。

五、总线的发展史

ISA总线

(Industry Standard Architecture)

⬇

PCI总线

(Peripheral Component Interconnect)

⬇

AGP 总线

(Accelerated Graphics Port)

⬇

PCI-Express

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上Go语言开发知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

]

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上Go语言开发知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

7697

7697

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?