目录

一、实验目的

1、掌握译码器的使用方法;

2、掌握译码器设计组合逻辑电路的方法

二、实验原理

中规模集成电路(MSI)是一种具有专门功能的集成功能件。常用的MSI组合功能件有译码器、编码器、数据选择器、数据比较器和全加器等。借助于器件手册提供的功能表弄清器件各引出端(特别是各控制输入端)的功能与作用,就能正确地使用这些器件。在此基础上应该尽可能地开发这些器件的功能,扩大其应用范围。对于一个逻辑设计者来说关键在于合理选用器件,灵活地使用器件的控制输入端,运用各种设计技巧,实现任务要求的电路功能。在使用 MSI组合功能件时,器件的各控制输入端必须按逻辑要求接入电路,不允许悬

空。

译码器

译码器可分为两大类,,一类是通用译码器,另一类是显示译码器(此类译码器参见附录三,本实验将不做讨论)。

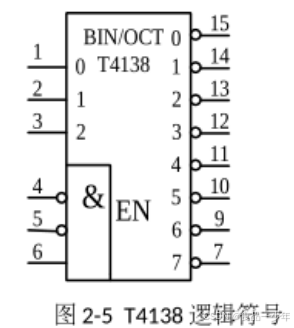

T4138是一个3线-8线译码器,它是一种通用译码器,其逻辑符号如图2-5所示,表22是其功能表。其中,A2、A、A是地址输入端,Y、Y、…、Y,是译码输出端,S,、S2、S是使能端,当S:=1S+S;=0时,器件使能。

3线-8线译码器实际上也是一个负脉冲输出的脉冲分配器。若利用使能端中的一个输入端输入数据信息,器件就是成为一个数据分配器。例如,若从s输入端输入数据信息,S,=S;=0,地址码所对应的输出是s,数据信息的反码;若从s,输入端输入数据信息S.=1 S=0地址码所对应的输出就是数据信息S2

译码器的每一路输出,实际上是地址码的一个最小项的反变量,利用其中一部分输出端输出的与非关系,也就蛇们相应最小项或逻辑表达式,能方便地实现逻辑函数。利用使能端能够方便地将两个3线-8线译码器组合成一个4线-16线的译码器。

三、实验任务

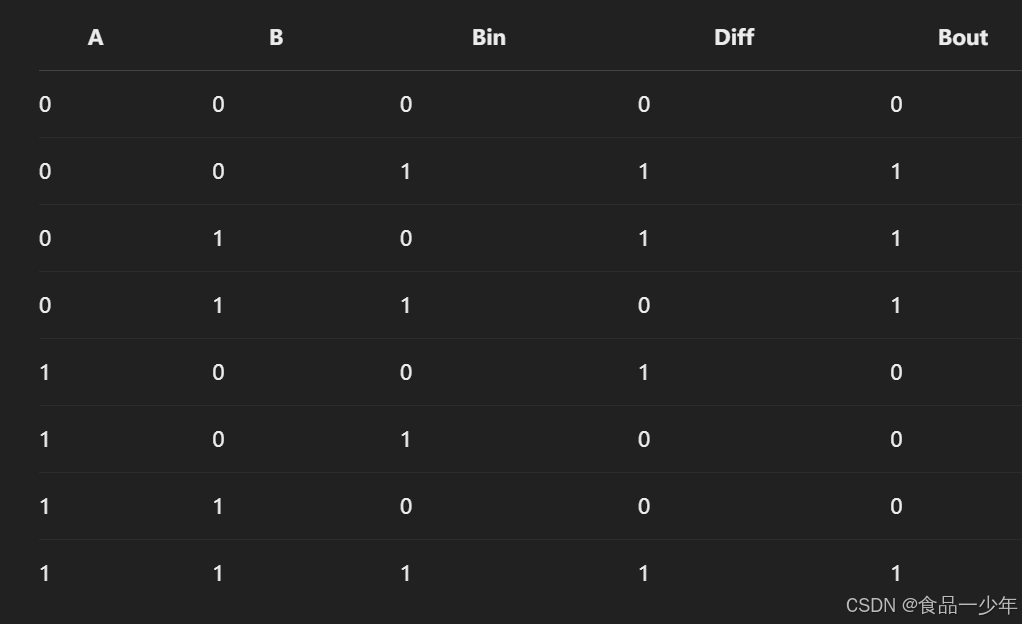

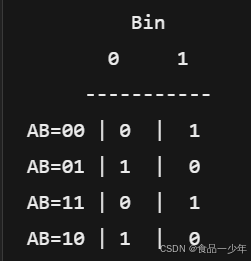

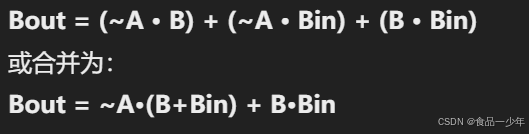

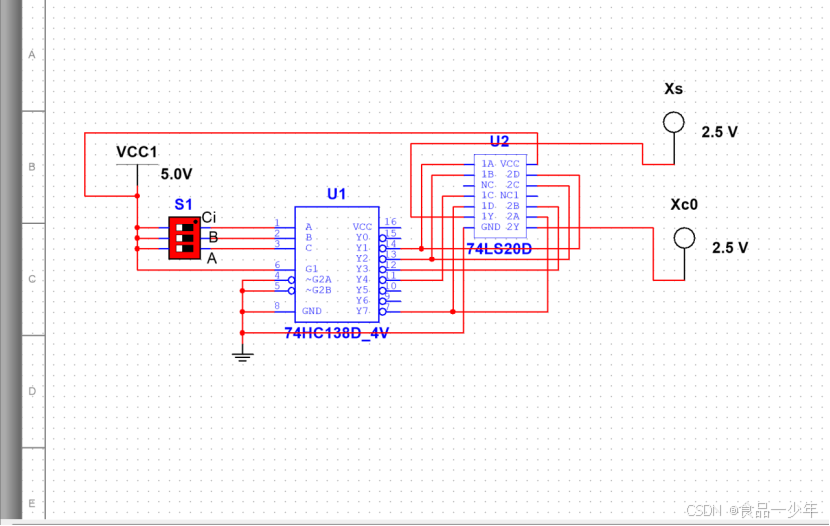

利用3线-8线译码器设计一个1位二进制全减器(可附加与非门)要求画出逻辑电路图,检测并记录电路功能。

四、实验设备与器材

1、主要集成电路:741381片;74201片。

2、multisim 仿真软件

真值表

卡诺图

![]()

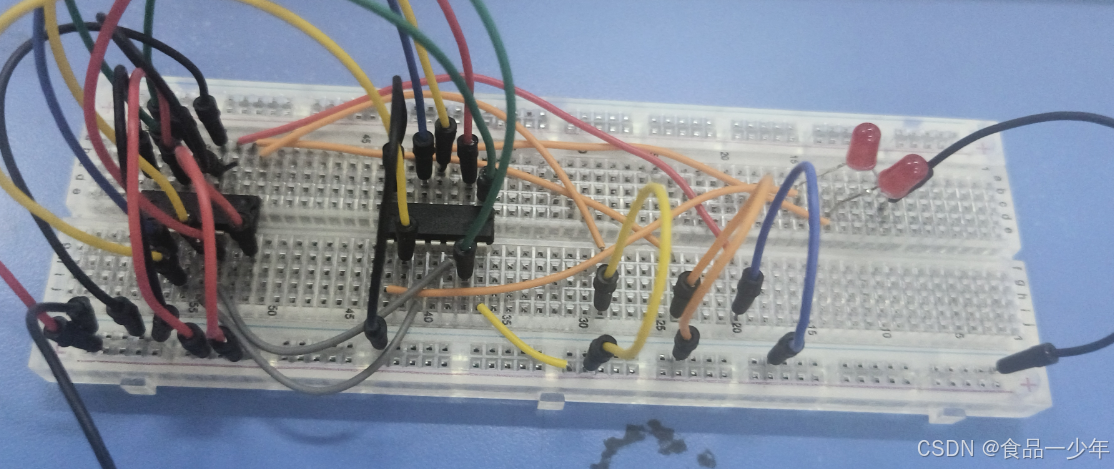

实物图

仿真电路

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?