目录

四、实验原理与设计过程(可介绍设计方法、设计过程、电路原理图要求手画)

五、实验方案(针对在实验室应进行的操作,包括芯片功能测试、电路搭建等)

六、结果预判(仿真,可利用字符发生器和逻辑分析仪进行输出验证。)

一、实验目的

1、掌握集成触发器的使用方法和逻辑功能的测试方法;

2、学习并掌握第一信号鉴别电路,又称作抢答器的设计方法。

二、实验任务

第一信号鉴别电路的工作原理

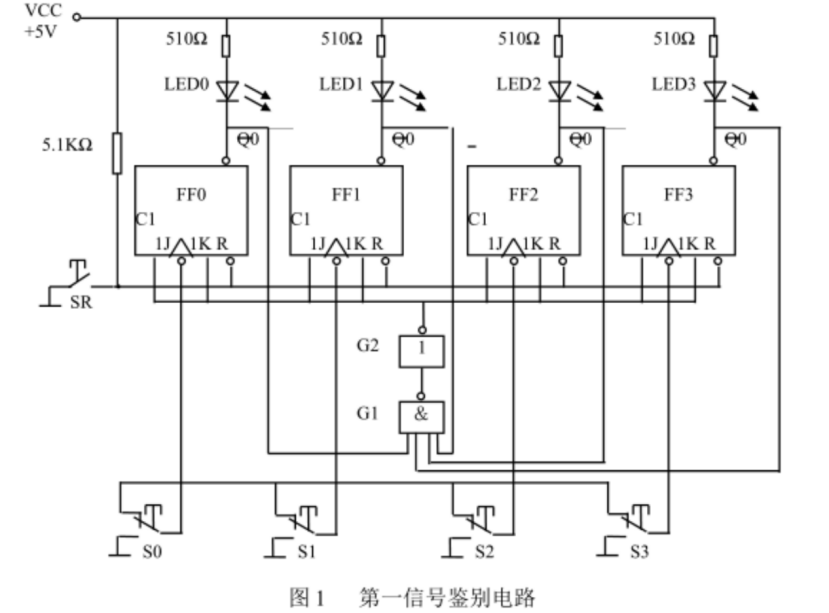

图1所示,为由4个JK触发器组成的第一信号鉴别电路,用以判别S0~S3;送入的4个信号中,哪一个信号最先到达,其工作过程如下:

开始工作前,先按复位开关SR,FF0~FF3,都被置0,Q0~Q3都输出高电平1,发光极管 LED0~LED3不发光。这时,G1输入都为高电平1,G2输出1,FF0~FF3,的J=K=1,这4个触发器处于接收输入信号的状态。在S0~S3的4个开关中,如S3第一个按下时,则FF3首先由0状态翻到1状态,~Q3=0,这一方面使发光二极管LED3发光,同时使G2输出0,这时 FF0~FF3的J和K都为低电子0,都执行保持功能。因此,在S3按下后,其它三个开关S0~S2,任一个再按下时,FF0~FF2的状态不会改变,仍为0状态,发光二极管LED0~LED2也不会亮,所以,根据发光二极管的发光可判断开关S3第一个按下。

如要重复进行第一信号判别时,则在每次进行判别前应先按复位开关Sr使FF0~FF3处于接收状态。图1所示电路又称作抢答器。

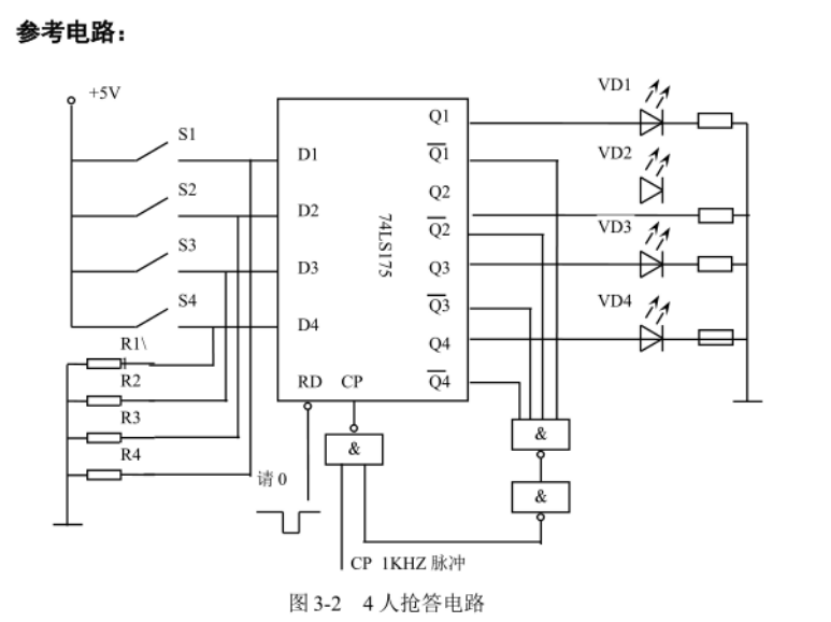

用D触发器和与非门设计智力竞赛4人抢答电路,设有4个开关(S0~S3),另有4个指示灯,第一抢答者(第一个按下开关时)所对应的指示灯亮,其它三个开关任一个再按下时,其它三个指示灯也不会亮。

三、实验设备与器材

1.硬木课堂

2.74LS000四2输入与非门一片

3.74LS020 双四输入与非门 一片

4.74LS074双上升沿D触发器两片

四、实验原理与设计过程(可介绍设计方法、设计过程、电路原理图要求手画)

1、设计方法

利用D触发器将“第一个抢答信号”锁存;

使用组合逻辑对触发器的触发条件进行控制,确保只能有一个输入有效;

LED用于输出状态指示,显示谁最先抢答。

该电路主要实现“第一信号鉴别”,即在四个输入(S6~S9)中,一旦有任意一路最先按下,该路输出锁存为高电平并点亮对应的指示灯,同时屏蔽其他输入,使其无法再触发输出。只有当按下“复位”按钮时,才能清除锁存状态,进入下一轮等待。

2、设计过程

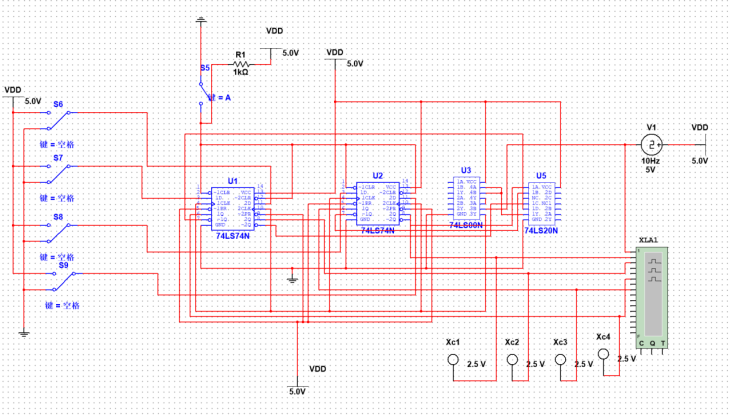

使用两片74LS074芯片提供4个D触发器,对应4个抢答输入(S6~S9);

每个抢答输入的按钮控制一个触发器的时钟信号C;

所有触发器的D端接高电平,使在C上升沿时Q输出为1;

使用与非门(74LS000或74LS20)构成“使能”信号,控制其它触发器时钟输入是否有效;

当某个触发器Q输出为1后,立即封锁其它触发器的时钟信号,使其它输入无效;LED显示抢答者。

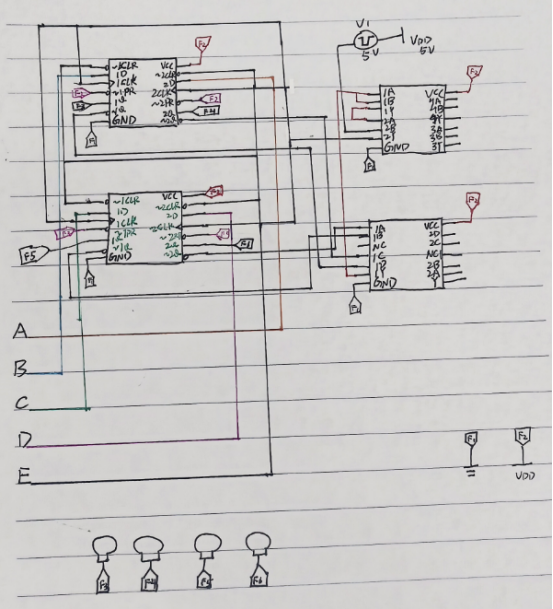

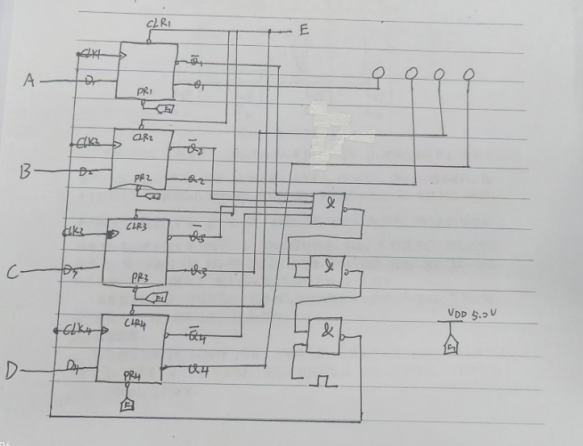

3、电路原理图

(1)、芯片连接图

(2)、逻辑原理图

五、实验方案(针对在实验室应进行的操作,包括芯片功能测试、电路搭建等)

1、芯片功能测试

使用逻辑笔或示波器验证74LS074触发器的D、C、CLR、Q逻辑功能;

使用简单的输入(高低电平)测试74LS000(2输入与非门)、74LS020(4输入与非门)的输出逻辑。

2、电路搭建步骤

在实验箱或面包板上摆放好 74LS74、74LS00/74LS20 芯片,注意给芯片正确供电 (VCC=5V)、接地;

将四个按键 S0~S3 分别接到 D 触发器的时钟端 (或经过与非门屏蔽后再接时钟端);

将 D 触发器的 D 输入统一接高电平 (5V);

将触发器 Q1~Q2 分别通过限流电阻接到对应 LED;

将所有 CLR 脚并联到一个复位按键 SR(或其他复位电路),松开复位时令 CLR=高电平(无效),按下时 CLR=低电平(有效复位);

将 Q0~Q3 或在一起(或通过与非门组合)生成屏蔽信号 E,用于其他按键路径的使能逻辑。

3、电路验证步骤

使用实验箱或仿真平台进行实际接线;

确保各芯片电源与GND连接正确;

复位按钮、抢答按钮、LED灯需提前调试好逻辑

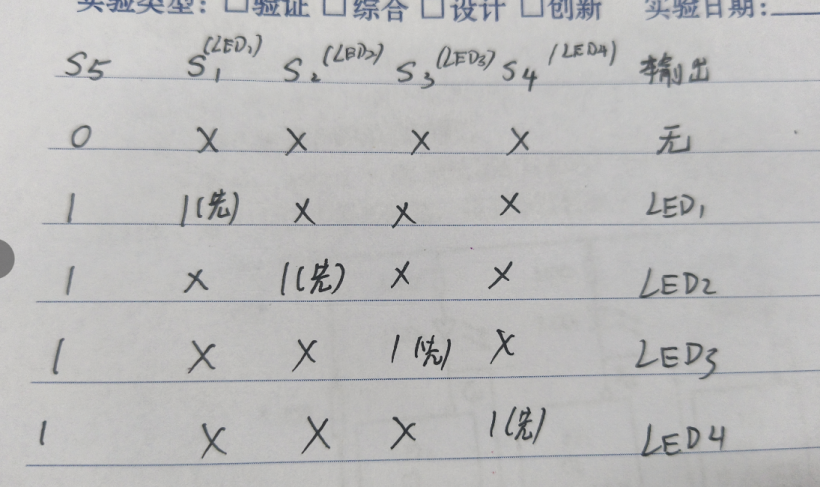

六、结果预判(仿真,可利用字符发生器和逻辑分析仪进行输出验证。)

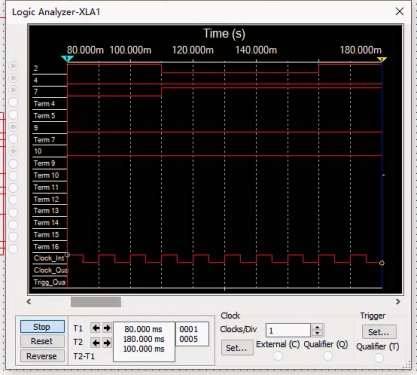

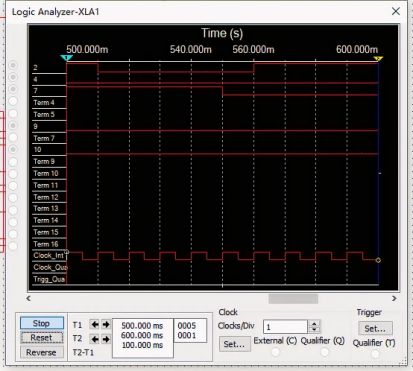

开关D打开:抢答成功变为高电平,过程中打开其他开关其他电平不会变化:

复位开关打开:所有电平复原:

.

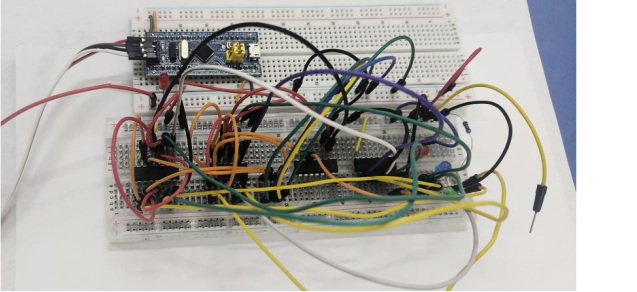

实物图

外挂了一个最小系统板输出pwm占空比为50%的方波3

七、实验总结

本次实验通过使用集成D触发器与与非门设计并实现了一个具有“第一信号锁存”功能的四人抢答电路。在设计过程中,深入理解了D触发器的锁存特性及其在同步电路中的应用,掌握了如何通过组合逻辑实现输入信号的优先判别与后续屏蔽。实验过程中,通过复位控制电路初始化状态,通过输入信号上升沿触发触发器状态变化,并利用组合逻辑对其它触发器进行屏蔽控制,实现了抢答者中第一个按键生效、其余无效的功能。仿真结果与预期一致,能够清晰反映系统的状态切换与逻辑正确性。通过本实验,不仅加深了对触发器工作原理的理解,同时也锻炼了综合使用基本逻辑器件进行中规模逻辑系统设计的能力,提升了电路分析、设计和验证的综合素质。

3610

3610

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?