既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

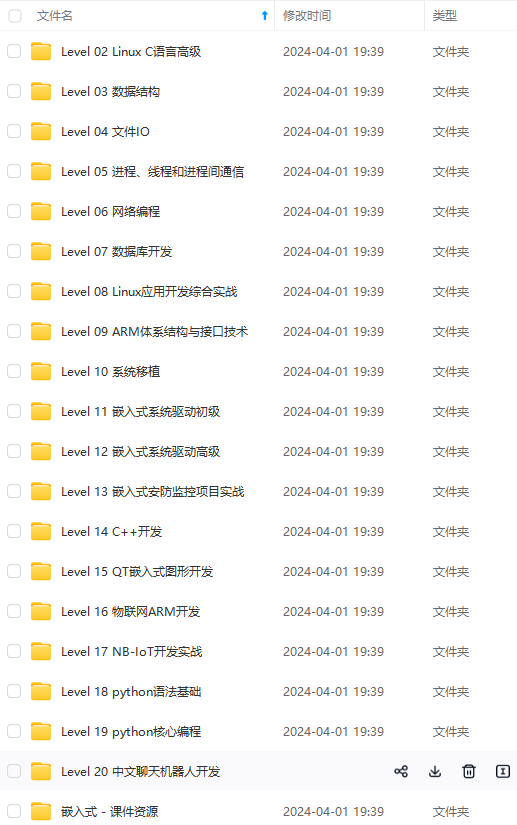

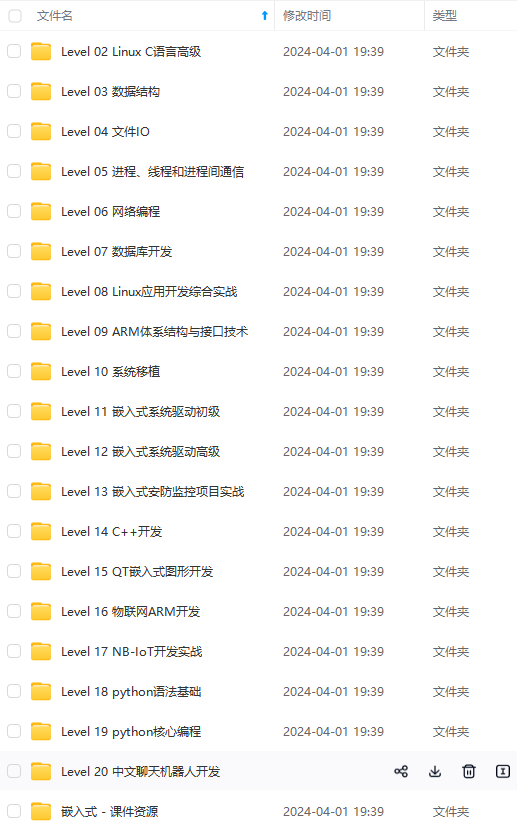

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

(二). ISE 工具栏_上半部分

建立完工程后,新建.v文件并添加进工程。如下图

下面开始介绍上半部分工具栏的功能。

如果要修改源文件顺序,如下

编译: 标号为1的是 全编译,即从头开始编译,而有的时候我们只修改了一小部分代码,所以编译的时候不用全编译,就用标号2的 SmartGuide

SmartGuide 这个ISE中的全局优化选项,使能这个选项,编译器在Implementation时会比较前一次编译的Implementation结果,未修改部分则沿用前一次的结果,但是如果时序比较紧张,会根据情况重新实现相应未修改部分来达到时序要求。

设计属性 可以重新对工程属性进行编辑。如下图

(三). ISE 工具栏_下半部分

Create Schematic Symbol:将当前源文件创建成一个原理图模块,可以被其他原理图模块调用。如图 View HDL Instantiation Template:查看当前源文件HDL例化模板,生成之后,其他工程可以直接调用这个模块,是很常用的功能。

View HDL Instantiation Template:查看当前源文件HDL例化模板,生成之后,其他工程可以直接调用这个模块,是很常用的功能。

1. Synthesize

View RTL Schematic:查看 RTL 视图,一般点击的选项,直接生成图片,如下

2. Implement Design

综合完之后,就对工程进行编译等

Map:映射;

Place&Route:布局布线;

3. 创建UCF文件

Create Timing Constraints:创建时序约束文件(UCF 文件),一般用new_Source创建UCF约束文件,然后用这个运行

run完之后的效果如下图

I/O Pin Planning (PlanAhead) - Pre-Synthesis:一般不用这个,而是直接用UCF写代码。运行效果如下图:

二、ISE软件仿真

1.创建tb文件

2.编写代码

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

以下为源程序代码

module flow\_led(

input sys_clk , //系统时钟

input sys_rst_n, //系统复位,低电平有效

output reg [3:0] led //4个LED灯

);

而由源程序代码编写tb文件;input——>reg代替,output由wire代替

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

`timescale 1ns / 1ps //仿真的 时间单位/时间精度

module flow_led_tb;

//input——>reg代替,output由wire代替

// Inputs

reg sys_clk;

reg sys_rst_n;

// Outputs

wire [3:0] led;

//创建激励

// Instantiate the Unit Under Test (UUT)

flow_led uut (

.sys\_clk(sys_clk),

.sys\_rst\_n(sys_rst_n),

.led(led)

);

//初始化语句,只执行一次

initial begin

// Initialize Inputs

sys_clk = 0;

sys_rst_n = 0;

//等待100个时间单位,即100个1ns

// Wait 100 ns for global reset to finish

#100;

sys_rst_n = 1;//等待100ns之后,把复位信号拉高,不再复位

// Add stimulus here

end

//接下来给流水灯的时钟

//因为开发板的时钟是50MHz的,所以时钟周期为20ns,此处让时钟信号每10ns翻转一次,那完整的周期就是20ns,实现了模拟时钟周期的功能。

always#10 sys_clk = ~sys_clk;

endmodule

然后运行,可以看到如下图

额,其实这里出现过一个bug,如下图,

整了好一会,最后错误出现在我仿真的时候选错了文件,选成了下面的设计文件,应该选上面的tb文件才对

工具栏使用

1.运行方式

左边箭头为连续运行,右边箭头为步进运行,运行时间为后面的数字所示的时间。

2.移动光标

(黄线)在name先选择,然后没点击一次,黄线就会换一个节点;图示为在sys_clk上的

ISE与notepad++关联

edit——preference——Editors——custom——notepad++安装路径

注意在路径的首尾添加大括号 { }再加1个空格,之后输入 $1

(注意把路径中的右斜杠 \ 改成左斜杠 / ) 之后apply即可

在notepad++中修改代码后必须保存之后再到ISE中编译才有效!!

三、ISE生成bit流文件

点击Generate Programming File即可

下载bit流文件

点击Configure Target Device,在弹出的界面点击Boundary Scan再点击这个绿色的按钮

这个弹窗是为了让我们添加下载文件的,Yes之后添加bit流文件

添加完bit文件后,此弹窗是为了让我们生成固化文件,此处先不生成。点击No

下一个弹窗是为了让我们确认,点击OK。最后,双击program即可

四、ISE下载固化文件

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新**

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

1291

1291

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?