开始

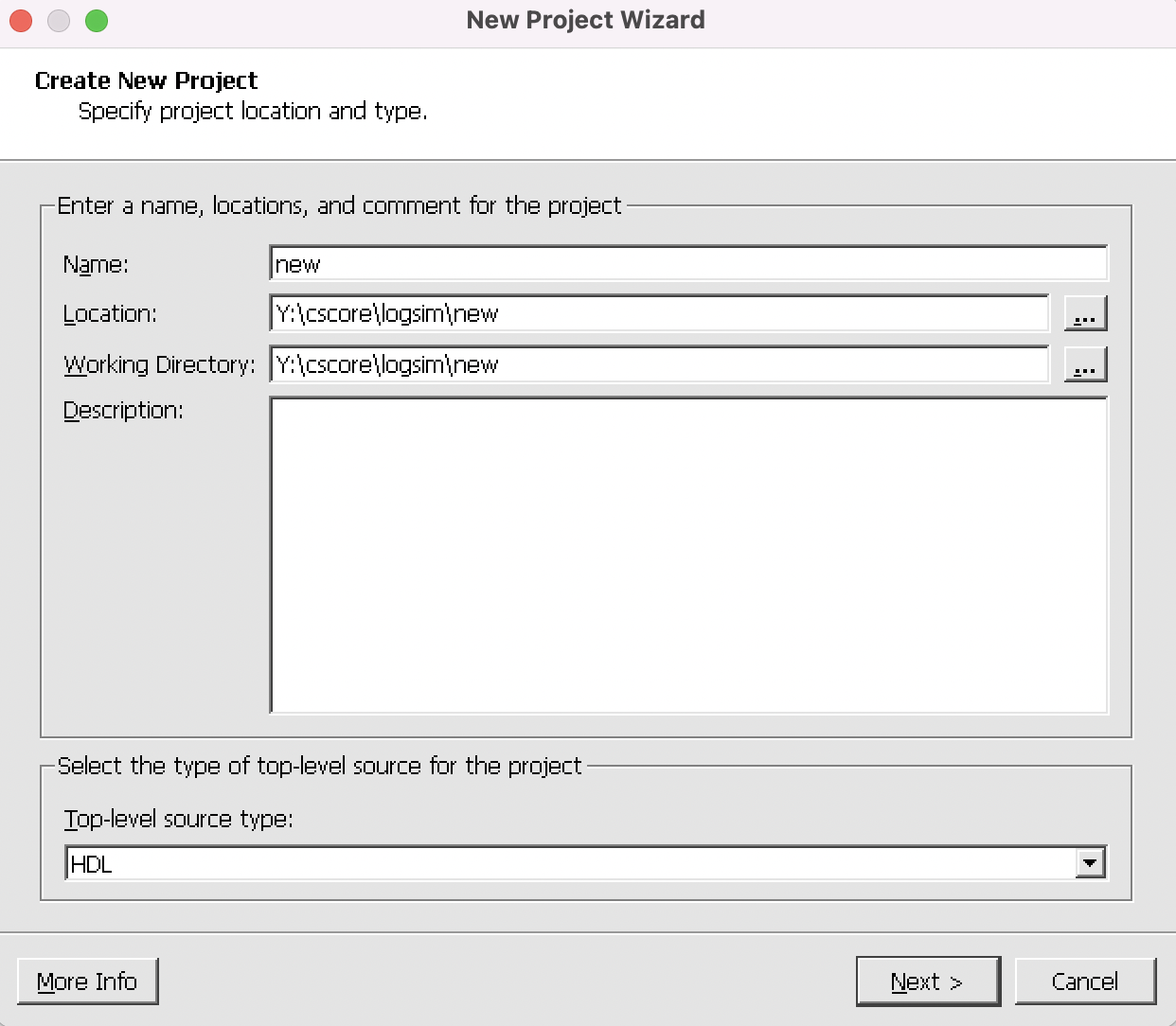

新建一个工程

File - New project

-

命名与保存位置

>> Next

-

工程设置

Project Category: All

Family: 选择所使用的fpga类型

Device: 选择所使用的fpga具体型号

Synthesis Tool: 选择所使用的综合工具(默认ISE自带XST)

Simulator: 选择仿真软件(默认ISE自带Isim)

Preferred Language: 选择所使用的硬件语言(Verilog)

VHDL Source Analysis Standard: WHDI-93

>> Next

-

工程综述

>>Finish

设计输入输出

-

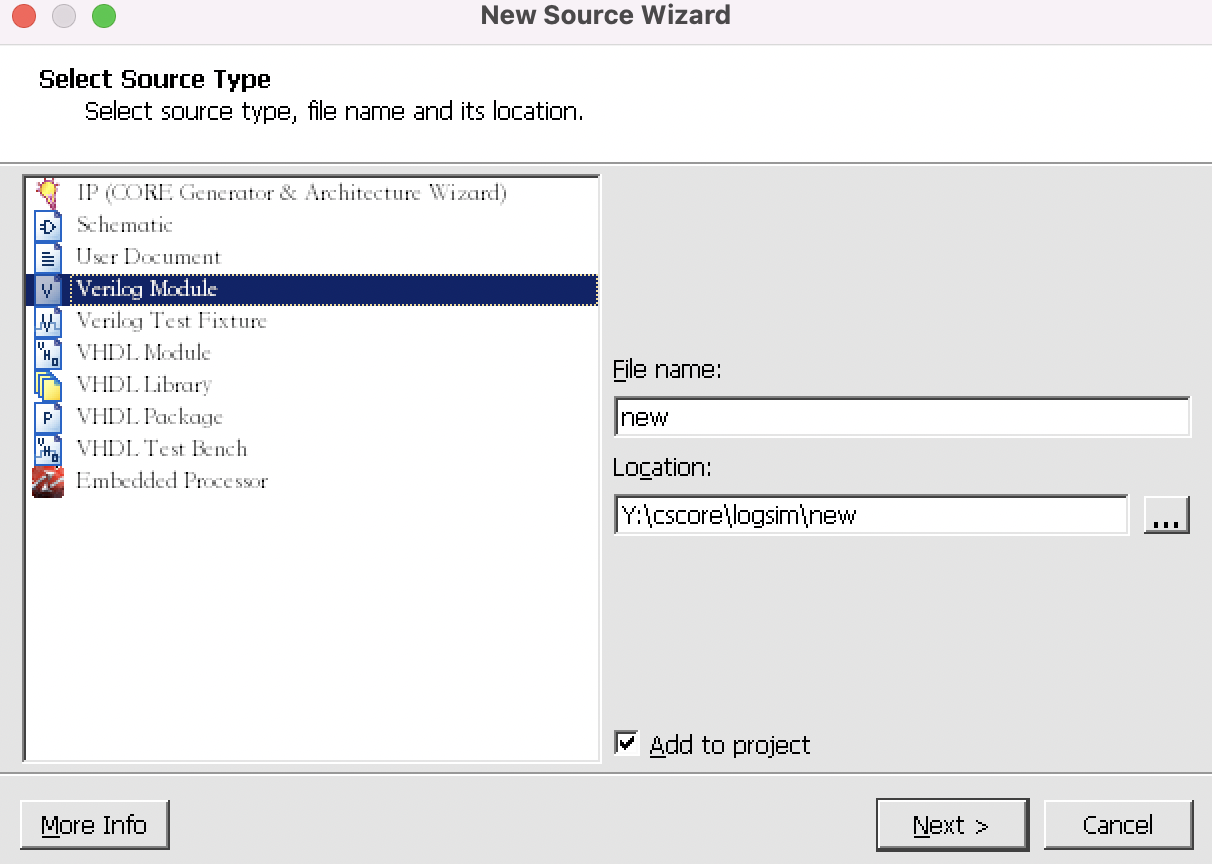

工程管理区任意位置 - 右键 - new source 或者 点击左侧的按钮(如图)

-

向导对话框

选择Verilog Module

(视频 [ 0:30 ] 有对每一项的详细说明)

> > Next

-

模块定义对话框

ModuleNamep 模块名 Port Name 端口名 Directiona 端口方向 [ input / output / inout ] Bus 不勾选表示该端口为一位信号,勾选表示该端口为多位信号 MSBe 信号最高位 LSBe 信号最低位

>>next

-

综述

>> finish

-

自动创建verilog模块的例子,在代码编辑区域打开

自动生成 模块和端口定义

-

点击工具栏 保存

生成仿真模板文件

新建测试模块:工程管理视窗单击右键 -> New source -> Verilog Test Fixture

在自动生成的文件中编写测试代码, 工程管理视窗选择 Simulation,双击下方 Behavioral Check Syntax,检查通过后,再双击 Simulate Behavioral Model 即可使用 ISim 进行仿真。

(待整理更新)

参考:https://blog.csdn.net/su1041168096/article/details/81449564

5864

5864

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?