既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

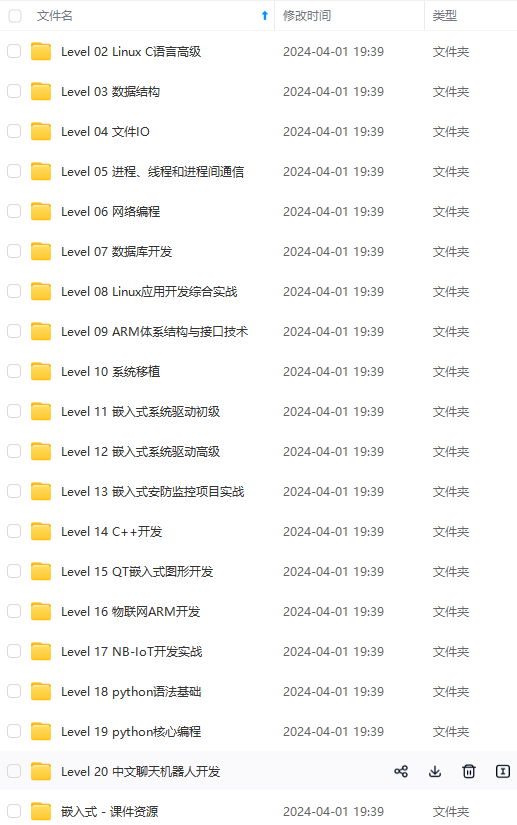

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

1.2 PCI总线的信号定义

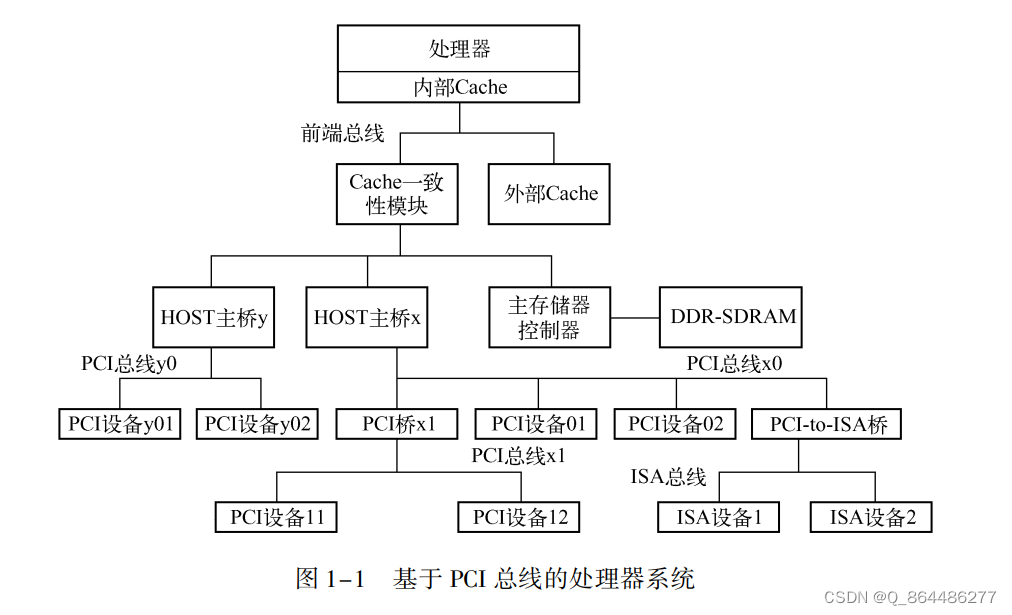

PCI 总线是一条共享总线, 在一条 PCI 总线上可以挂接多个 PCI 设备。 这些 PCI 设备通 过一系列信号与 PCI 总线相连, 这些信号由地址/ 数据信号、 控制信号、 仲裁信号、 中断信 号等多种信号组成。

PCI 总线可以使用33 MHz 或者66 MHz 的时钟频率, 而 PCI⁃X 总线可以使用 133 MHz、 266 MHz 或者 533 MHz 的时钟频率。

除了 RST#、 INTA ~ D#、 PME#和 CLKRUN#等信号之外, PCI 设备使用的绝大多数信号 都使用这个 CLK 信号进行同步。 其中 RST#是复位信号, 而 PCI 设备使用 INTA ~ D#信号进 行中断请求。 本书并不详细介绍 PME#和 CLKRUN#信号。

1.2.1 地址和数据信号

(1) AD[31∶0]信号

PCI 总线复用地址与数据信号。第一个时钟传送地址,后面传数据,支持突发传送

(2) PAR 信号

PAR 信号是 AD[31∶ 0]和 C / BE[3∶ 0]的奇偶校验信号。

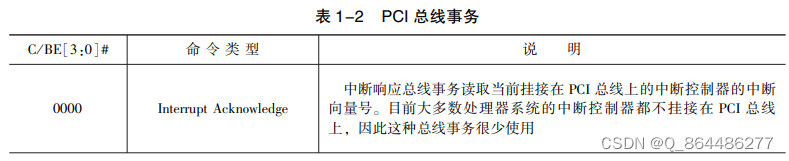

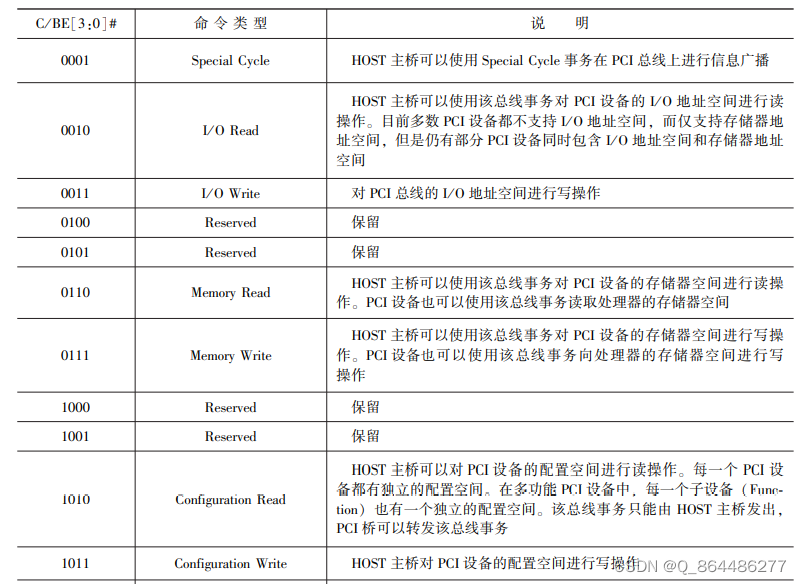

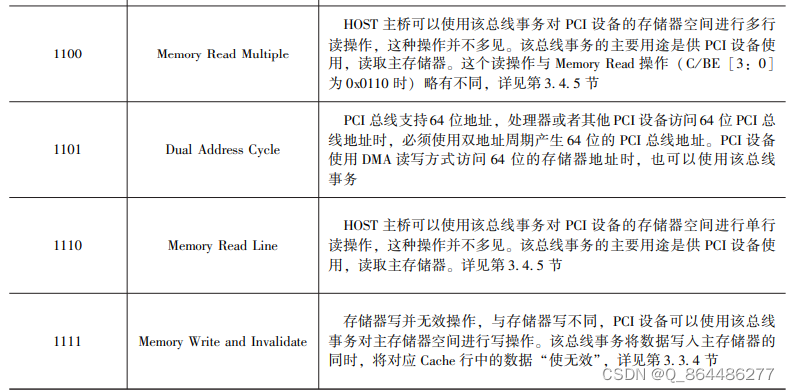

(3) C / BE[3∶0] #信号

1.2.2 接口控制信号

(1) FRAME#信号

该信号指示一个 PCI 总线事务的开始与结束。低电平有效,高电平无效。

(2) IRDY#信号

如果当前 PCI 总线事务为写事务, 表示数据已经在 AD[31∶ 0]上有效; 如果为读事 务, 表示 PCI 目标设备已经准备好接收缓冲, 目标设备可以将数据发送到 AD[31∶ 0]上。

(3) TRDY#信号

如果当前 PCI 总线事务为写事务, 表示目标设备已经准备好接收缓冲, 可以将 AD[31∶ 0]上的数据写 入目标设备; 如果为读事务, 表示 PCI 设备需要的数据已经在 AD[31∶ 0]上有效。

(4) STOP#信号

该信号有效时表示目标设备请求主设备停止当前 PCI 总线事务。

(5) IDSEL 信号

PCI 总线在进行配置读写总线事务时, 使用该信号选择 PCI 目标设备。

(6) DEVSEL#信号

该信号有效时表示 PCI 总线的目标设备准备好, 该信号与 TRDY#信号的不同之处在于 该信号有效仅表示目标设备已经完成了地址译码。 目标设备使用该信号通知 PCI 主设备, 其 访问对象在当前 PCI 总线上, 但是并不表示目标设备可以与主设备进行数据交换。 而 TRDY# 信号表示数据有效, PCI 主设备可以向目标设备写入或者从目标设备读取数据。 11 PCI 总线规范根据设备的译码速度, 将 PCI 设备分为快速、 中速和慢速三种。 在 PCI 总 线上还有一种特殊的设备, 即负向译码设备, 在一条 PCI 总线上当快速、 中速和慢速三种设 备都不能响应 PCI 总线事务的地址时, 负向译码设备将被动地接收这个 PCI 总线事务。 如果 在 PCI 主设备访问的 PCI 总线上, 没有任何设备可以置 DEVSEL#信号为有效, 主设备将使 用 Master Abort 周期结束当前总线事务。

(7) LOCK#信号

PCI 主设备可以使用该信号, 将目标设备的某个存储器或者 I / O 资源锁定, 以禁止其他 PCI 主设备访问此资源, 直到锁定这个资源的主设备将其释放。PCI 总线使用 LOCK#信号实 现 LOCK 总线事务, 只有 HOST 主桥、 PCI 桥或者其他桥片可以使用 LOCK#信号。

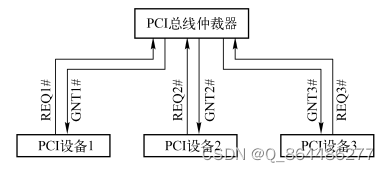

1.2.3 仲裁信号

在一棵 PCI 总线树中, 每一条 PCI 总线上都有一个总线仲裁器。 一个处理器系统可以使 用 PCI 桥扩展出一条新的 PCI 总线, 这条新的 PCI 总线也需要一个总线仲裁器, 通常在 PCI 桥中集成了这个总线仲裁器。 多数 HOST 主桥也集成了一个 PCI 总线仲裁器, 但是 PCI 总线 也可以使用独立的 PCI 总线仲裁器。 PCI 主设备使用 PCI 总线进行数据传递时, 需要首先置 REQ#信号有效, 向 PCI 总线仲裁 器发出总线申请, 当 PCI 总线仲裁器允许 PCI 主设备获得 PCI 总线的使用权后, 将置 GNT#信 号为有效, 并将其发送给指定的 PCI 主设备。 而 PCI 主设备在获得总线使用权之后, 将可以置 FRAME#信号有效, 与 PCI 从设备进行数据通信。

1.2.4 中断请求等其他信号

PCI 总线提供了 INTA#、 INTB#、 INTC#和 INTD#四个中断请求信号。信号置低表示向处理器请求中断,处理器执行完毕后,将中断信号置高。

PCI 总线规定单功能设备只能使用 INTA#信号, 而多功能设备才能使用 INTB# / C# / D# 信号。PCI 总线在进行数据传递过程时, 难免会出现各种各样的错误, 因此 PCI 总线提供了一 些错误信号, 如 PERR#和 SERR#信号。 其中当 PERR#信号有效时, 表示数据传送过程中出 现奇偶校验错( Special Cycle 周期除外) ; 而当 SERR#信号有效时, 表示当前处理器系统出 现了三种错误可能, 分别为地址奇偶校验错、 在 Special Cycle 周期中出现数据奇偶校验错、 系统出现其他严重错误。如果 PCI 总线支持 64 位模式, 还需要提供 AD[63∶ 32] 、 C / BE[7∶ 4] 、 REQ64、 ACK64 和 PAR64 这些信号。

1.3 PCI 总线的存储器读写总线事务

总线的基本任务是实现数据传送, 将一组数据从一个设备传送到另一个设备。PCI 总线支持以下几类存储器读写总线事务。

(1) HOST 处理器对 PCI 设备的 BAR 空间进行数据读写, BAR 空间可以使用存储器或 者 I / O 译码方式。 HOST 处理器使用 PCI 总线的存储器读写总线事务和 I / O 读写总线事务访 问 PCI 设备的 BAR 空间。 (2) PCI 设备之间的数据传递。 在 PCI 总线上的两个设备可以直接通信, 如一个 PCI 设 备可以访问另外一个设备的 BAR 空间。 不过这种数据传递在 PC 处理器系统中较少使用。 (3) PCI 设备对主存储器进行读写, 即 DMA 读写操作。 DMA 读写操作在所有处理器系 统中都较为常用, 也是 PCI 总线数据传送的重点。 在多数情况下, DMA 读写操作结束后将 伴随着中断的产生。 PCI 设备可以使用 INTA#、 INTB#、 INTC#和 INTD#信号提交中断请求, 也可以使用 MSI 机制提交中断请求。

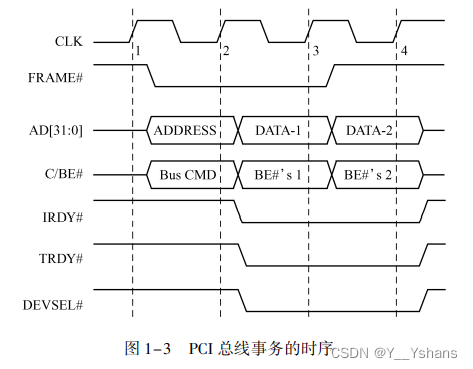

1.3.1 PCI 总线事务的时序

与 PCI 总线事务相关的控制信号有 FRAME#、 IRDY#、 TRDY#、 DEVSEL#等其他信号。

当PCI设备需要使用PCI总线的时候,先发送请求REQ#,通过仲裁,返回GNT#信号。PCI设备获得控制权后,FRAME#置为有效,总线事务结束后, FRAME#信号将被置为无效。PCI 主设备将访问的目的地址和总线命令分别驱动到 AD[31∶ 0]和 C / BE#信号上。 如果当前总线命令是配置读写, 那么 IDSEL 信号线也被置为有效。当 IRDY#、 TRDY#和 DEVSEL#信号都有效后, 总线事务将使用数据周期进行数据 传递。 当 IRDY#和 TRDY#信号没有同时有效时, PCI 总线不能进行数据传递, PCI 总线使用 这两个信号进行传送控制。

1.3.2 Posted 和 Non⁃Posted 传送方式

PCI 总线规定了两类数据传送方式, 分别是 Posted 和 Non⁃Posted 数据传送方式。

其中 Posted 总线事务指 PCI 主设备向 PCI 目标设备进行数据传递时, 当数据到达 PCI 桥 后, 即由 PCI 桥接管来自上游总线的总线事务, 并将其转发到下游总线。 采用这种数据传送 方式, 在数据还没有到达最终的目的地之前, PCI 总线就可以结束当前总线事务, 从而在一 定程度上解决了 PCI 总线的拥塞问题。

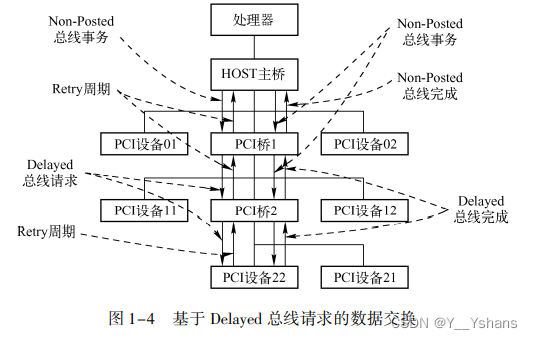

而 Non⁃Posted 总线事务是指 PCI 主设备向 PCI 目标设备进行数据传递时, 数据必须到达 最终目的地之后, 才能结束当前总线事务的一种数据传递方式。这种事务方式会造成一定的拥塞,因此 PCI 总线使用 Delayed 总线 事务处理 Non⁃Posted 数据请求。

PCI 总线规定只有存储器写请求 (包括存储器写并无效请求) 可以采用 Posted 总线事务;而存储器读请求、 I / O 读写请求、 配置读写请求只能采用 Non⁃Posted 总线事务。

拿图1-1举例说明posted请求

设备11需要进行DMA操作写数据到DDR,那么它会先向PCI桥x1发送请求,桥1接收后会释放x1总线的控制,此时11和12可以正常通信。同理,桥x1会将请求传给HOST主桥x,主桥x会传给控制器。这种逐级释放总线资源,使得PCI 总线的利用率较高。Non⁃ Posted 数据请求在通过 PCI 总线时, 并不会及时释放总线资源, 从而在某种程度上影响 PCI 总线的使用效率和传送带宽。

1.3.3 HOST 处理器访问 PCI 设备

PCI 设备能够直接使用的地址是 PCI 总线域的地址,而处理器能够直接使用的地址是存储器域的地址。

这里说一下处理器与设备11的通信步骤

其实就是处理器将数据写入寄存器中,先访问存储器域地址,经过HOST主桥转换地址 变成PCI地址,发送事务到PCI桥x1,x1释放总线。后面过程同理,最后 PCI 设备 11 通过地址译码方式接收这个写总线事务。

1. 3. 4 PCI 设备读写主存储器

根据1.3.3 同理

1. 3. 5 Delayed 传送方式

主要是优化Non⁃ Posted

PCI⁃X 总线将 PCI 总线使用的 Delayed 总线事务, 升级为 Split 总线事务。 采用 Split 总线事务可以有效解决 HOST / PCI 桥的这些重 试操作。 Split 总线事务的基本思想是发送端首先将 Non⁃Posted 总线请求发送给接收端, 然 后再由接收端主动地将数据传递给发送端。

1. 4 PCI 总线的中断机制

PCI 总线使用 INTA#、 INTB#、 INTC#和 INTD#信号向处理器发出中断请求。

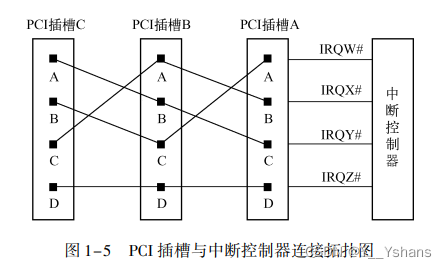

1. 4. 1 中断信号与中断控制器的连接关系

图 1-5 所示的拓扑结构时, PCI 插槽 A、 B、 C 的 INTA#、 INTB#和 INTC#信号将分 散连接到中断控制器的 IRQW#、 IRQX#和 IRQY#信号, 而所有 INTD#信号将共享一个 IRQZ# 信号。 采用这种连接方式时, 整个处理器系统使用的中断请求信号, 其负载较为均衡。 而且 这种连接方式保证了每一个插槽的 INTA#信号都与一根独立的 IRQx#信号对应, 从而提高了 PCI 插槽中断请求的效率。

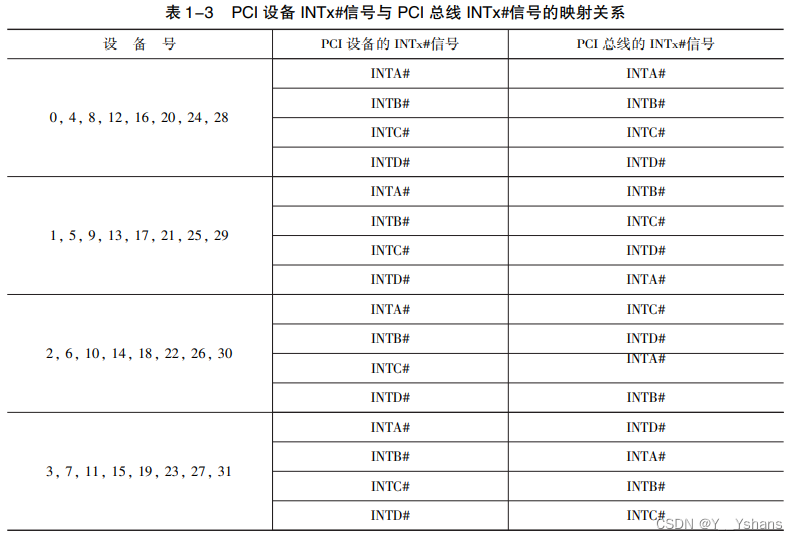

1. 4. 2 中断信号与 PCI 总线的连接关系

1. 4. 3 中断请求的同步

中断遇到的问题在于,比如DMA最后一个数据向目的地传输,此时中断也产生了,中断直接作用于处理器,但是很有可能数据还没有传到目的地。所以解决方法有,传输完全结束后,给中断信号到处理器,这种占用资源。还有一种是DMA传送结束后,处理器请求存储器的某一种类信号,这个信号代表结束信号,这样就比较方便。

MSI中断机制在第十章提及

1. 5 PCI⁃X 总线简介

PCI⁃X 总线仍采用并行总线技术。 PCI⁃X 总线使用的大多数总线事务基于 PCI 总线, 但 是在实现细节上略有不同。 PCI⁃X 总线将工作频率提高到 533 MHz, 并首先引入了 PME (Power Management Event) 机制。 除此之外, PCI⁃X 总线还提出了许多新的特性。

1. 5. 1 Split 总线事务

代替了delay总线,提高了Non⁃Posted 总线事务的传送效率。

与 Delayed 总线事务相比, Requester 获得的数据是 Completer 将数据完全准备好后, 由 Completer 主动传递的, 而不是通过 Requester 通过多次重试获得的, 因此能够提高 PCI⁃X 总 线的使用效率。 PCI⁃X 总线提出的 Split 总线事务被 PCIe 总线继承。

1. 5. 2 总线传送协议

PCI⁃X 总线改变了 PCI 总线使用的传送协议。 目标设备可以将主设备发送的命令锁存, 然后在下一个时钟周期进行译码操作。 与 PCI 总线事务相比, PCI⁃X 总线采用的这种方式, 虽然在总线时序中多使用了一个时钟周期, 但是可以有效提高 PCI⁃X 总线的运行频率。

因为主设备通过数据线将命令发送到目标设备需要一定的延时。 如果 PCI 总线频率较 高, 目标设备很难在一个时钟周期内接收完毕总线命令, 并同时完成译码工作。 而如果目标 设备能够将主设备发出的命令先进行锁存, 然后在下一个时钟周期进行译码则可以有效解决 这个译码时间 Margin 不足的问题, 从而提高 PCI⁃X 总线的频率。

1. 5. 3 基于数据块的突发传送

在 PCI 总线中, 数据发送端知道究竟需要发送多 少字节的数据, 但是接收端并不清楚到底需要接收多少数据。 这种不确定性, 为接收端的缓 冲管理带来了较大的挑战。 为此 PCI⁃X 总线使用基于数据块的突发传送方式, 发送端以 ADB (Allowable Disconnect Boundary) 为单位, 将数据发送给接收端, 一次突发读写为一个以上的 ADB。 采用这种方 式, 接收端可以事先预知是否有足够的接收缓冲, 接收来自发送端的数据, 从而可以及时断 连当前总线周期, 以节约 PCI⁃X 总线的带宽。

总结

本章主要介绍了 PCI 总线的基本组成部件,PCI 设备如何提交中断请求,以及 PCI⁃X 总 线对 PCI 总线的功能增强。 本章的重点在于 PCI 总线的 Posted 和 Non⁃Posted 总线事务,以及 PCI 总线如何使用 Delayed 传送方式处理 Non⁃Posted 总线事务,请读者务必深入理解这两种 总线事务的不同。

参考文章:

PCIe总线学习笔记(一、PCI基础知识简介)(转载) - 爱码网

PCI_Express_体系结构导读——王齐

一文讲述,什么是pci总线原理?_csbmww的博客-CSDN博客_pci原理图

pci总线结构学习树形结构_iN651的博客-CSDN博客_lspci查看pci树形结构

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

34217)]

[外链图片转存中…(img-Mxpgd3GX-1715892934217)]

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

1837

1837

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?