1、3 AHB和AXI突发传输的对比

- 1、

AHB:需要一次Burst传输的所有地址、地址与数据锁定对应关系、后一次突发传输必须等待前次传输完成; - 2、

AXI:只需要首地址、可以连续发送多个突发传输首地址而无需等待前次突发传输完成、两次传输的数据可以交错传递、大大提高了总线的利用率!!!!! - 3、AHB Burst传输只有八种模式:

single、INCR、INCR4、WRAP4、INCR8、WRAP8、INCR16、WRAP16 - 4、AXI Burst传输

可以指定传输数据的个数:1-16

SoC系统中,均以AXI总线为主总线,通过桥连接AHB总线与APB总线,这样能够增加SoC系统的灵活性,更加合理地把不同特征IP分配到总线:

- AHB总线与AXI总线均适用于高性能、高带宽的SoC系统,但AXI具有更好的灵活性,而且能够读写通道并行发送,互不影响;

- AXI总线支持乱序传输,能够有效地利用总线的带宽,平衡内部系统。

二、AXI 概述

2、1 AXI总线、接口、协议(AXI4、AXI4-Lite与AXI4-Stream区别与联系)

- 1、总线、接口和协议常常放在一起,但是他们有各自的含义:

- ①、总线:一组由各种逻辑器件构成的数据传输通道,一般由

数据线、地址线、控制线等构成; - ②、接口:一种连接标准,又常常被称为物理接口;

- ③、协议:传输数据的规则

- ①、总线:一组由各种逻辑器件构成的数据传输通道,一般由

- 2、AXI总线分为:AXI4、AXI4-Lite、AXI4-Stream

- ①、

AXI4:(For high-performance memory-mapped requirements.)主要面向高性能内存映射通信的需求(如读写DDR、使用BRAM控制器读写BRAM等),是面向内存映射的接口,允许最大256个数据突发传输; - ②、

AXI4-Lite:(For simple, low-throughput memory-mapped communication )用于简单、低吞吐量的内存映射通信(例如,与控制寄存器和状态寄存器之间的通信),占用很少的逻辑单元;- AXI4-Lite 是 AXI4 的删减版,适合轻量级的应用,也是包含 5 个通道,不同的是每个通道都进行了简化,去掉了对突发传输的支持(Burst),只允许每个transfer传输一个数据。

- ③、

AXI4-Stream:(For high-speed streaming data.)面向高速流数据传输(视频、图像等流式数据);去掉了地址项,允许无限制的数据突发传输规模。- AXI4-Stream为流数据的传输定义了单个通道;

- 允许无限制的数据突发传输

- ④、AXI4、AXI4-Lite与AXI4-Stream的共同点:

- 均使用Ready、Valid握手机制进行通信。

- ①、

- 3、AXI接口:

- AXI-GP接口(4个):是通用的AXI接口;

- AXI-HP接口(4个):是高性能/带宽的标准的接口;

- AXI-ACP接口(1个):是ARM多核架构下定义的一种接口。

- 4、AXI协议:AXI4,AXI4-Lite,AXI4-Stream都是AXI4协议

,细节上略微有差别。

2、2 AXI协议特点:

- 五个独立的地址读写、数据读写、写操作响应通道

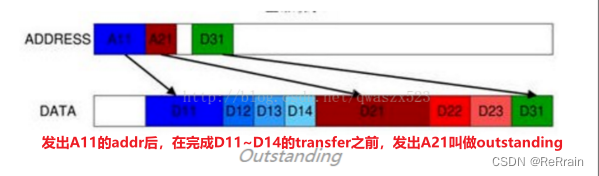

- 支持发出多个未完成地址(outstanding addresses):可连续发出传输地址,无需等待前次传输完成

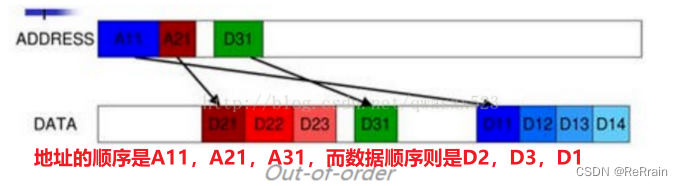

- 支持乱序传输(out-of-order transaction):更快内存区域的传输无需等待较慢内存区域的传输完成,减少传输延迟的影响

- 在乱序传输的基础上,支持具有不同AWID的交叉数据写入(Interleaving Transfer)

- 支持使用

字节选通信号(byte strobes)的非对齐传输 - 仅发出首地址的突发(Burst)传输

- AXI 特点:

- ①、单向通道体系结构:信息流只以单方向传输,简化时钟域间的桥接,减少门数量;当信号经过复杂的片上系统时,减少延时。

- ②、支持多项数据交换:通过并行执行突发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

- ③、独立的地址和数据通道:地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。

三、AXI 架构

3、1 AXI 通道

- 1、AXI总线共有5个独立的通道,每个传输通道都是单方向的

- ①、这五个独立通道中的每一个都包含一组信息信号和一个双路的

VALID和READY握手机制:- 发起方:使用VALID信号来指示通道中的数据和控制信息什么时候有效;

- 接收方:使用READY信号来表示何时可以接收数据;

- 数据发起方,发送VALID信号,数据接收方,返回一个READY信号。

- ②、读数据和写数据通道都包括一个

LAST信号,用来指明一个transaction传输的最后一个数据 - ③、

读数据通道传送着slave到master的读数据和读响应信息:- 读数据总线宽度可以是

8,16,32,64,128,256,512,1024位; - 读响应信息指明读事务的完成状态。

- 读数据总线宽度可以是

- ④、

写数据通道传送着master向slave的写数据,- 写数据总线宽度可以是

8,16,32,64,128,256,512,1024位; - 每八位数据都会有一个

byte lane strobe,用来指明数据总线上面的哪些byte有效(即WSTRB[n] = 1,表示第n个字节有效(n从0开始))

- 写数据总线宽度可以是

- ①、这五个独立通道中的每一个都包含一组信息信号和一个双路的

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9208

9208

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?