这里总结各家单片机的引脚相关 开发板商城 找相关设备测试 whaosoft aiot http://143ai.com

[ 0 ]、通用

此为通用部分, 控制LED等可以用此, 不过M3/M4未测

位带区操作

以PB5 为例( 0x42218194 )

STM32F10x支持位带操作的两个内存区的范围是:

0x2000_0000-0x200F_FFFF(SRAM 区中的最低 1MB)

0x4000_0000-0x400F_FFFF(片上外设区中的最低 1MB)

例如操作GPIOB5->ODR寄存器(GPIOB_ODR寄存器的地址为0x4001080c,则A=0x4001080c)

位带区: 支持位带操作的地址区。

位带别名: 对别名地址的访问最终会变换成对位带区的访问。

AliasAddr= 0x42000000+((A-0x40000000)*8+n)*4 =0x42000000+ (A-0x40000000)*32 + n*4

所操作的位带别名区地址:

AliasAddr=*(volatile uint32_t)0x42000000+((0x4001080c-0x40000000)*8+5)*4

=*(volatile uint32_t)0x42000000+ (0x4001080c-0x40000000)*32 + 5*4

=*(volatile uint32_t)0x42218194

#define PB5 *(volatile uint32_t)0x42000000+((0x4001080c-0x40000000)*8+5)*4

#define PB5 *(volatile uint32_t)0x42000000+ (0x4001080c-0x40000000)*32 + 5*4

#define PB5 *(volatile uint32_t)0x42218194

#define BITBAND(addr, bitnum) ((addr & 0xF0000000)+0x2000000+((addr &0xFFFFF)<<5)+(bitnum<<2))

#define MEM_ADDR(addr) *((volatile unsigned long *)(addr))

#define BIT_ADDR(addr, bitnum) MEM_ADDR(BITBAND(addr, bitnum))一、雅特力 arterytek

二、兆易创新 gigadevice

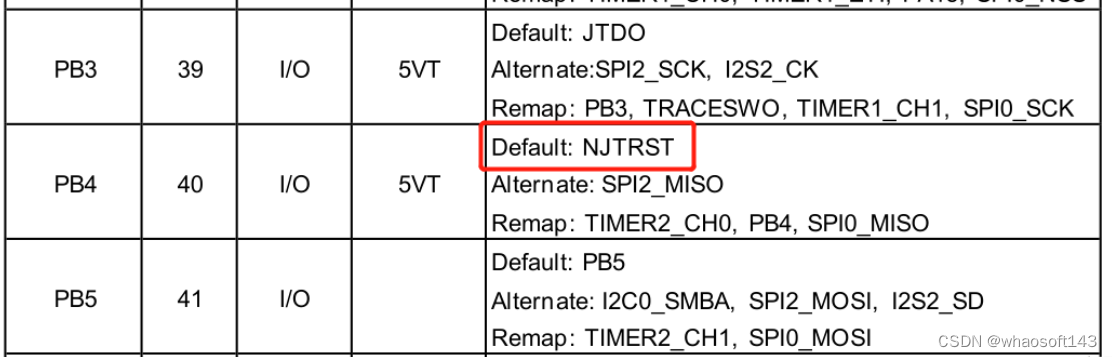

F303CC下

2.1 PB4 - JNTRST

GD32F303取消PB4引脚NJTRST功能映射

故障的出现

配置好GD32F303CBT6的RT-Thread框架后,发现PB4无法拉低,一直处于上拉状态,以为是框架配置的有问题,但是PB3和PB5能够正常的配置电平的高低,百思不得其解。

故障的解决

打开GD303的datasheet,查看pin设置表格后发现PB4默认状态为JTAG模式下的NRST引脚,一直处于上拉状态,无法控制下拉。

编辑

于是调用在在配置PB4引脚之前调用指令:

//管脚复用时钟使能

rcu_periph_clock_enable(RCU_AF);

//PB4管脚默认是NJTRST,要当GPIO,需要重映射

gpio_pin_remap_config(GPIO_SWJ_NONJTRST_REMAP, ENABLE)将PB4引脚的NJTRST功能复用去掉,即可正常将PB10当做正常IO来使用。

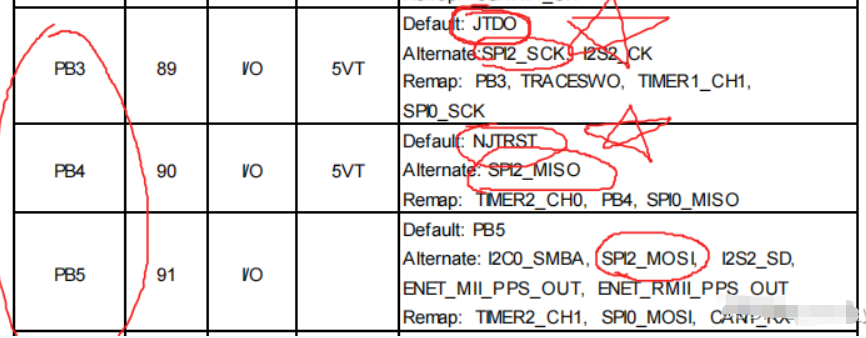

2.2 PB3 - JTDO

问题描述之前只是盯着pb4, pb3给忘了 <debug模式下PB3 可用, 非debug不可用了>

在代码编写和调试时,忽视了PB3和PB4的默认功能是JTDO和NJTRST功能,直接将PB3、PB4当做普通SPI引脚使用,由于我调试时一致使用JLINK连接芯片进行在线调试,在这个时候sram芯片的驱动一直正常,读写数据也正常,也导致我再一开始没有发现这个问题。

后来交给测试人员测试功能时,反馈有时候出现数据丢失的情况。博主排查后发现是sram读写数据失败导致,用示波器排查波形发现在在读写sram时,SCK没有时钟信号发出。博主很奇怪,为何之前调试时没有出现过这种情况?于是乎,连接上JILNK在线调试,用示波器一看,果然,此时sram读写数据都是SCK线上是有正常时钟发出的。。。

在这种情况下,排查了数据手册(datasheet)上SPI相关的引脚,结果发现了问题的根本所在:PB3引脚默认功能为JTDO,PB4引脚默认功能是NJTRST,他们是JTAG调试方式时用的,博主使用的是SWD的方式,且这两个引脚要配置为SPI功能需要做重定向处理,即将关闭这两个引脚JTAG相关功能,这样配置之后,测试发现一切正常了。

修改代码解决

//管脚复用时钟使能

rcu_periph_clock_enable(RCU_AF);

//PB4管脚默认是JTDO,要当GPIO,需要重映射

gpio_pin_remap_config(GPIO_SWJ_SWDPENABLE_REMAP, ENABLE)三、意法半导体 stm32

F103 下

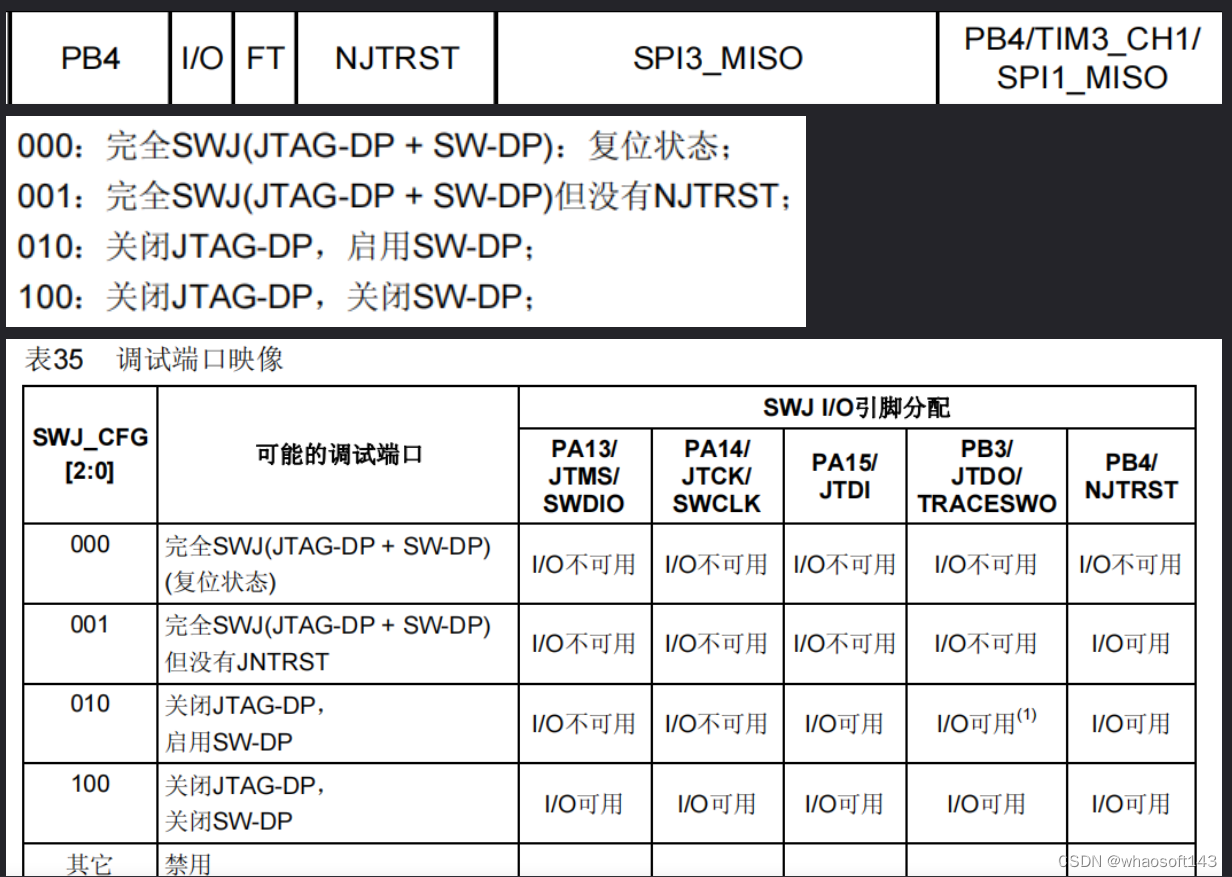

3.1 PB4 - JNTRST

STM32 ~PB4 JNTRST引脚用做普通IO的方法

问题描述:(同上)

PB4默认启动时不是普通IO引脚,是JTAG的复用功能,NJTRST。

编辑

解决方案:

这里我们选择010,完全关闭JTAG-DP,启用SW-DP。

在代码中添加:

GPIO_InitTypeDef GPIO_InitStructure;

RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO, ENABLE);//使能AFIO

GPIO_PinRemapConfig(GPIO_Remap_SWJ_JTAGDisable,ENABLE); //主要就是这个~

// 改变指定管脚的映射 GPIO_Remap_SWJ_JTAGDisable ,JTAG-DP 禁用 + SW-DP 使能

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB, ENABLE); //使能 PB 端口时钟

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_4; //LED1-->PB.4 端口配置, 推挽输出

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP; //推挽输出

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; //IO 口速度为 50MHz

GPIO_Init(GPIOB, &GPIO_InitStructure); //初始化 GPIOB.4

GPIO_SetBits(GPIOB,GPIO_Pin_4); //PB.4 输出高3.2 PB3 - JTDO

不知道是不是因为上面代码, 好像3也没事了

1492

1492

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?