引言

在现代数字系统设计中,现场可编程门阵列(FPGA) 凭借其高度灵活性和并行处理能力,已成为通信、人工智能、工业控制等领域的核心器件。然而,传统FPGA开发模式要求在运行时保持固定硬件架构,难以满足动态场景需求。动态重配置技术(Dynamic Partial Reconfiguration, DPR) 的突破,使得FPGA能够在不中断系统运行的前提下,实时重构部分逻辑资源,开启了硬件可进化系统的新纪元。本文将从技术原理、实现方法、应用场景及设计挑战等维度,深度剖析这一前沿技术。

一、FPGA动态重配置技术原理

1.1 重配置类型对比

| 类型 | 重配置范围 | 中断时间 | 应用场景 |

|---|---|---|---|

| 完全重配置 | 全芯片 | 毫秒级 | 系统启动、模式切换 |

| 部分重配置 | 局部逻辑 | 微秒级 | 实时算法更新、协议切换 |

1.2 部分重配置核心机制

-

比特流(Bitstream)分层管理

FPGA配置存储器被划分为静态区域(Static Region) 和多个可重构区域(Reconfigurable Partition, RP)。静态区域承载控制系统和通信接口,RP区域通过动态加载不同比特流实现功能切换。 -

配置接口协议

- ICAP (Internal Configuration Access Port): 片内硬核,支持高速低延迟访问(Xilinx方案)。

- PCAP (Processor Configuration Access Port): 通过处理器总线控制(如Zynq系列PS-PL协同)。

- AXI4-Configuration Port: 基于AXI总线的标准化配置接口。

-

动态切换流程

markdown

加载新比特流 → 冻结目标RP区域 → 擦除原配置 → 写入新配置 → 释放冻结 → 时序收敛检查二、技术优势与挑战

2.1 核心优势

-

硬件资源复用率提升

案例:在软件无线电(SDR)中,通过动态加载不同解调算法(QPSK/16QAM),节省80%的DSP资源。 -

功耗优化

动态关闭空闲模块,例如在图像处理系统中交替启用JPEG编码和H.264编码模块,功耗降低40%。 -

零停机升级

5G基站在业务运行中更新前向纠错(FEC)算法,避免服务中断。 -

容错与自修复

航天器通过重配置替换受辐射影响的逻辑单元,提升系统可靠性。

2.2 关键技术挑战

-

时序收敛难题

重配置可能引入时钟偏移,需通过增量布局布线(Incremental P&R) 和约束优化确保时序一致性。 -

跨时钟域(CDC)风险

动态区域与静态区域的接口需插入异步FIFO或握手协议,避免亚稳态。 -

比特流安全性

采用AES-256加密和HMAC签名,防止重配置过程中的恶意攻击。

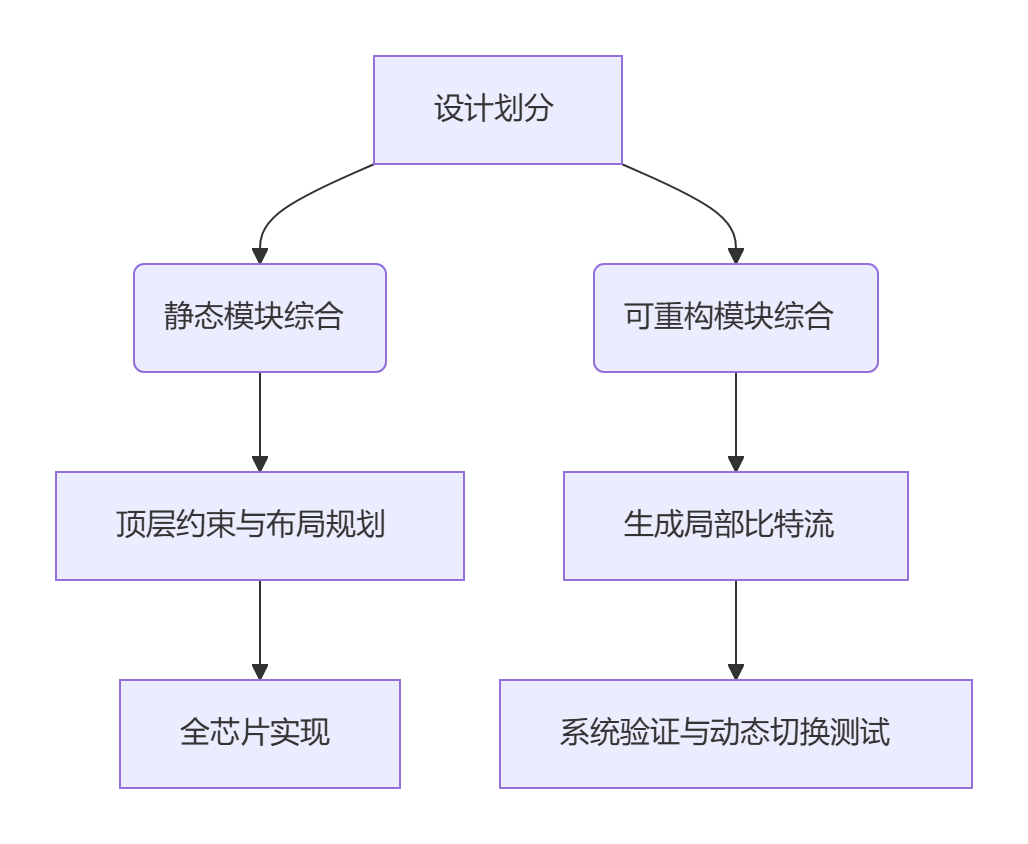

三、设计实现流程(以Xilinx Vivado为例)

3.1 开发流程

3.2 关键步骤详解

-

Floorplanning

使用Pblock约束定义RP区域边界,预留布线通道。建议RP区域宽高比为整数倍,降低路由拥塞。 -

OOC(Out-of-Context)综合

对每个可重构模块独立综合,生成黑盒(Black Box)接口。 -

硬件验证技术

- ICAP状态机设计: 实现比特流加载控制器。

- JTAG-to-AXI Master: 通过Vivado HSI进行在线调试。

verilog

// 示例:ICAP状态机片段 always@(posedge clk) begin case(state) IDLE: if(load_bit) state <= LOAD_HEADER; LOAD_HEADER: // 发送同步字AA995566... // ... 其他状态 endcase end

四、行业应用案例

4.1 自适应无线通信系统

- 场景:5G基站支持多频段多模式

- 实现:动态切换OFDM调制模块和波束成形算法,重配置时间<100μs。

4.2 实时视频处理流水线

- 场景:4K视频会议系统

- 实现:交替加载H.265编码和背景分割算法,资源复用比达6:1。

4.3 深度神经网络加速器

- 场景:边缘端AI推理

- 实现:按需加载CNN/RNN处理引擎,能效提升3倍。

五、未来趋势与研究方向

-

异构计算架构

Xilinx Versal ACAP 将动态重配置与AI引擎结合,实现硬件架构的实时优化。 -

云边协同重配置

通过5G网络远程更新边缘设备硬件功能,构建“FPGA即服务”生态。 -

EDA工具革新

Vivado ML Edition 引入AI驱动的自动布局规划,大幅缩短DPR开发周期。

结语

FPGA动态重配置技术正在重塑数字系统的设计范式,其价值在智能化、可进化硬件系统中愈发凸显。尽管在时序收敛、工具链成熟度等方面仍面临挑战,但随着新型异构计算平台和先进EDA工具的发展,动态重配置必将成为下一代自适应系统的核心技术。

欢迎在评论区交流技术问题,关注博主获取更多FPGA深度解析!

1079

1079

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?