在做小项目的时候使用stm32F103作为一个主控,很多时候都是使用外部时钟源,但项目有时候为了节省经费,减少硬件上的设计成本,在硬件设计上去掉外部晶振,使用内部晶振作为时钟源。

为了解决时钟源的问题,去找了挺多的资料。但这方面的资料实在太少了。通过去官网查找,终于解决了,这次记录一下,方便以后巩固。

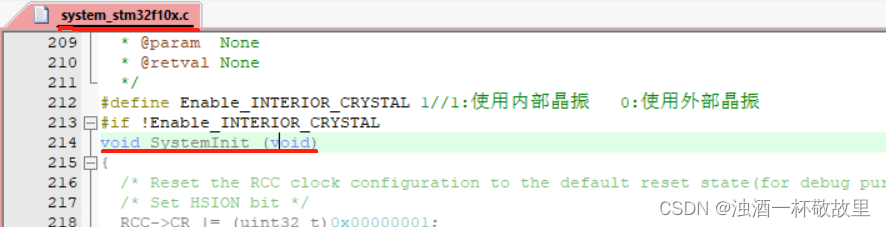

在system_stm32f10x.c文件中,重新写systemInit()函数。可以注释掉原来的函数,重新写一下这个函数。

重新写systemInit()函数。在开启内部时钟时,需要提前设置flash延时,并设置内部HSI校正值。最后才可以开启内部晶振时钟。内部RC默认为8M,将倍频数设置为9,这样使内部RC振荡器之后,时钟频率即为36MHz。为使用外部晶振频率72MHz的一半。

/*PLLCLK=8/2*9=36MHz 设置倍频得到时钟源PLL的频率*/

RCC->CFGR |= ( uint32_t ) RCC_CFGR_PLLMULL9; //设置倍频后的频率//注:HSI:内部晶振时钟

void SystemInit (void)

{

//set flash delay

/* Enable Prefetch Buffer */

FLASH->ACR |= FLASH_ACR_PRFTBE;

/* Flash 2 wait state */

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

while((uint32_t)(READ_BIT(FLASH->ACR, FLASH_ACR_LATENCY)) != FLASH_ACR_LATENCY_2){};

//set HSI校正值

RCC_AdjustHSICalibrationValue(16);

/* 开启HSI */

RCC->CR |= (uint32_t) 0x00000001;

/*选择HSI为PLL的时钟源HSI必须2分频给PLL*/

RCC->CFGR |= (uint32_t)RCC_CFGR_PLLSRC_HSI_Div2;

/*PLLCLK=8/2*9=36MHz 设置倍频得到时钟源PLL的频率*/

//设置倍频后的频率

RCC->CFGR |= (uint32_t)RCC_CFGR_PLLMULL9;

/* PLL不分频输出 */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* 使能 PLL时钟 */

RCC->CR |= RCC_CR_PLLON;

/* 等待PLL时钟就绪*/

while ((RCC->CR & RCC_CR_PLLRDY) == 0){};

/* 选择PLL为系统时钟的时钟源 */

RCC->CFGR &=(uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* 等待PLL成为系统时钟的时钟源*/

while( (RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08){};

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK/2 */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;

}

使用一个led,写一段led闪烁程序,发现可以正常运行。一个延时会不会延长?

有待验证o(* ̄︶ ̄*)o!!!我验证好,再接着更新。这次也是一边看资料,一边搞出来。如有不足之处,还望各路大神指点一下!!

1003

1003

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?