一、算法仿真效果预览

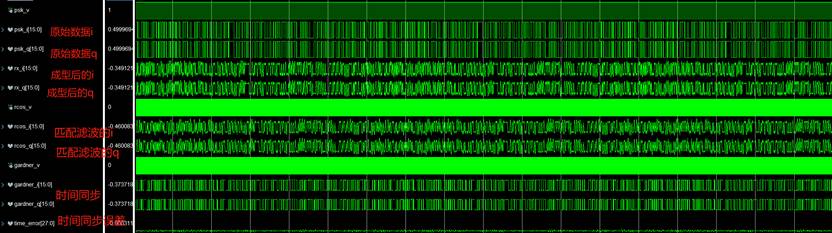

使用 Vitis Model Composer 2022.2仿真测试,测试覆盖从信号生成、编码、调制、成型滤波,滤波抽取,匹配滤波,时间同步,频偏锁定,帧同步,解调的全流程,关键参数如时间同步误差,频偏补偿值可实时观测。

1.1 系统概述

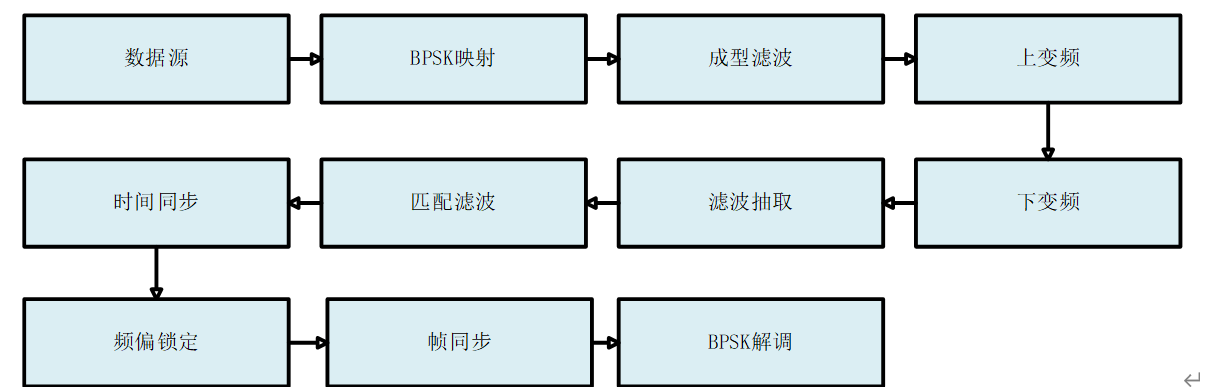

BPSK(二进制相移键控)作为数字通信中基础且常用的调制技术,通过两个相反相位(通常为 0° 和 180°)传输二进制数据。本系统基于Vitis Model Composer实现 BPSK 全流程软解调,核心环节包括数据源生成、BPSK映射、成型滤波、上变频、下变频、时间同步、频偏锁定、帧同步、译码,整体架构如下:

1.2 BPSK 映射 / 软解调

- BPSK映射:将输入二进制比特流(0 和 1)分别映射为两个相反的载波相位,0 对应 0°(复数表示为 1),1 对应 180°(复数表示为 - 1),实现每符号传输 1 比特信息,结构简单且抗噪声性能稳定。

- 软解调:利用判决符号和相位估计结果进行概率估计,提升解调准确性。设判决符号为 d_hat,接收到的信号为 r [n],软解调结果d的计算公式为:d = d_hat / P (d_hat|r [n]),其中 P (d_hat|r [n]) 是接收信号 r [n] 条件下判决符号为 d_hat 的概率,需通过信号概率分布估计或最大似然估计获取,并充分考虑噪声影响。

-

1.3 上变频 / 下变频

- 上变频:将基带信号频谱移至高频载波。通过混频器将基带信号与固定频率本振信号混合,产生频率相加和相减的信号,再经滤波器提取上边带信号,实现基带信号到高频载波的调制,满足远距离传输需求。

- 下变频:作为上变频的逆过程,将接收的高频信号频谱下移至中频或基带。通过与本地振荡器正弦信号混频,提取下边带信号(或进一步处理为基带信号),为后续解调环节提供合适频率的信号。

-

1.4 时间同步(gardner环)

Gardner 环是一个典型的 “反馈控制系统”,整体流程分为 4 步,形成闭环跟踪

- 信号采样:根据当前 NCO 输出的时钟,对接收基带信号进行三点采样(sk−1、sk−1/2、sk);

- 误差检测:通过 TED 计算定时误差ek;

- 环路滤波:用低通滤波器(LPF)滤除ek中的高频噪声,得到平滑的控制电压uk(避免时钟频繁抖动);

- 时钟调整:NCO 根据uk调整采样时钟的相位或频率,反馈到第一步,直到ek趋近于0,实现定时锁定。

基于 PN 导频和 CORDIC 的频偏锁定

发送端在数据帧中附加已知伪随机(PN)导频序列,接收端利用该序列估计频偏。具体步骤为:接收端将导频数据延迟后与原始导频共轭相乘,通过 CORDIC 算法对结果的实部和虚部进行迭代旋转,估计相位偏移并计算频偏值;最后将接收信号与反向复数指数函数相乘,完成频偏补偿,将频偏锁定至零。

1.5 基于相关峰的帧同步

接收端通过本地已知序列(如训练序列、PN 导频序列)与接收信号进行相关运算,确定最佳采样时刻。当两者相位和时间对齐时,相关值出现峰值,峰值对应的位置即为定时点,确保后续采样、判决环节能准确获取信号数据。

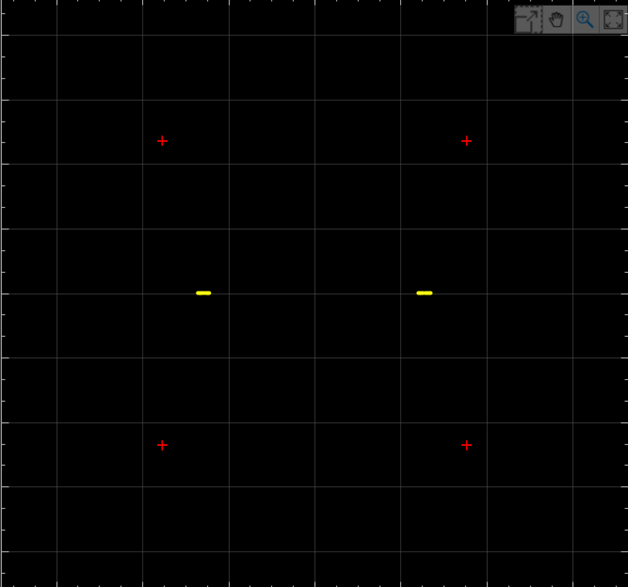

1.6 采样判决

在定时点确定后,对接收信号进行采样,将采样值与预设判决门限比较,恢复原始二进制比特流。对于 BPSK 信号,根据采样点在复平面上的位置(靠近 1 或 - 1),判决发送比特为 0 或 1

图 1 系统信号抓取图

图 2 频偏纠正后星座图

实现验证平台:基于RFSOC XCZU47DR平台实现

成都荣鑫科技原创内容,欢迎技术交流,盗者必追究。

961

961

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?