《数字逻辑》

课 程 设 计 报 告

题目: 拔河游戏机

专业: 计算机科学与技术

班级: 14计科2班

组长: 张钦颖(1414080901218)

成员: 无

成员: 无

惠州学院计算机科学系

二○一五 年 一 月 八 日

1 设计任务书

设计题目:拔河游戏机

拔河游戏机用7个发光二极管排列成一行,开机后只有中间一个发亮,以此作为拔河的中心线,游戏双方各持一个按键,迅速地、不断地按动产生脉冲,谁按得快,亮点向谁方向移动,每按一次,亮点移动一次。任一方终端二极管发亮时这一方获胜,此时双方按键被锁住,只有经复位后才使亮点恢复到中心线。

2 总体方案设计

2.1 功能和逻辑需求分析

(1)本课程设计的拔河游戏机由7个电平指示灯排列成一行,开机之后只有中间一个电平指示灯亮,以此作为拔河的中心线,游戏双方各持一个按键,迅速地、不断地按动产生脉冲,谁按得快,亮点向谁移动,每按一次,亮点移动一次。移到任一方终端指示灯点亮,这一方就获胜,此时双方按键均无效,输出保持,只有经裁判置位后才使亮点恢复到中心线。

(2)当一局比赛结束后,由点亮该终点灯的信号使电路封锁加减脉冲信号的作用。即实现电路自锁,使加减脉冲无效。同时,使电路自动加分。

(3)控制电路部分应能控制计数器的计数,可以使计数器停止计数。(其进入方向则由参赛双方的按键信号决定)

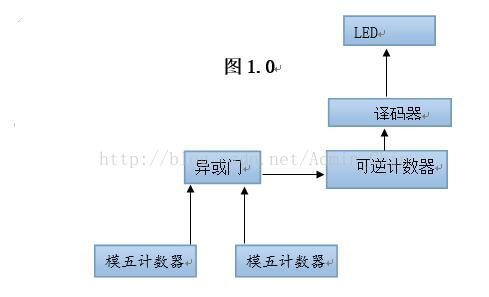

2.2 总体方案设计

2.2.1 模五计数器:

分设两个计数器比较选手快慢,对选手输入的手动脉冲进行计数,用预置法设初始值为0101,即5,使十进制计数器改成五进制计数器,先输入五个脉冲信号的将传一个进位信号到可逆计数器。

2.2.2 可逆计数器:

若甲选手对应可逆计数器的加法,乙选手对应可逆计数器的减法,若甲的速度比乙快(即甲所用计数器先输出进位信号),则控制可逆计数器进行加法,反之,则进行减法.

2.2.3 译码器:

译码器有三个输入和7个输出。每个输入都有和它唯一对应的输出。例如输入为001时对应l1这个灯亮,输入为111时对应l7这个灯亮。

2.2.4 异或门:

由于TDS-4实验箱只有两个手动脉冲,考虑到两个人比赛,那么这两个手动脉冲必然是要接入到计数器中,而比分显示器和可逆计数器都是需要脉冲触发的,而我们用异或门提供一个脉冲给可逆计数器,使得它们可正常计数。

3单元模块设计

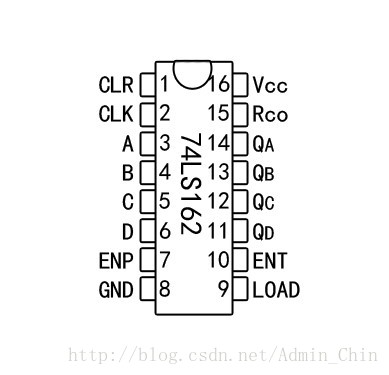

3.1 十进制计数器(2个)

整形电路由两个模为5带进位信号的计数器组成。按键AB为别作为

拔河游戏机设计基于数字逻辑,通过模五计数器、可逆计数器、译码器和异或门实现。玩家按键产生脉冲,计数器比较速度,亮点移动,最先到达终点者获胜。采用7个LED指示比赛状态,游戏结束需复位。电路通过单元模块设计、调试和测试确保功能正常。

拔河游戏机设计基于数字逻辑,通过模五计数器、可逆计数器、译码器和异或门实现。玩家按键产生脉冲,计数器比较速度,亮点移动,最先到达终点者获胜。采用7个LED指示比赛状态,游戏结束需复位。电路通过单元模块设计、调试和测试确保功能正常。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9599

9599

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?