FPGA和CPLD是可编程逻辑器件的典型代表。

我们可以通过软件对其硬件结构进行重构(wait…软件能改变硬件结构?变形金刚啊?),不用像传统方式那样,每次做电路、升级电路都要重新买器件、焊电路。

FPGA:Field-Programmable Gate Array

CPLD:Complex Programmable Logic Device

编程语言可以是VerilogHDL、VHDL

软件常用Quartus等.

下面来介绍一下“变形金刚”的原理。

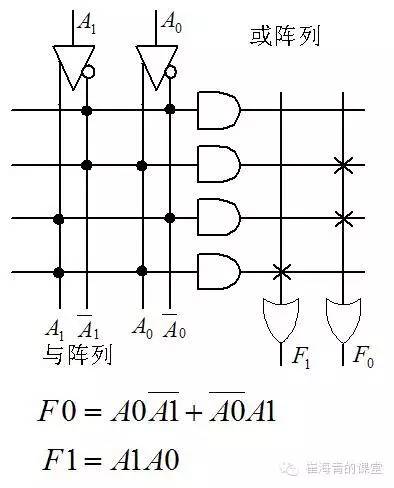

如下图是CPLD内部的一种基本结构”与或门阵列”:

A0、A1是输入信号,F0、F1是输出信号。

通过设置“与阵列”和“或阵列”中交叉点的连接、断开,可以得到F(A0,A1)的任意一种组合逻辑表达式。

故,该电路在硬件不更换的条件下,通过改变交叉点状态,对应逻辑功能是可以再次改变的,所以称为可编程逻辑器件(PLD)。

这些交叉点的通断控制有很多实现方式,早期使用紫外线或激光对交叉点进行照射使其熔断或熔接。现在一般用存储器的值去控制三极管通断实现交叉点通断。所以,对可编程逻辑器件下载配置,实际上可以理解为给存储器赋值。

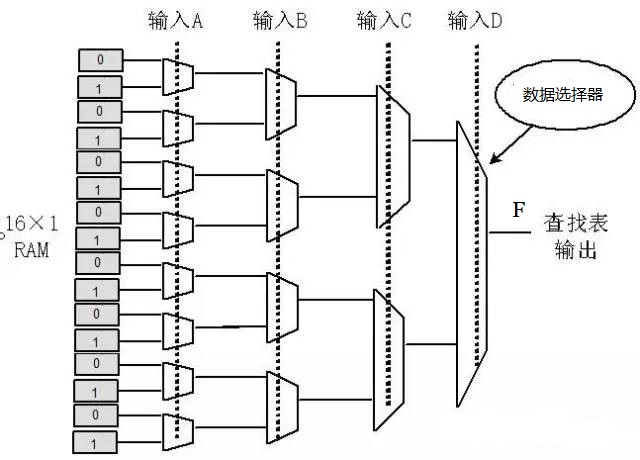

FPGA内部可编程单元结构采用查找表结构(LUT,look up table)

如下图,左侧一列是16X1bit的位存储单元 RAM。输入信号是ABCD,输出信号F在图的最右侧“查找表输出”。通过改变ABCD输入,可以选择对应地址的值输出。通过修改存储单元RAM的内容,这个电路结构可实现任意的F(A,B,C,D)函数。有没有发现,这个结构和数字电路中真值表的功能是一模一样的。

总结:

VerilogHDL是我们描述电路功能的语言,软件Quartus根据Verilog语言,让计算机自动设计出电路结构,并将这种结构配置到FPGA芯片中,实现其内部结构的重构。

在现代电子系统设计中,可编程逻辑器件的使用,极大地降低了用户设计大规模数字电路的难度,实现了电子设计自动化(EDA,Electronic Design Automation)。

FPGA、CPLD内部结构非常丰富,绝不局限于以上内容。本文仅帮助大家快速揭开可编程逻辑器件的神秘之处。

2390

2390

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?