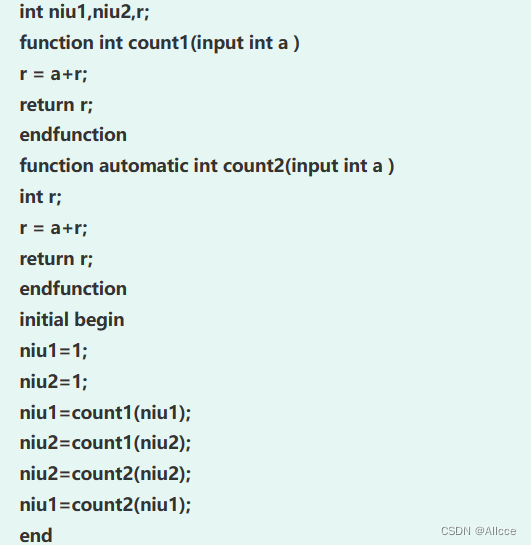

1)静态函数和动态函数的值累积问题:

函数定义时有没有写automatic,当写了时候,那么每次调用都是重新开始。

静态变量可以累积,动态变量运行离开函数后值自动清空

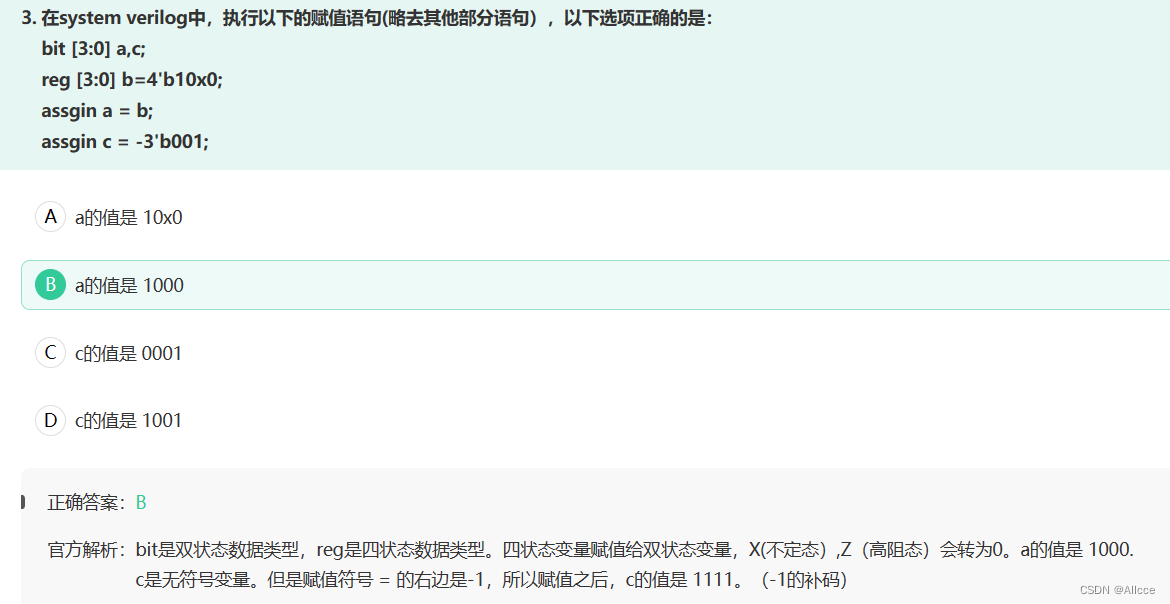

2)有关有符号数向无符号数进行赋值:

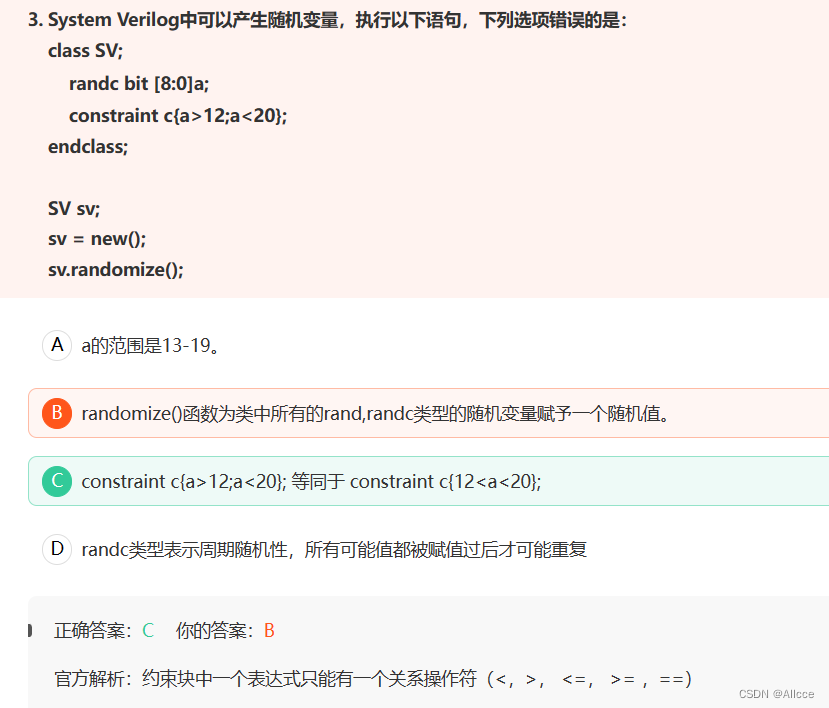

3)new函数是系统预定义函数,不需要void也不需要指定返回值,函数会隐式的返回例化后的对象指针。

4)在program中可以调用module、或其他的program中的task和function

5)system verilog 所提供的机制被称为单一继承, 也就是说, 每一个子类都由唯一的父类继承而来

6)流操作符,包括<<和>>,用在赋值表达式的右边,后面带表达式、结构或者数组。流操作符用于把其后的数据打包成一个比特流。操作符>>把数据从左到右变成流,而<<则把数据从右往左变成流。同时可以指定片段宽度,把原数据按照这个宽度分段之后再转化为流。

7)

8)

== 不能判断x,z状态,遇到x,z返回x

=== 可以判断x,z状态,只有全部位相同,从返回1

==? 通配全等,即其中一个数某位是x或z,都判断为1.

9)

10)System Verilog程序比由许多并行执行的块构成的Verilog更加接近C程序,它拥有一个(或者更多)程序入口。在一个设计中,一个always块可能从仿真的开始就会在每一个时钟的上升沿触发执行。但是一个测试平台的执行过程是经过初始化、驱动和响应设计行为等步骤后结束仿真的。在这里一个连续执行的always模块不可能正常工作。当program中最后一个initial块结束的时候,仿真实际上也默认为结束了,就像执行了$finish一样。如果加入了一个always块,它将永远不能结束,这样就不得不明确地调用$exit来发出程序块结束的信号。

11)SystemVerilog 有如下优点。 单一, 同时支持设计和验证的标准语言。 支持约束随机的产生。 支持覆盖率统计分析。 支持断言验证。

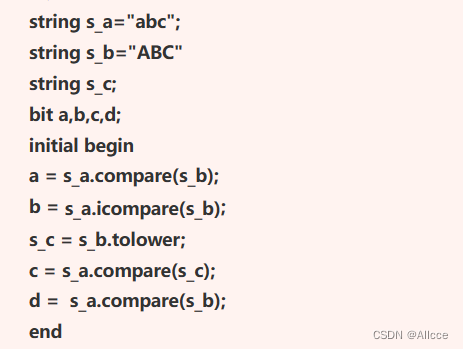

12)SV中的字符串:

System Verilog与C语言不一样的是,字符串的结尾并不带标识符null,所有尝试使用字符"\0"的操作都会被忽略。

字符串使用动态存储方式

单个字符是byte类型

13)

s_b.tolower() 将 中的字符转换成小写形式并返回该字符串;s_b不会发生变化.

s_a.compare(s_b);将s_a,s_b进行比较,区分大小写

s_a.icompare(s_b);将s_a,s_b进行比较,不区分大小写

14)将队列q[$]进行赋值时,含义是将q队列最后一个元素的值传递给j。

15)

16)program属于软件的范畴,不能出现硬件的描述,如always,可以定义initial,进行多个初始化

17)

$fwrite的作用是打印信息到屏幕上,类似于$display

$fseek,文件定位,可以从任意点对文件进行操作

$fstrobe 和 $strobe 使用函数使用类似,都是在时间节点到达时,执行函数

1647

1647

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?