介绍

模100计数器就是一个100进制的计数器。这个设计在实现计数器的基础上将2进制编码的10进制数在7段数码管上进行显示。

数码管展示

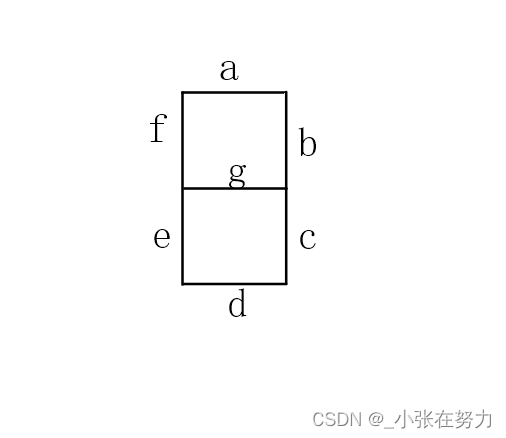

转换电路与SSD(七段数码显示)的连接关系是abcdefg,即最高位传递给a,最低位传递给g。

我们可以得到1-10这十个数字与SSD显示的对应关系。

设计文件

模10计数器

library ieee;

use ieee.std_logic_1164.all;

entity counter is

port(clk: in std_logic;

digit: out integer range 0 to 9);

end counter;

architecture counter of counter is

begin

count: process (clk)

variable temp: integer range 0 to 10;

begin

if(clk'event and clk = '1')then

temp :=temp+1;

if (temp=10) then temp:=0;

end if;

end if;

digit <= temp;

end

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?