介绍

前面已经实现了38译码器,现在我们来实现一下编码器。

对于编码器,就是译码的反过程嘛,哈哈哈哈,大家一定很熟悉了,不多赘述了。

由于之前已经实现了38译码器,所以这里我与之前实现的译码器结合,实现编码译码的全过程,仿真结果和源码都放在最后了。

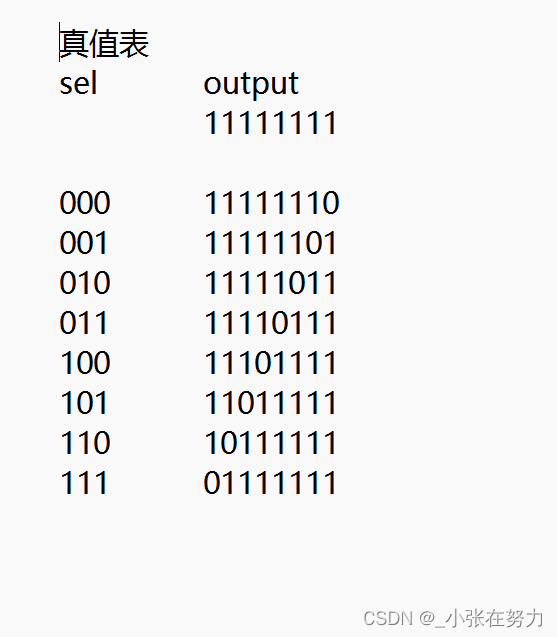

真值表

大家参考38译码器的真值表吧,反过来就是了。

设计文件

library ieee;

use ieee.std_logic_1164.all;

entity encoder is

port(input : in std_logic_vector(7 downto 0);

output : out std_logic_vector(2 downto 0));

end encoder;

architecture encoder of encoder is

begin

output <= "000" when input = "11111110" else

"001" when input = "11111101" else

"010" when input = "11111011" else

"011" w

本文介绍了如何基于已有的38译码器实现编码器,通过真值表设计,给出了编码器的逻辑实现和测试代码,以及顶层模块的端口映射和实例化。作者强调是学习过程中的分享,欢迎提问交流。

本文介绍了如何基于已有的38译码器实现编码器,通过真值表设计,给出了编码器的逻辑实现和测试代码,以及顶层模块的端口映射和实例化。作者强调是学习过程中的分享,欢迎提问交流。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2089

2089

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?