SDRAM(Synchronous Dynamic Random Access Memory) 同步动态随机存储器,同步是指 Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写(from baidu)。

SDRAM的储存是由电容介质充放电实现的,掉电丢失。

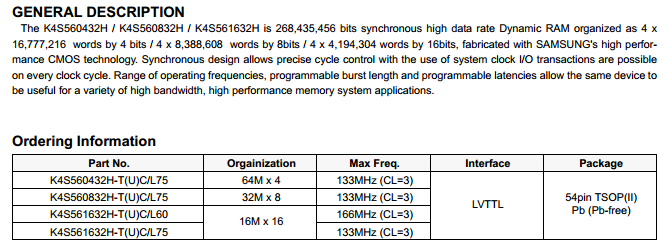

下面我们拿三星的一款SDRAM作为样本详细解析

这块芯片是一块CMOS技术芯片,标准供电电压3.3V

SDRAM芯片的地址都有行列之分,相当于一个表格给定行地址和列地址就能确定其中的某个数据,一块芯片里有几个不同的表格,每个表格称为一个bank

该芯片(大部分SDRAM)中有4个bank

上图中有三种型号*4 *8 *16分别表示输出数据宽度为4bit,8bit,16bit

上图中的引脚作用如下(#代表低电平有效)

CLK 系统时钟 边沿采样,系统时钟必须供给才能让芯片运作

#CS 片选信号 能够屏蔽对芯片的操作,除了CLK,CKE,DQM脚不被影响

CKE 时钟使能信号 当它为0时能够屏蔽系统时钟以此来冻结整个芯片(类似锁存作用)在发送命令一个时钟周期之前就必须将CKE置1

A0~A12 地址 行列地址共用这个信号,行地址占用A0~A12,列地址占用

(x4 : CA0~ CA9

本文深入解析SDRAM(同步动态随机存储器)的工作原理,包括其电容储存特性、地址结构、引脚功能以及初始化过程。重点介绍了行地址锁存、列地址锁存、突发传输、预充电周期、列地址脉冲选通潜伏期等关键时序参数,并概述了自动刷新和自刷新两种刷新机制。此外,还提到了数据掩码在读写操作中的作用。

本文深入解析SDRAM(同步动态随机存储器)的工作原理,包括其电容储存特性、地址结构、引脚功能以及初始化过程。重点介绍了行地址锁存、列地址锁存、突发传输、预充电周期、列地址脉冲选通潜伏期等关键时序参数,并概述了自动刷新和自刷新两种刷新机制。此外,还提到了数据掩码在读写操作中的作用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8214

8214

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?