1.2计算机的基本组成

冯·诺依曼计算机

以“存储程序”这个概念为基础的各类计算机统称冯·诺依曼机。

EDVIC:离散变量自动电子计算机(英语:Electronic Discrete Variable Automatic Computer,EDVAC)是一台美国早期电子计算机。与它的前任ENIAC不同,EDVAC采用二进制,而且是第一台冯·诺伊曼结构的计算机。“存储程序”这个概念就是冯·诺依曼在研制这台机器时提出的。

冯·诺依曼机的六个特点

补充:

- 1中的五大结构包括运算器,存储器,控制器,输入设备和输出设备

- 4中的操作码表示要做什么操作,地址码用来表示操作数在存储器中的位置

- 核心特征是5存储程序

- 这些都不是一成不变的,很可能会有更好的机制,有很多可以改良的地方

冯·诺依曼计算机硬件框图

图中虚线表示数据流动的通路,实线表示控制与反馈

各部分功能:

- 运算器:算术运算,逻辑运算

- 存储器:存放数据和程序

- 控制器:指挥控制程序的运行,完成一条指令的执行,控制指令执行顺序,处理运算结果

- 输入设备:把信息转换为机器能识别的形式

- 输出设备:将计算机处理结果转化为人们熟悉的形式

数据的输入输出都要用到运算器。输入设备输入的数据要通过运算器放到存储器中,要想输出数据也要从存储器再经过运算器,把处理结果输出。

注意存储器中内容可以直接送到控制器中,例如从存储器中取一条指令,可以直接送到控制器中进行分析。

运算器运算时需要把信息从存储器中取出,在运算器中算的结果再保存到存储器中。

缺点

- 以运算器为中心,运算器是瓶颈

- 框图不清晰,没有层次化

计算机硬件框图

以存储器为中心的计算机硬件框图

对以运算器为中心的改进,输入设备的程序和数据可以直接送入存储器,存储器中的计算结果可以直接送到输出设备。控制器通过控制信号和状态反馈信号对整个系统进行控制和感知系统各个部分的状态。

缺点:框图还是比较混乱

现代计算机硬件框图

这是一种层次化的结构

系统复杂性管理方法

- 抽象

- 3’Y

- 层次化Hierachy:将系统划分为多个模块或子模块(递归进行)

- 模块化Modularity:有明确定义的功能和接口

- 规则性regularity:为了重用

计算机的工作步骤

举一个例子

假设是一个累加器型的机器,即两个操作数一个来自主存一个来自累加器(ACC,一种寄存器),假设有加法指令,乘法指令,取数指令,存数指令,打印指令,停机指令

- 如果是计算ax²+bx+c

- 如果是(ax+b)x+c

前者需要的步骤和内存都更多

指令格式举例

指令的格式为:操作码 地址码,都是用0、1代码的组合来表示

(假设操作码6位,地址码10位,000001表示取数)

这些都是只需要一个地址码,因为另一个在ACC中,计算结果也默认保存在ACC中

“【】”表示寄存器或内存单元中保存的内容

操作码可以根据不同操作编码,地址码根据操作数所在的实际物理地址进行编写

还是以上式为例,可以看出,指令和数据以同等地位保存

存储器的基本组成

主存储器(主存/内存)包括:存储体M,各种逻辑部件,控制电路

它的结构可以这样表示:

存储体

接下来,让我们熟悉几个名词:

- 存储单元,存储元件,存储字,存储字长

它们之间的关系是这样的:

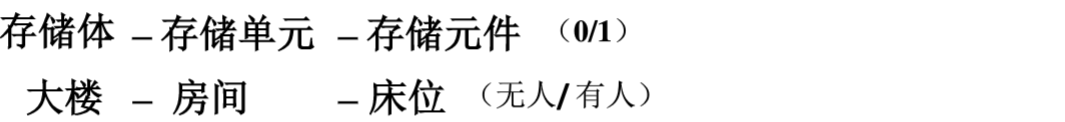

存储体由许多存储单元组成,而存储单元由很多存储元件组成,存储元件有0/1两种状态。

一个存储单元内存储着一串由0/1(存储元件状态)组成的二进制代码,这个就叫一个存储字,它的长度自然就叫存储字长,可以是8位,16位,32位等。

打个比方,一个存储体是一座宿舍大楼,大楼里有很多房间(存储单元),房间里放着许多床位(存储元件),床位有两种状态,有人住(1)、没人住(0)。就拿我们寝室来说,住着四个小姐妹(存储字长是4),每个床位都有人住(存储字为1111)。

在寻访存储体中的数据或指令是就按地址寻访。

MDR,MAR

概念如下:

这里的缩写和中文名是一一对应的

MAR:memory address register

MDR:memory data register

MAR存储器地址寄存器是用来存放欲访问的存储单元的地址,因此它的位数反映着存储体中存储单元的个数,假设MAR有11位,则有2^11=2048个存储单元,记为2K。MDR存储器数据寄存器由于需要存放从某个存储单元中取出的代码或即将存入某个存储单元的代码,它的位数必然等于存储字长。

指令字长,数据字长和存储字长

早期计算机中三者相等,后来指令字长和数据字长要求是可变的,精度更高的,就不能由存储字长来决定指令字长和数据字长了,于是就打算用字节数来算,一个字节(1B)由8位二进制位(bit)组成。但是要注意指令字长,数据字长,存储字长必须是字节的整数倍,字节是计算机中数据处理的基本单位,计算机中以字节为单位存储和解释信息,字长是字节的整数倍便于从内存单元中存取和更好地利用存储空间。

运算器

结构:ALU算术逻辑单元是核心,ACC(累加器),X(操作数寄存器)这两个寄存器是输入,乘除运算时会用到MQ(乘商寄存器),如果不是累加器型的计算机就不一定这这样的硬件结构和数量了。

右图为进行加减乘除运算时各个寄存器中存储的数据。

注意:乘法是一个累加和移位的过程,需用ACC做累加器来保持累加的内容。运算的结果会比被乘数增加一倍,所以分开存储乘积高低位。除法是减法和移位实现的。

具体分析:

- 加法

- 减法

- 乘法

- 除法

上述这些指令的执行,顺序都是由控制器决定的。

控制器

控制器的功能

- 解释指令:从取指令、分析、取操作数到真正地执行指令,保存结果的全过程

- 保证指令的按序执行

控制器的基本组成

PC和MAR之间有一条直接的通路,有自动加一的功能(是指自动形成下一条指令的地址),不是真的加1。

IR的内容来自MDR,IR中的操作码(OP(IR))送到CU,用来分析指令,地址码(AD(IR))则送到了存储器的MAR中。

CU控制单元是控制器的核心,各种信号从CU发出,它分析当前指令需要完成的操作,发出各种微操作命令序列,控制所以被控对象。

I/O

包括:各种I/O设备及其相应接口 I/O设备通过I/O接口与主机(控制器,存储器,运算器)联系,接受CU发出的各种控制命令,并完成操作。主机完成一条指令的过程

取数指令:

执行取数指令需要经过以下步骤:

取指令:(1)PC将目前要执行的指令地址送给MAR,(2)MAR从存储体M中找到对应地址的取数指令并(3)取出送给MDR,(4)MDR把取数指令送给指令寄存器IR

分析指令:(5)OP(IR)被送到CU,CU分析操作码,结果是取数指令

执行指令:(6)AD(IR)被送到MAR,(7)MAR从存储体M找到要取的数,(8)将取的数保存到MDR,(9)将MDR中的数据送到ACC寄存器中

存数指令:

存数指令的取指令部分和取数是一样的,(5)OP(IR)被送到CU,CU分析指令得到是存数指令,(6)AD(IR)被送到MAR,(7)然后MAR再存储体M中找到要存入的地址,(8)ACC中的内容被存入MDR,(9)MDR把数据存入指定的地址中

一个程序:

取数,存数,加法,乘法,打印,停机…等等这些指令都要经过取指令,分析指令,执行指令这三行…以图中例子类推即可

值得注意的是,取指令进行之后就可以使PC+1得到下一条要执行的指令了。

PS:本笔记是高教出版社的计组的学习笔记,是博主自己对课文的整理和理解,当然里面也会包括一些课本原话啦

| To Be Continue |

|---|

1902

1902

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?