1. slave传输响应

一旦master开始传输,slave就控制着传输的进展。master一旦开始传输就不能取消。

当slave被访问时,必须提供一个响应,以指示传输的状态。传输状态由HRESP信号提供。

表5-1表明,完整的传输响应是HRESP和HREADYOUT信号的组合。

表5-1 HRESP信号响应

| HRESP | 响应 | 描述 |

|---|---|---|

| 0 | OKAY | 传输已成功完成,或者slave需要额外的周期来完成请求。HREADYOUT信号指示传输是待定还是已完成。 |

| 1 | ERROR | 在传输过程中发生了错误。必须将错误条件信号给master,以便它知道传输未成功。对于错误条件,需要两个周期的响应,在第二个周期中HREADYOUT被断言。 |

表5-2 基于HRESP和HREADYOUT信号状态的完整传输响应

| HREADYOUT | ||

|---|---|---|

| HRESP | 0 | 1 |

| 0 | 传输待定 | 传输成功完成 |

| 1 | 错误响应,第一周期 | 错误响应,第二周期 |

这意味着slave可以通过以下三种方式完成传输:

- 立即完成传输。

- 标记一个错误以指示传输失败。

- 插入一个或多个等待状态以使传输能够完成。

1.1 传输完成 (Transfer done)

当HREADY为高电平(HIGH)并且HRESP为OKAY时,表示一个传输已经成功完成。

1.2 传输待定 (Transfer pending)

一个典型的slave使用HREADYOUT来插入适当数量的等待状态到传输的数据阶段。然后,传输以HREADYOUT为高电平和一个OKAY响应来完成,以指示传输成功完成。

当slave在完成响应之前插入一定数量的等待状态时,它必须将HRESP驱动为OKAY。

注意

- 一般来说,每个slave在完成传输之前都必须插入一个预定的最大等待状态数。这使得可以计算出访问总线的最大延迟。

- 建议slave不要插入超过16个等待状态,以防止任何单个访问锁定总线太多时钟周期。然而,对于某些设备,例如串行启动ROM,这一建议并不适用。这类设备通常只在系统启动期间被访问,如果使用了超过16个等待状态,对系统性能的影响可以忽略不计。

1.3 错误响应

slave使用错误响应来指示与相关传输的某种错误条件。这通常表示保护错误,例如试图写入只读存储器位置。

尽管OKAY响应可以在单个周期内给出,但ERROR响应需要两个周期。要开始ERROR响应,slave将HRESP驱动为高电平以指示ERROR,同时驱动HREADYOUT为低电平,以延长传输一个额外的周期。在下一个周期,HREADYOUT被驱动为高电平以结束传输,而HRESP保持高电平以指示ERROR。

由于总线的流水线特性,需要两个周期的响应。当slave开始发出ERROR响应时,下一个传输的地址已经被广播到总线上。两个周期的响应为master提供了足够的时间来取消下一个访问,并在下一个传输开始之前将HTRANS[1:0]驱动为IDLE。

如果slave需要超过两个周期来提供ERROR响应,那么可以在传输开始时插入额外的等待状态。在此期间,HREADY为低电平,响应必须设置为OKAY。

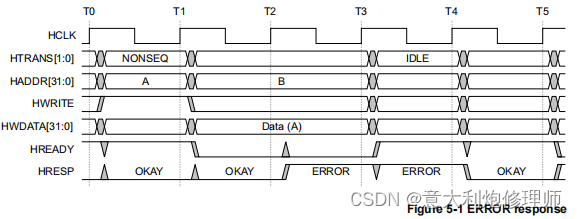

图5-1展示了一个带有错误响应的传输

T1-T2 slave插入一个等待状态并提供OKAY响应。

T2-T3 slave发出ERROR响应。这是ERROR响应的第一个周期,因为HREADY为LOW。

T3-T4 slave发出ERROR响应。这是ERROR响应的最后一个周期,因为HREADY现在是HIGH。

master将传输类型更改为IDLE,这取消了在T2时刻由slave寄存的针对地址B的预期事务。

T4-T5 slave以OKAY响应。

如果slave提供了一个ERROR响应,那么master可以取消突发中剩余的传输。然而,这不是一个严格的要求,master也可以继续完成突发中剩余的传输。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?