目录

1. 介绍

Zynq芯片,作为一款集成了高性能FPGA和ARM处理器的系统级芯片(SoC),为视频处理提供了强大的硬件支持。该芯片内置的丰富视频方面的IP模块,使得从事视频处理项目的开发者能够高效、灵活地实现各种视频处理算法,加速产品的开发和创新。

对于初涉视频处理领域的同学来说,理解Zynq芯片提供的视频处理能力,首先需要掌握一些基础的数字视频知识。这些基础知识不仅有助于理解视频处理的工作机制,而且是使用Zynq芯片进行视频处理项目开发的前提。

文章记录本人入门Zynq芯片在视频处理方面的应用世界,希望通过对数字视频基础知识的掌握,使读者能够更好地利用Zynq芯片进行视频处理项目的开发。

2. 重要概念

视频传输,一次发送一张图像。每个图像从顶行开始逐行发送,每行从左侧像素开始逐像素发送。

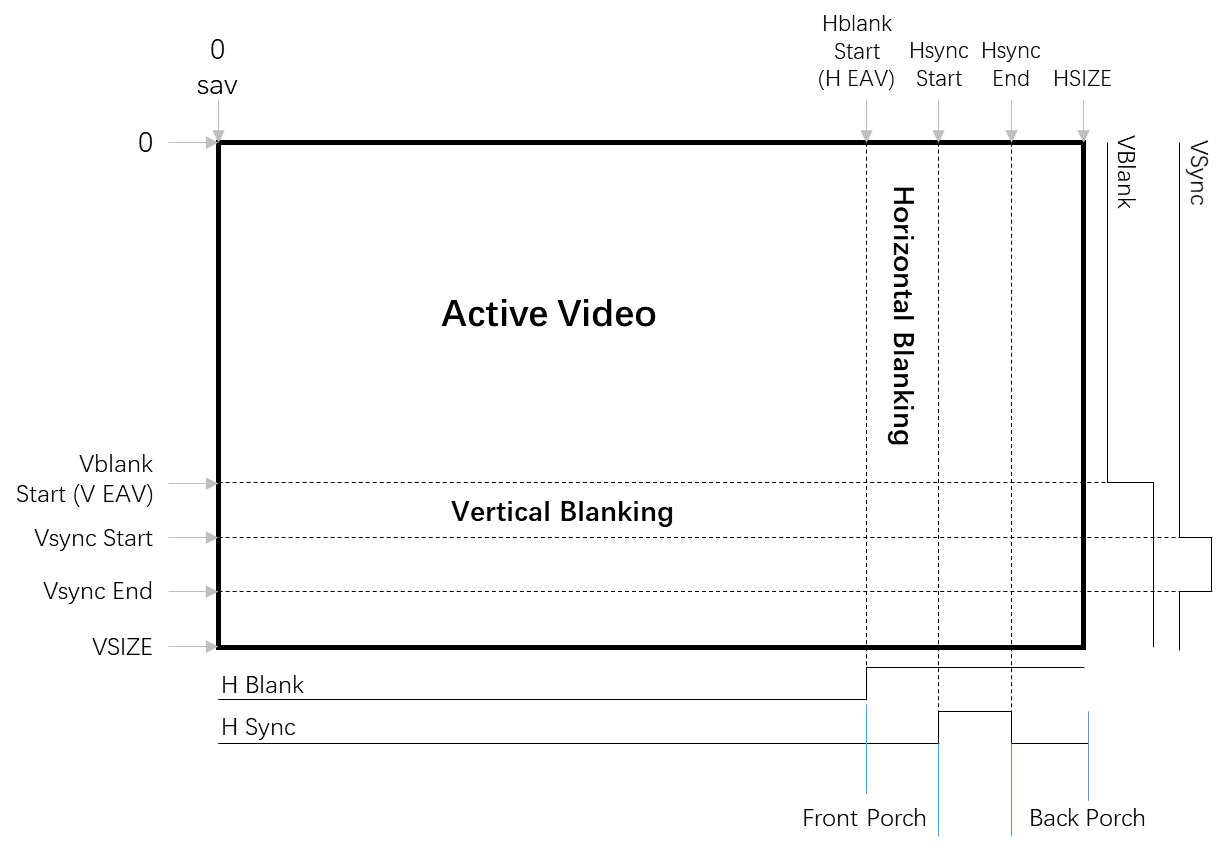

定时信息(由定时信号携带)与像素值一起被发送以描述视频帧定时。视频帧(视频的一个图像)包括活动视频和消隐期。

消隐期,是需要掌握的一个关键性概念。

在早期模拟视频技术中,为了使电子束从一行的末尾回到下一行的开始,或者从一个画面的末尾跳转到下一个画面开始位置时,电子束被暂时关闭的时间段。在这段时间内,屏幕上不会显示任何图像信息,因此被称为“消隐”期。

消隐期主要包括两种类型:行消隐和场(帧)消隐。

行消隐:在CRT(阴极射线管)显示器或电视中,每绘制完一行图像后,电子束需要从该行末尾移动回下一行的起始位置。在这个移动过程中,为了避免在屏幕上产生不必要的扫描线,电子束会被暂时关闭,这段时间就是行消隐期。

场(帧)消隐:在完成一个画面(场或帧)的绘制后,电子束需要从屏幕的底部移动回顶部开始绘制下一个画面。同样,为了避免产生不希望的扫描轨迹,电子束在移动过程中会被关闭,这段时间称为场消隐期或帧消隐期。

在数字视频技术中,尽管不再需要物理移动电子束,但消隐期的概念依然存在。消隐期通常用于同步信号,确保视频数据的正确解析和显示。

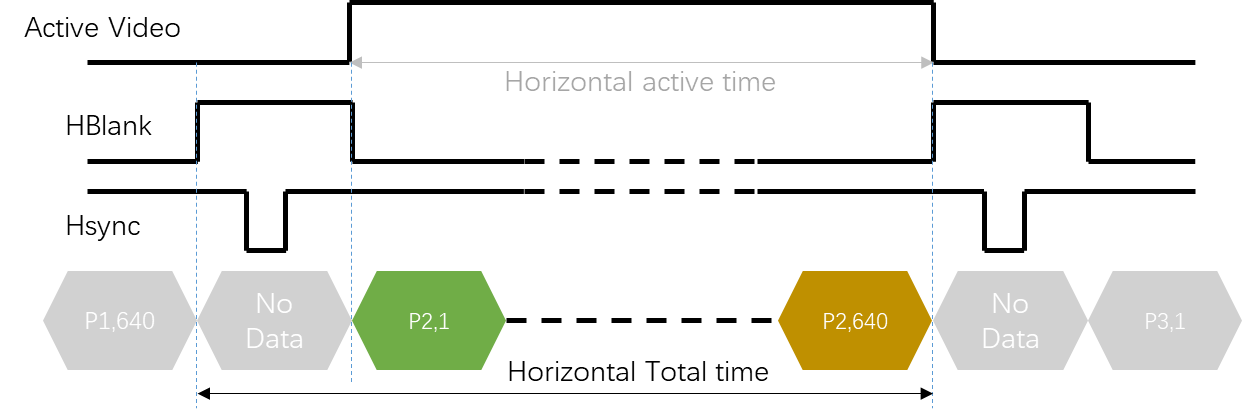

行消隐时序图:

可以观察到,行消隐期间,无数据传输,而其余时间,均有视频有效数据传输。

场(帧)消隐时序图:

对于数字视频信号而言,消隐信号的必要性不如模拟视频信号那么显著,一些新型的视频接口通常不需要消隐信号,因为这些接口传输的是压缩后的数字数据包。

Native video VS AXI4-Stream

在视频处理和传输的领域中,Native video接口和AXI4-Stream接口代表了两种不同的设计理念和应用场景。

Native video接口,特别是在模拟视频信号传输中,典型地包含了消隐信号,这种设计深受传统电视和监视器等模拟视频设备的影响,其中物理电子束的移动是图像显示过程的一部分。

AXI4-Stream接口则是一种基于高性能FPGA和SoC设计的数字视频传输协议。它专为高吞吐量和低延迟的数据传输而设计,不包含传统的消隐信号。在AXI4-Stream协议中,视频数据以流的形式传输,每个数据包都紧跟着同步信号,如行同步和帧同步信号,这些同步信号指示了视频帧的开始和结束。

3. 仿真测试

仅仅通过文字干巴巴地讲述技术概念,太枯燥乏味,尤其是对于复杂的视频处理技术来说,看着这些概念容易昏昏欲睡。

亲自动手进行测量或者仿真测试,往往能够更加深刻地理解这些概念,激发学习的兴趣,让理论知识变得生动有趣。

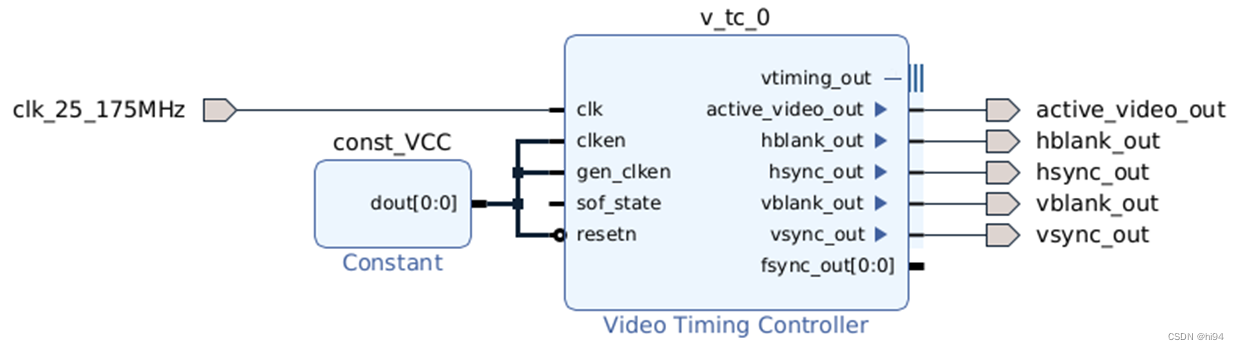

利用Xilinx的Vivado设计套件搭建一个工程,通过实际的设计和仿真,来测试视频处理中的关键信号,如同步信号和消隐信号等。

工程Block Design:

TestBench文件如下:

`timescale 1ns / 1ps

module tb_VTC();

bit clk_25_175MHz = 0;

bit active_video_out, hsync_out,vsync_out, hblank_out, vblank_out;

// Generate the clock : 50 MHz

always #19.86ns clk_25_175MHz = ~clk_25_175MHz;

design_1_wrapper UUT

(

.active_video_out (active_video_out ),

.clk_25_175MHz (clk_25_175MHz ),

.hsync_out (hsync_out ),

.vsync_out (vsync_out ),

.hblank_out (hblank_out ),

.vblank_out (vblank_out )

);

endmodule

很简单吧,Vivado提供了专门的IP核,能帮我们快速够构建起这些关键信号,并对其行为进行精确的模拟和分析。

4. 总结

本序言旨在引领大家进入Zynq芯片在视频处理方面的应用世界,希望通过对数字视频基础知识的掌握,使读者能够更好地利用Zynq芯片进行视频处理项目的开发,进而探索视频处理技术的无限可能。

2521

2521

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?