FPGA高速数据接收设计,多路高精度AD1246数据采集

ID:67500621181984267

卡哇伊2号小宝贝

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有高度灵活性和可重构性,广泛应用于各个领域的高性能计算和数据处理中。在大规模数据采集和处理应用中,FPGA被广泛应用于高速数据接收设计,并能够实现多路高精度AD1246数据采集功能。本文将围绕这一主题展开,探讨FPGA在高速数据接收设计以及多路高精度AD1246数据采集方面的应用和优势。

首先,高速数据接收设计是指在高速数据传输场景中,使用FPGA实现数据接收模块的设计与开发。随着现代通信技术的快速发展和应用需求的提升,对高速数据传输的要求也越来越高。传统的数据接收方式往往难以满足高速数据传输的需求,而FPGA作为一种硬件可编程的器件,具有高速并行处理能力和低延迟特性,成为实现高速数据接收的理想选择。

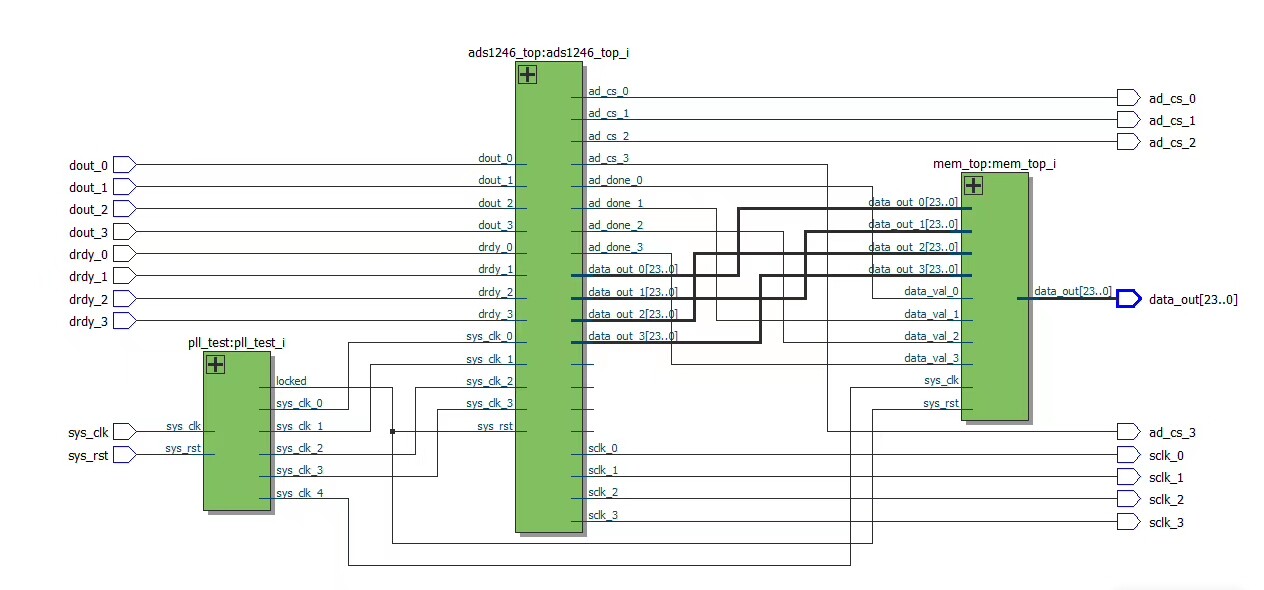

其次,AD1246是一种高精度模数转换器(ADC),主要用于将模拟信号转换为数字信号。在多路数据采集应用中,使用多个AD1246进行数据采集可以提高系统的采样频率和数据精度。FPGA作为数据接收的核心处理器,通过与AD1246相连接,实现对多路模拟信号的同时采集和处理。

针对FPGA高速数据接收设计,首先需要根据实际应用场景确定数据传输的速率和信号精度要求。然后,基于FPGA的开发平台,结合高速串行通信接口(如PCIe、Ethernet等),设计并实现数据接收模块。在设计过程中,需要考虑FPGA的硬件资源利用率和系统时钟频率的配置,以满足高速数据传输的需求。

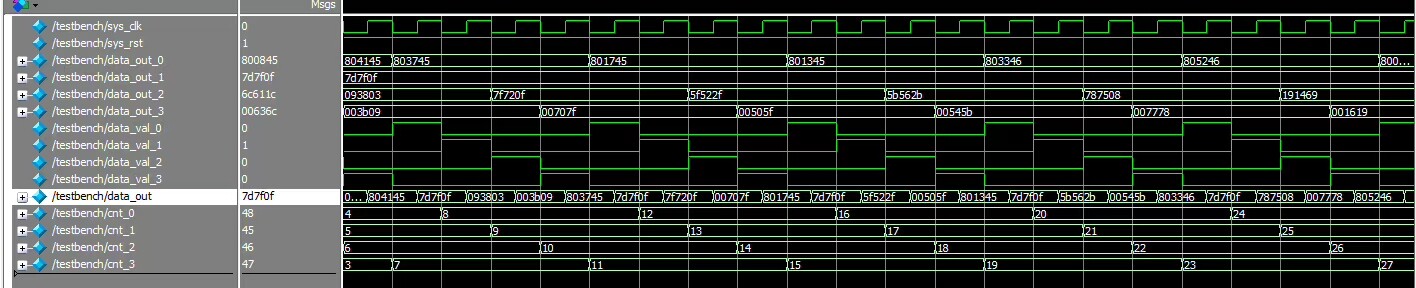

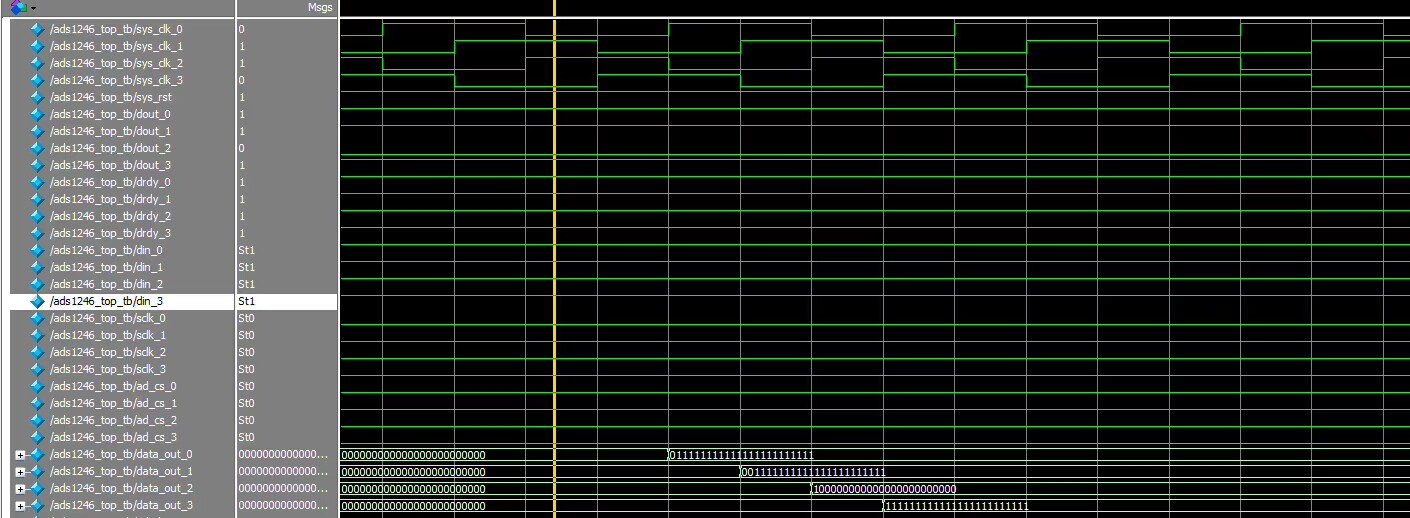

对于多路高精度AD1246数据采集,首先需要对AD1246进行配置和初始化,以保证其正常工作和稳定性。然后,通过FPGA的并行输入/输出功能,将多路AD1246的模拟输入信号传输到FPGA内部进行数据处理。在FPGA内部,可以利用FPGA的并行计算能力和数据流处理技术,对多路数据进行并行采样、滤波和处理。最后,将处理后的数据通过高速串行通信接口传输到外部设备进行存储和后续处理。

在FPGA高速数据接收设计和多路高精度AD1246数据采集过程中,需要考虑以下几个关键问题。首先是时钟同步和数据对齐的问题,由于高速数据传输和多路数据采集的特殊性,需要实现精确的时钟同步和数据对齐,以保证数据的完整性和准确性。其次是数据处理和存储的问题,由于高速数据传输速率较高,对数据处理和存储的要求也较高,需要合理设计数据处理和存储模块,以保证数据的实时性和可靠性。最后是系统稳定性和可扩展性的问题,由于高速数据传输和多路数据采集的复杂性,需要考虑系统的稳定性和可扩展性,以满足不同应用场景的需求。

综上所述,FPGA在高速数据接收设计和多路高精度AD1246数据采集方面具有重要的应用和优势。通过合理设计和优化FPGA硬件和软件系统,可以实现高速数据传输和多路数据采集功能,满足现代高性能计算和数据处理的需求。未来,随着FPGA技术的不断发展和应用场景的扩大,相信FPGA在高速数据接收和多路数据采集领域将发挥更重要的作用,为各行各业的技术创新和应用提供强有力的支持。

相关的代码,程序地址如下:http://imgcs.cn/621181984267.html

3166

3166

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?