FPGA高速数据接收设计,多路高精度AD1246数据采集

ID:67500621181984267

卡哇伊2号小宝贝

FPGA(Field-Programmable Gate Array)是一种可现场配置的逻辑器件,具有高度可重构性和并行性能。在现代高速数据采集系统中,FPGA被广泛应用于实现高速数据接收和处理功能。本文将围绕FPGA高速数据接收设计以及多路高精度AD1246数据采集展开讨论,旨在为读者提供关于该领域的技术分析和实践经验。

首先,我们将从FPGA高速数据接收设计的概念和背景入手。高速数据接收是指在处理器和外围设备之间进行快速数据传输的技术。在现代通信、雷达、成像和科学实验等领域,高速数据接收具有重要的应用价值。而FPGA作为一种可编程的硬件平台,具有并行处理能力和可重构性,能够满足高速数据接收系统对数据带宽和处理能力的要求。

在FPGA高速数据接收设计中,我们需要考虑的关键问题包括数据传输协议选择、数据接口设计和时序控制等。针对数据传输协议选择,常见的有PCIe、Ethernet和高速串行接口等。不同的应用场景和系统需求,选择适合的数据传输协议至关重要。在数据接口设计方面,我们可以借助FPGA内置的SERDES(高速串行器/解串器)模块实现高速数据传输。同时,时序控制对于数据接收的稳定性和准确性也至关重要,我们需要根据具体的应用需求设计合理的时序控制策略。

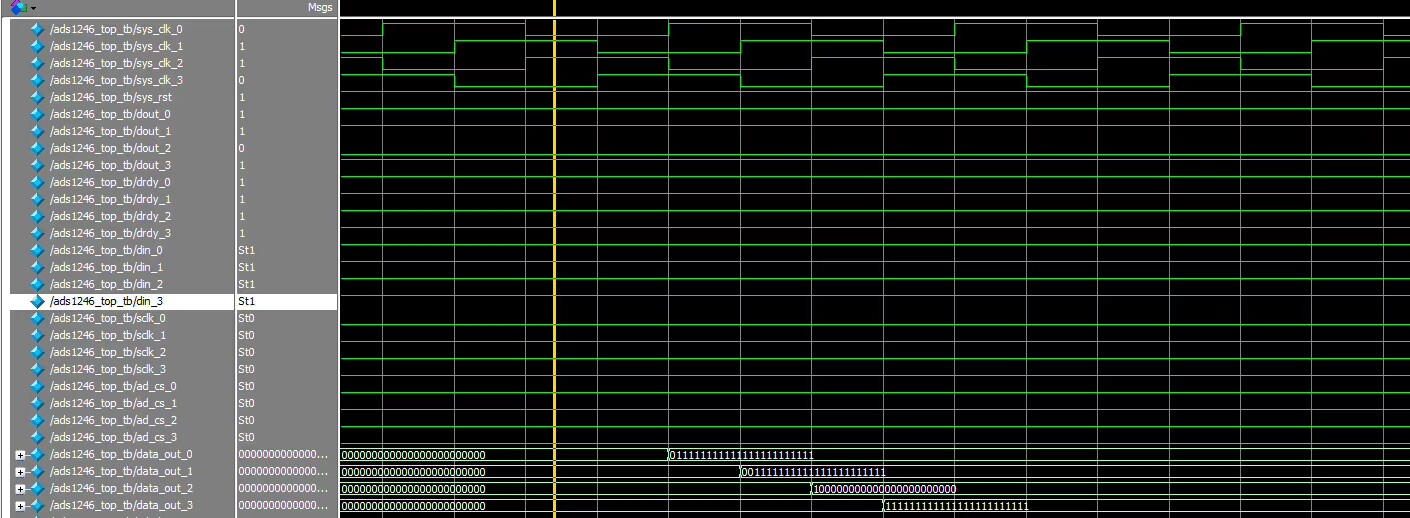

接下来,我们将重点介绍多路高精度AD1246数据采集的设计和优化。AD1246是一款高精度模数转换器(ADC),具有高速采样和低噪声特性。在多路数据采集系统中,我们常常需要同时采集多路信号,并实现高精度的数据采集和处理。对于AD1246数据采集,我们需要考虑的关键问题包括时钟同步、数据缓存和数据校准等。时钟同步是指多路数据采集的时钟信号保持同步,以确保数据的准确性。数据缓存可以用于临时存储采集到的数据,减少FPGA与AD1246之间的数据传输次数。而数据校准则是为了消除不同通道之间的偏差和误差,提高数据的准确性和一致性。

最后,我们将总结本文的内容并展望未来的发展方向。通过对FPGA高速数据接收设计以及多路高精度AD1246数据采集的讨论,我们可以看到FPGA在高速数据接收领域的广泛应用和潜力。未来随着FPGA硬件平台和相关技术的不断发展,我们可以期待更高性能、更灵活可靠的高速数据接收系统的实现。

本文对于FPGA高速数据接收设计和多路高精度AD1246数据采集进行了详细的讨论和分析,希望能够为读者提供有益的技术分析和实践经验。通过深入研究和应用,我们可以不断推动高速数据接收系统的发展,推动科学研究和工业应用的进步。在实际应用中,读者可以根据自身需求和系统要求,结合本文所介绍的设计思路和方法,进行具体的设计和优化,实现高效、稳定的高速数据接收系统。

相关代码 程序地址:http://nodep.cn/621181984267.html

本文详细探讨了FPGA在高速数据接收中的应用,涉及数据传输协议选择、接口设计及时序控制,以及多路高精度AD1246数据采集的时钟同步、数据缓存和校准。旨在为读者提供设计实践指导,推动高速数据接收系统发展。

本文详细探讨了FPGA在高速数据接收中的应用,涉及数据传输协议选择、接口设计及时序控制,以及多路高精度AD1246数据采集的时钟同步、数据缓存和校准。旨在为读者提供设计实践指导,推动高速数据接收系统发展。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?