TX2440 看手册学习2440-CPU时钟频率的设置(ADS1.2编译)

开始前,有必要了解一下概念术语:

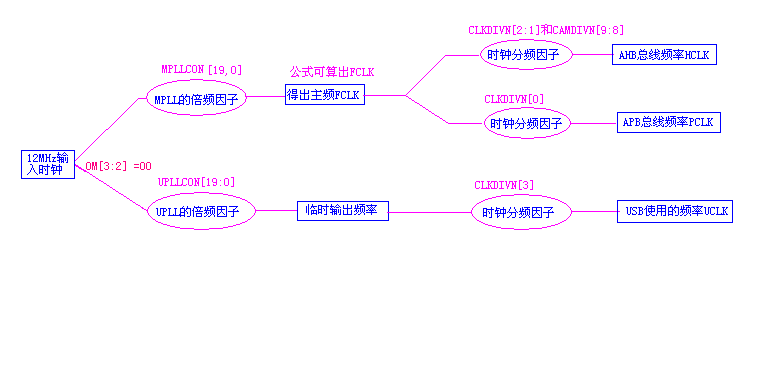

S3C2440A中的时钟控制逻辑可以产生必须的时钟信号,包括CPU的FCLK,AHB总线外设的HCLK以及APB总线外设的PCLK。S3C2440A包含两个锁相环(PLL):一个(MPLL)提供给FCLK、HCLK和PCLK,另一个(UPLL)专用于USB模块(48MHz)。时钟控制逻辑可以不使用PLL来减慢时钟,并且可以由软件连接或断开各外设模块的时钟,以降低功耗。

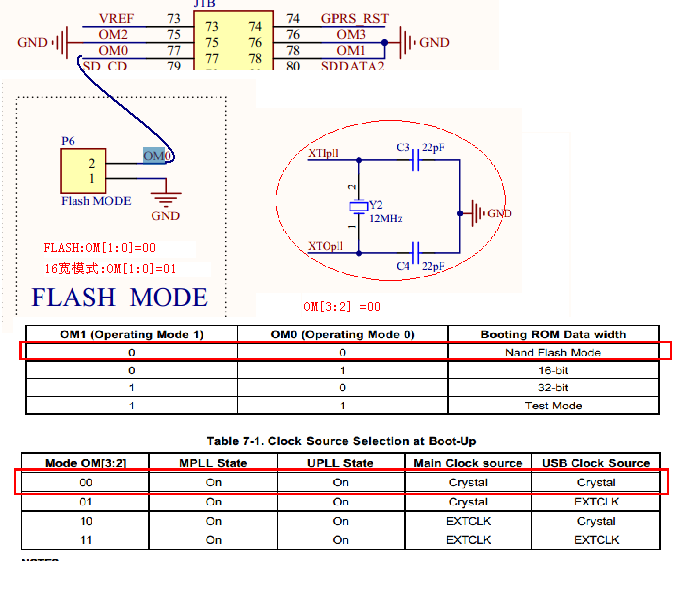

OM连接图(我的板子):

寄存器设置流程图:

注:一般会先设置UPLLCON再设置MPLLCON,设置完UPLLCON后最少运行7个nop指令后再设置MPLLCON,保证2440片子硬件有时间有干活.

输出频率公式:

主频:FCLK=MPLL=(2*m*Fin)/(p*2^s) ,其中m=(MDIV+8), p=(PDIV+2), s=SDIV.

USB频率:UCLK=UPLL=(m * Fin) / (p * 2^s) ,其中m=(MDIV+8), p=(PDIV+2), s=SDIV.

频率设置和频率输出到IO测试:

若主频FLCK是400MHz,如果按照1:4:8的设置,可以先设置CLKDIVN为0101,然后设置CAMDIVN的第9位为0(不设置的时候该位默认为0),此时HLCK是100MHz,PLCK是50MHz。可将该频率映射到CLKOUT0引脚,对其测试验证。

在我们搭建好2440的硬件平台后,我们在调试硬件的时候,通常需要将系统的时钟测试引脚引出来测试,以确认系统是否达到设计的要求。2440提供了CLKOUT0和CLKOUT1这两个引脚用于测试时钟。可以通过设置MISCCR寄存器的CLKSEL0和CLKSEL1位来选择CLKOUT0和CLKOUT1的时钟源。其时钟源分别有000=MPLL输出,001为UPLL输出,010为RTC输出,011为HCLK,100为PCLK,101为DCLK1/0,11X为保留的。

868

868

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?