目录

声明:我买的FPGA开发板是黑金AX4010系列,型号为EP4CE10F17C8N,一步步跟着黑金社区学习,记下笔记是为总结和归纳及方便后来学习的小伙伴,该笔者风格类似于黑金社区的风格(毕竟跟的学习带着影子),【FPGA从0开始系列】文章只限于学习,不允许用于商业用途,转载请注明作者和出处!感谢,码字不易!

1.实验目的

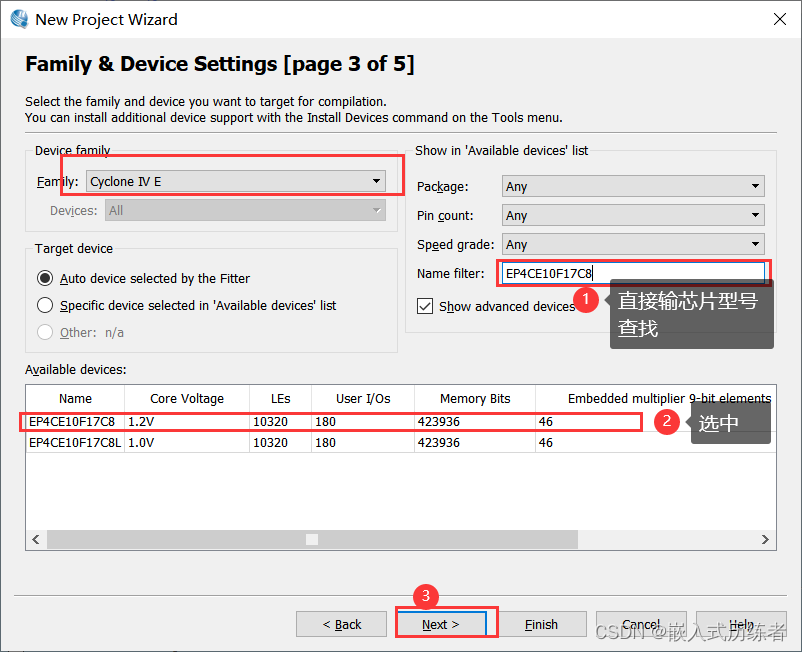

本实验讲述在quartus13.1如何一步步建立工程,配置引脚,编译下载到开发板EP4CE10F17C8N,程序为每隔1s依次点亮4个LED,形成流水灯。

2.准备阶段

2.1电脑安装Quartus13.1软件

2.2FPGA开发板为黑金AX4010系列,型号为EP4CE10F17C8

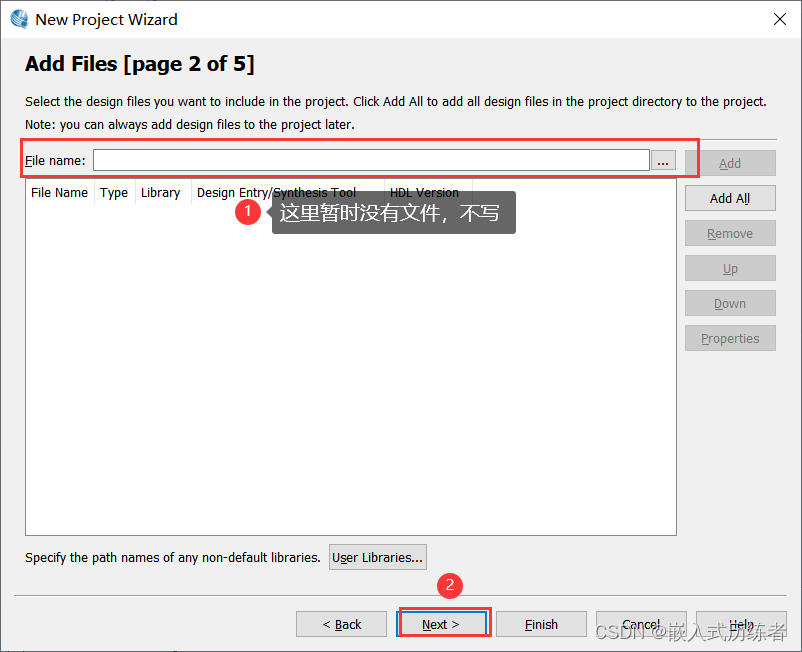

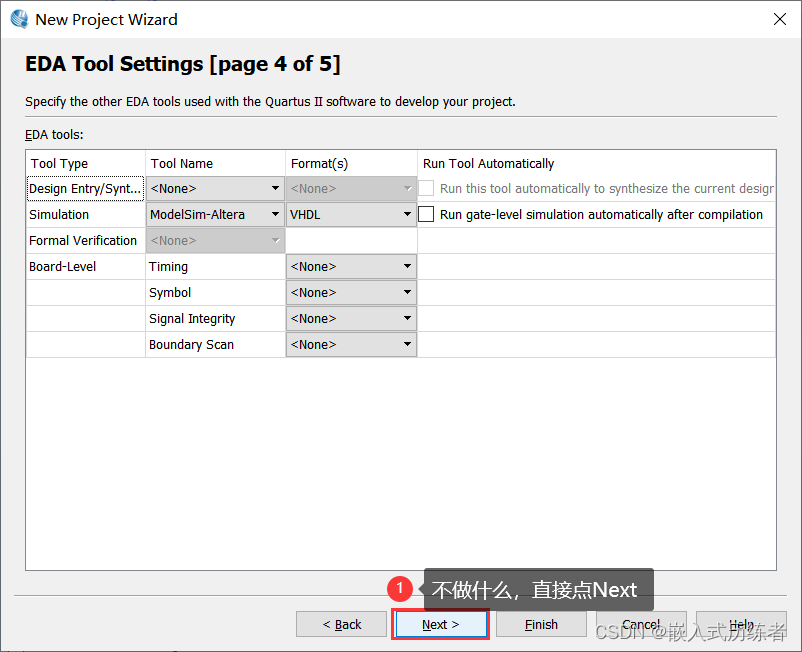

3.建立工程

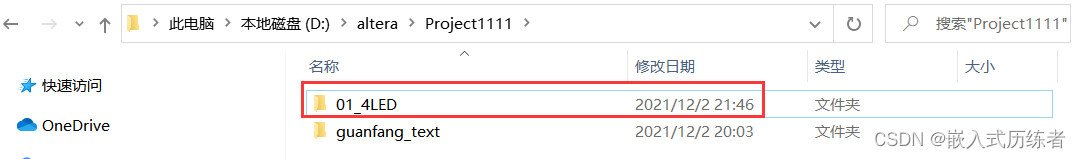

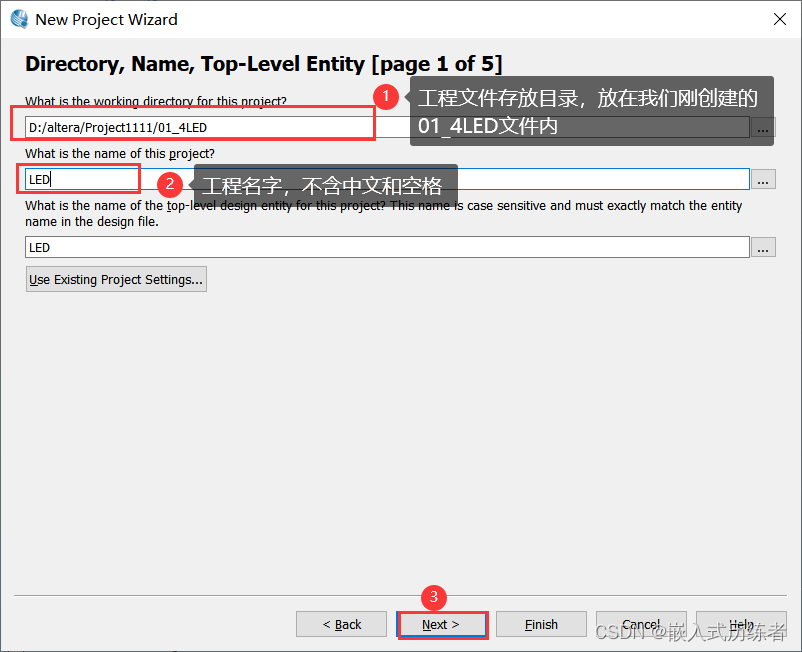

3.1.默认已经好安装和破解Quartus13.1,在D盘(自行选择)中创建一个01_4LED文件存放工程文件(注:文件不能含有中文和空格)

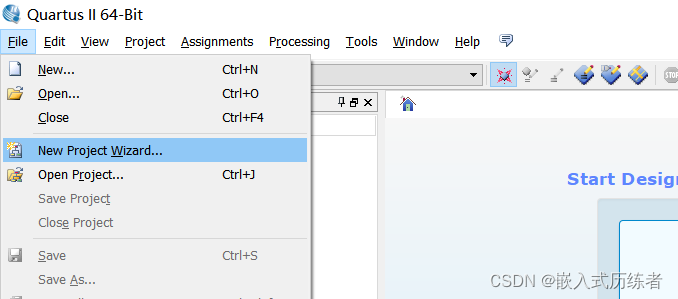

打开Quartus13.1,点击File-->New Project Wizard

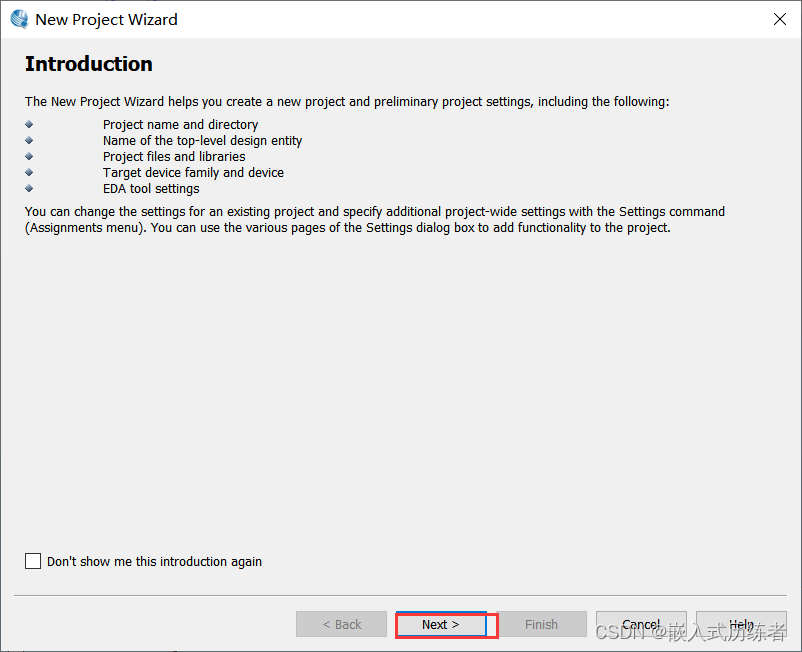

3.2.点击Next

3.3.前面所写工程文件信息的汇总,用于检查,点击Finish

4.创建Verilog HDL File文件

4.1.点击File--->New---->Verilog HDL File---->OK

5.程序代码的编写

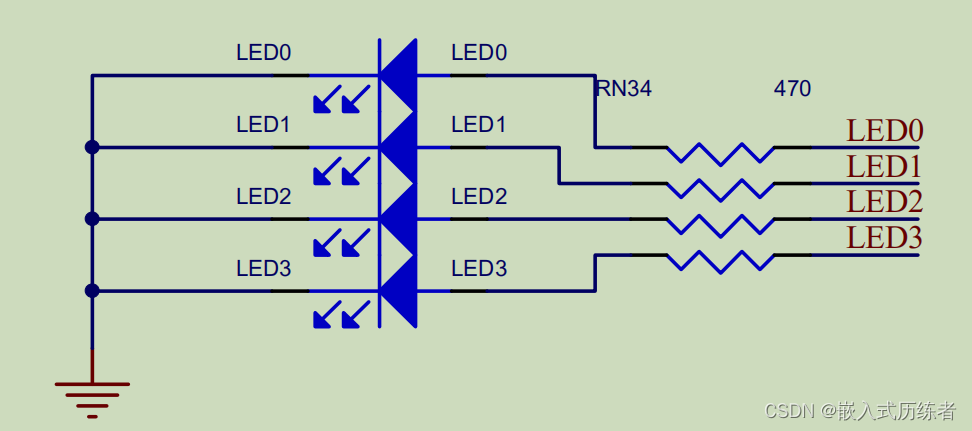

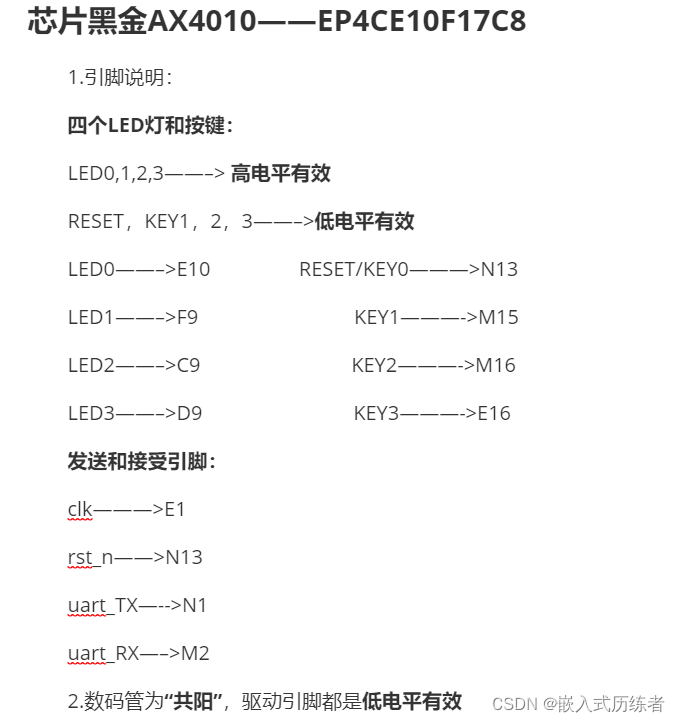

5.1.查看板子EP4CE10F17C8原理图知道LED0,LED1,LED2,LED3共阴,高电平有效,即高电平点亮。(每个硬件开发板有所不同,根据自己的原理图调整程序)

5.2.我总结了FPGA黑金AX4010系列EP4CE10F17C8的管脚分布

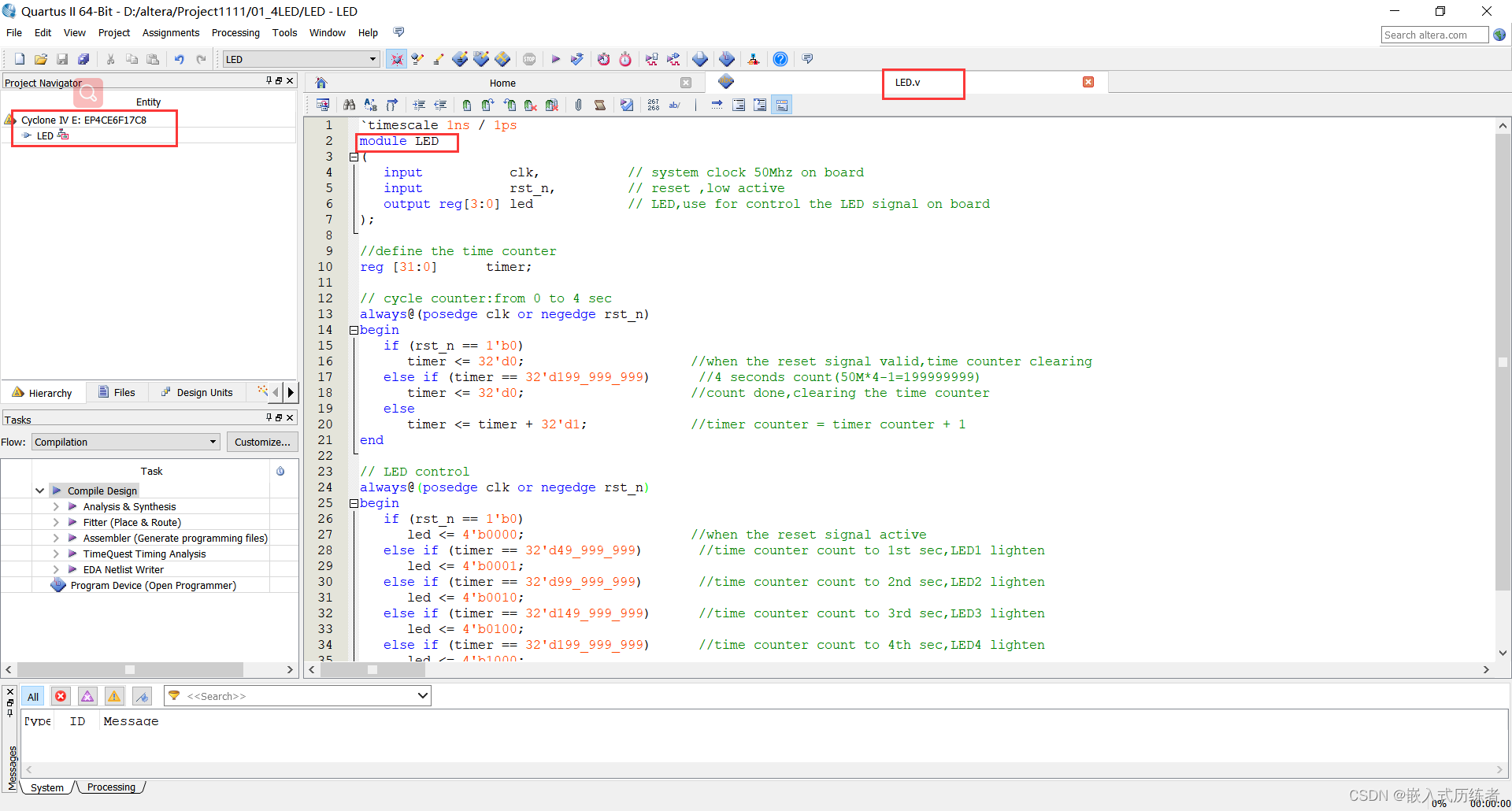

5.3.编写程序(来自于黑金板子的配套例程):

`timescale 1ns / 1ps

module LED

(

input clk, // system clock 50Mhz on board

input rst_n, // reset ,low active

output reg[3:0] led // LED,use for control the LED signal on board

);

//define the time counter

reg [31:0] timer;

// cycle counter:from 0 to 4 sec

always@(posedge clk or negedge rst_n)

begin

if (rst_n == 1'b0)

timer <= 32'd0; //when the reset signal valid,time counter clearing

else if (timer == 32'd199_999_999) //4 seconds count(50M*4-1=199999999)

timer <= 32'd0; //count done,clearing the time counter

else

timer <= timer + 32'd1; //timer counter = timer counter + 1

end

// LED control

always@(posedge clk or negedge rst_n)

begin

if (rst_n == 1'b0)

led <= 4'b0000; //when the reset signal active

else if (timer == 32'd49_999_999) //time counter count to 1st sec,LED1 lighten

led <= 4'b0001;

else if (timer == 32'd99_999_999) //time counter count to 2nd sec,LED2 lighten

led <= 4'b0010;

else if (timer == 32'd149_999_999) //time counter count to 3rd sec,LED3 lighten

led <= 4'b0100;

else if (timer == 32'd199_999_999) //time counter count to 4th sec,LED4 lighten

led <= 4'b1000;

end

endmodule

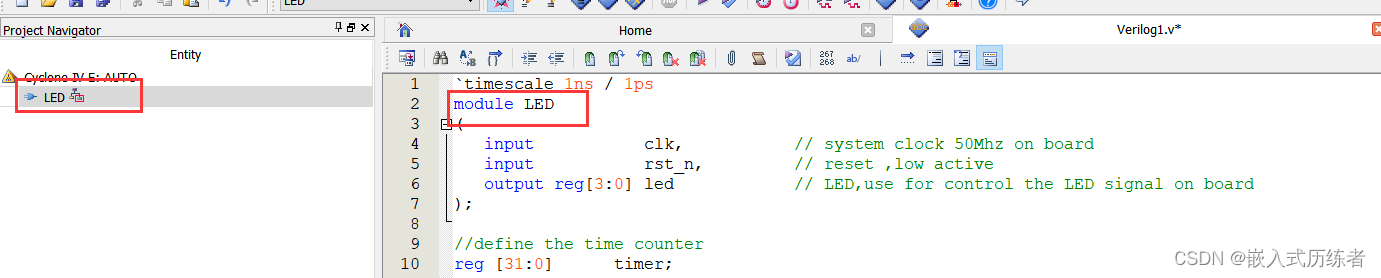

5.4.注意:两者应一致

5.5.写好程序后保存为LED.v文件

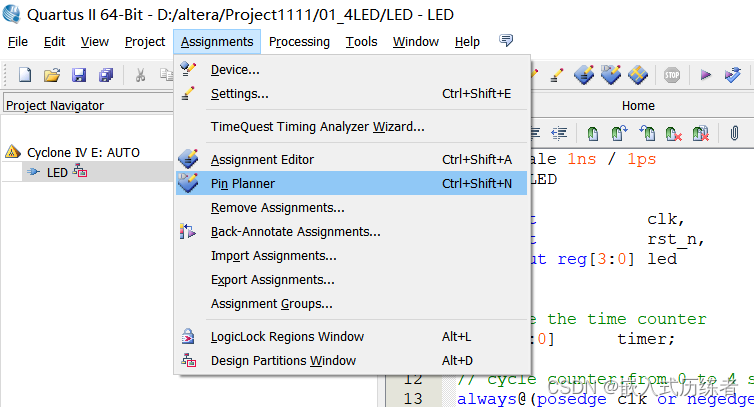

6.配置相应的引脚

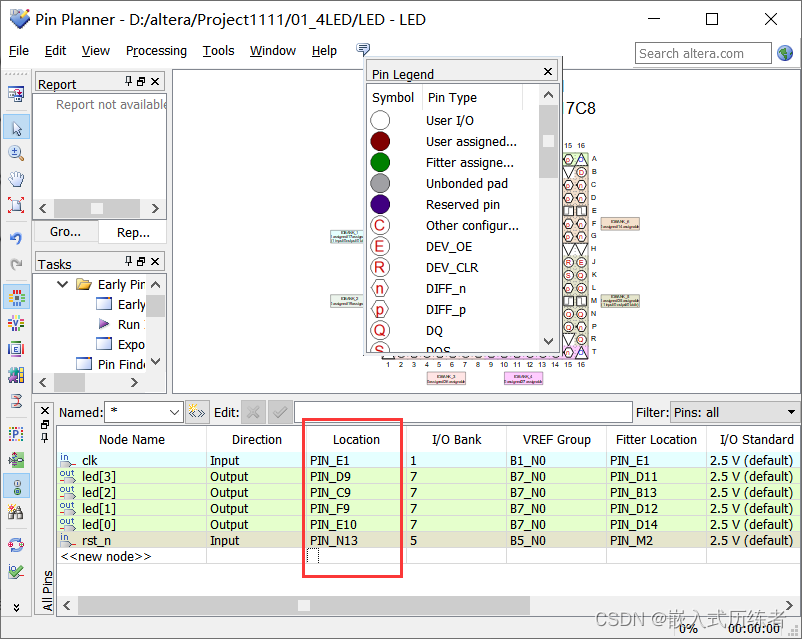

6.1.点击Assignments------>Pin Planner配置引脚,管脚分配的目的是为设计和实际的硬件电路关联起来。

6.2. 由原理图可知每个LED灯对应的引脚,在Location 处写入引脚名,敲回车,如图所示需要注意的是:每个 IO 都必须分配管脚,如果有未分配的 IO,软件可能会随机分配,造成不可预料的后果,严重时可烧坏 FPGA 芯片

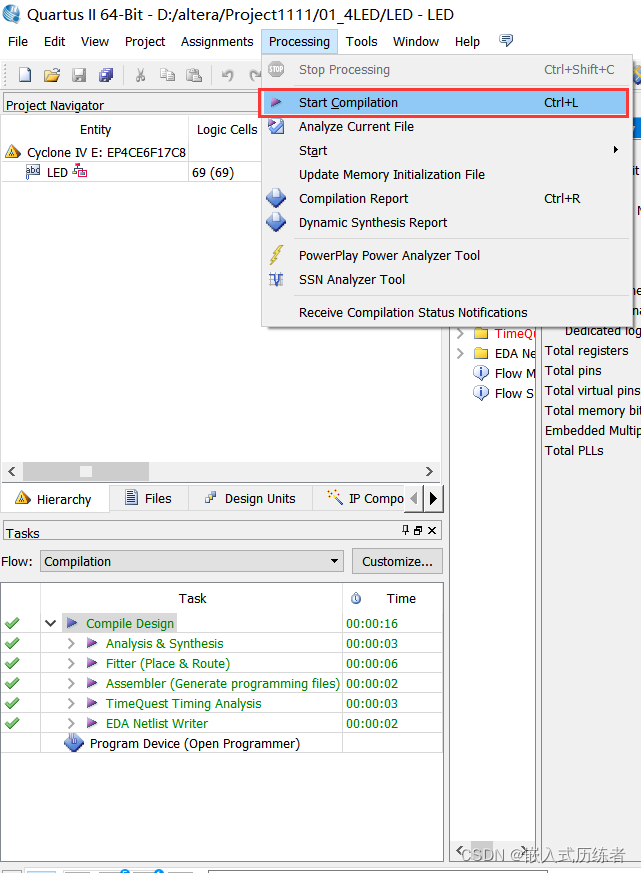

6.3.然后编译工程文件点击Processing------>Start Compilation (小三角形图标)

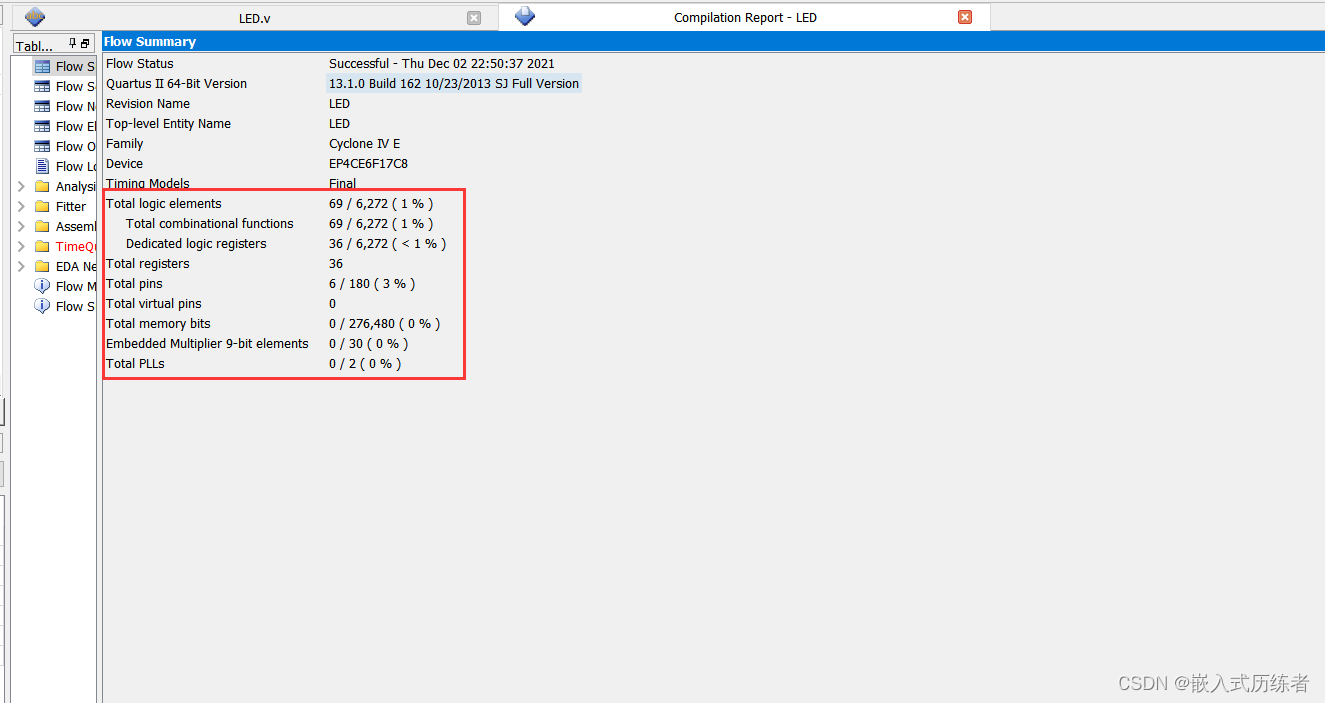

6.4.然后编译成功会打印该工程文件占用了FPGA的多少资源的Report。

7.程序下载板子上

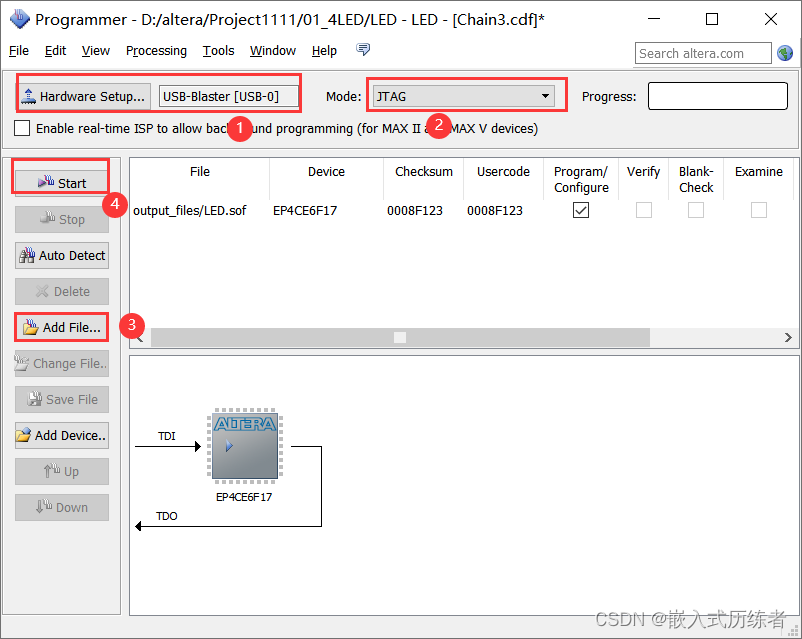

7.1.点击Hardware Setup选中USB-Blaster[USB-0], 选择JTAG下载,点击Add File,选中工程文件中output_files文件下的LED.sof文件,然后点击Start下载。LED.sof这个文件可以通过 JTAG 方式下载到 FPGA 运行,但不能直接固化到 Flash。

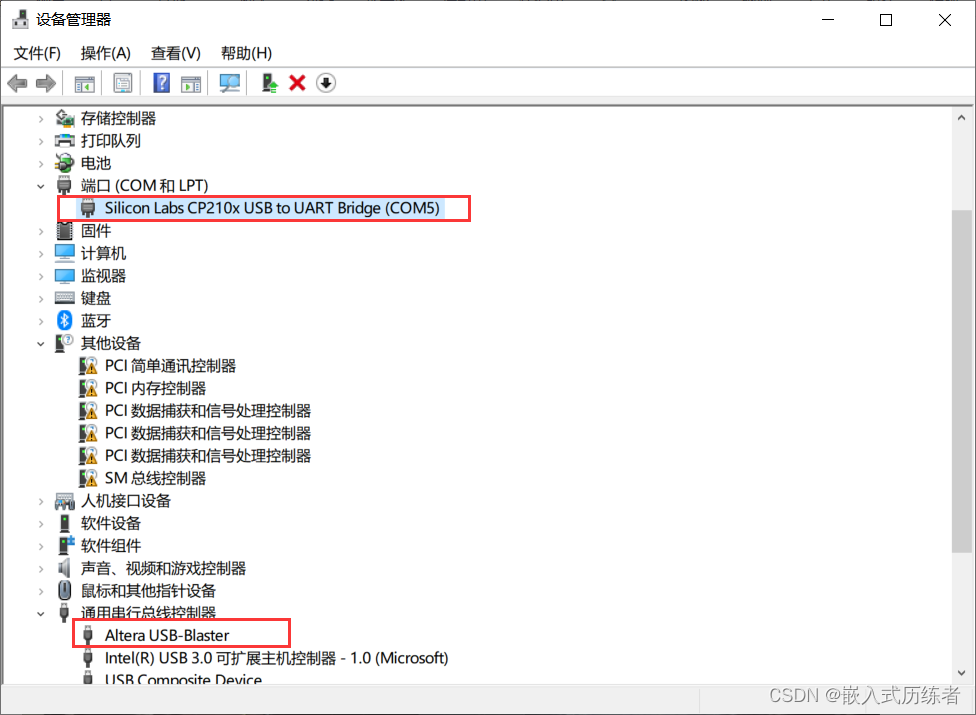

若Hardware Setup没有 USB-Blaster[USB-0],请检查 设备管理器 中是否安装Altera USB-Blaster,若没有安装或出现三角形!警告信息,请自行百度安装!

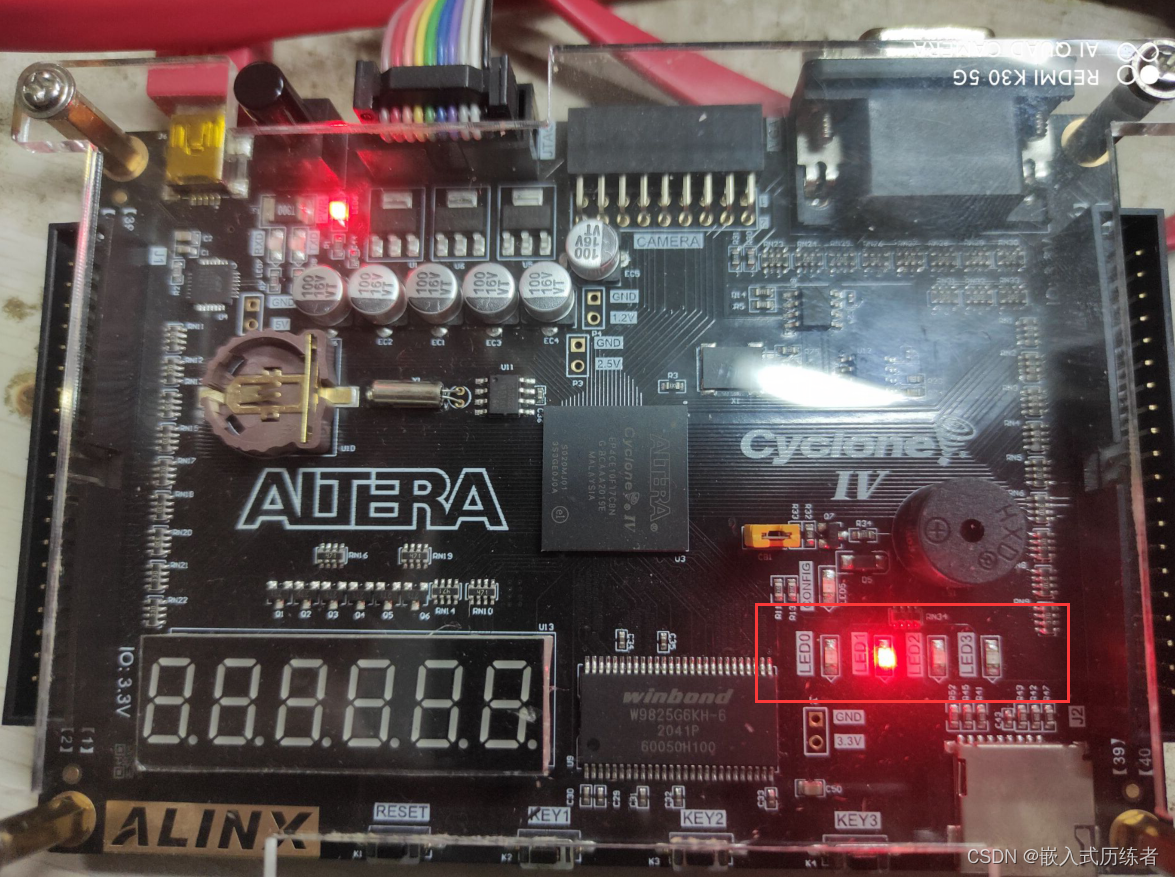

观察开发板现象:

8.固化程序到 Flash

LED.sof这个文件可以通过 JTAG 方式下载到 FPGA 运行的方式,是断电后会丢失。想要断电后下次上电后依然能运行程序,可选择固化程序。

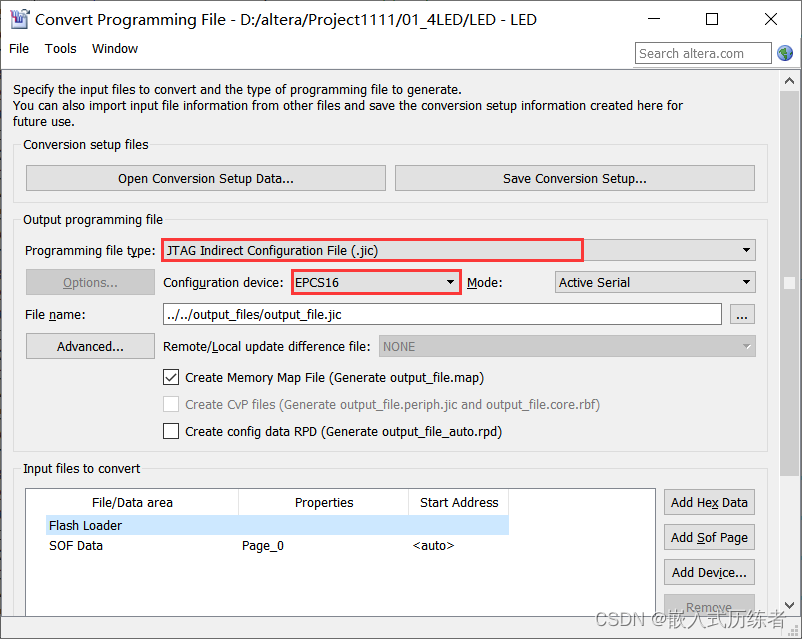

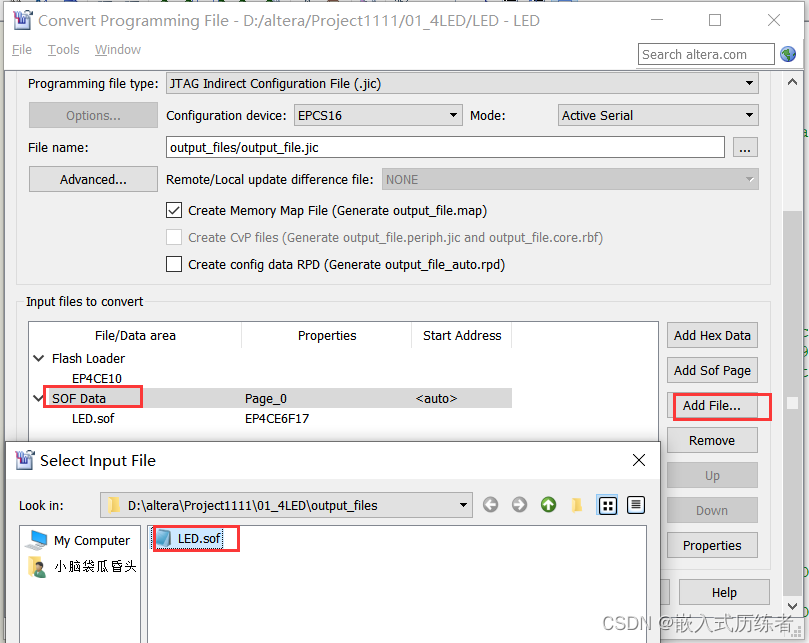

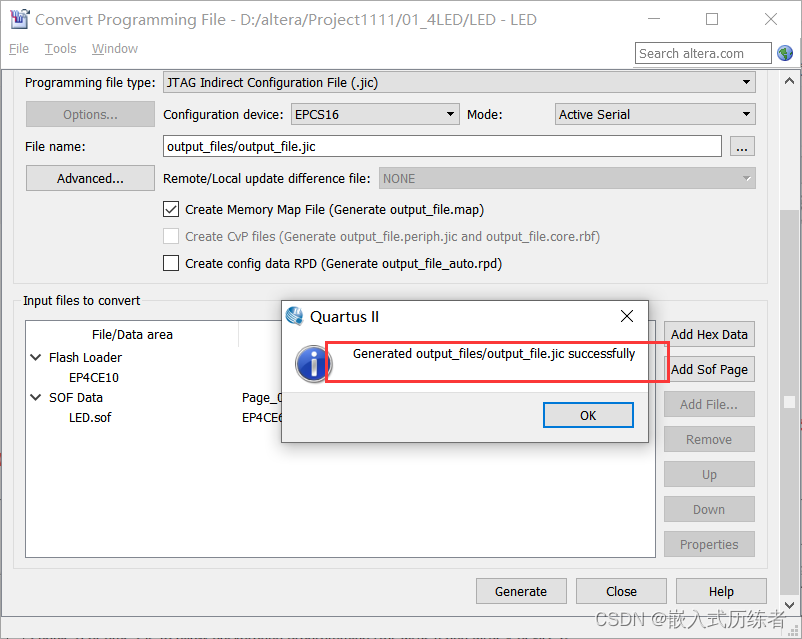

所谓固化,是指讲.sof文件转化为jic文件,直接下载固化到 Flash。

8.2.在图中选择转化的文件类型为jic文件 ,Configuration device:根据开发板型号选择,我选择EPCS16.

AX301 开发板、AX4010 开发板选择EPCS16(指 16M Flash),AX515 开发板、AX530 开发板选择 EPCS64(指 64M Flash),其他类似参见配套资料和自行百度!

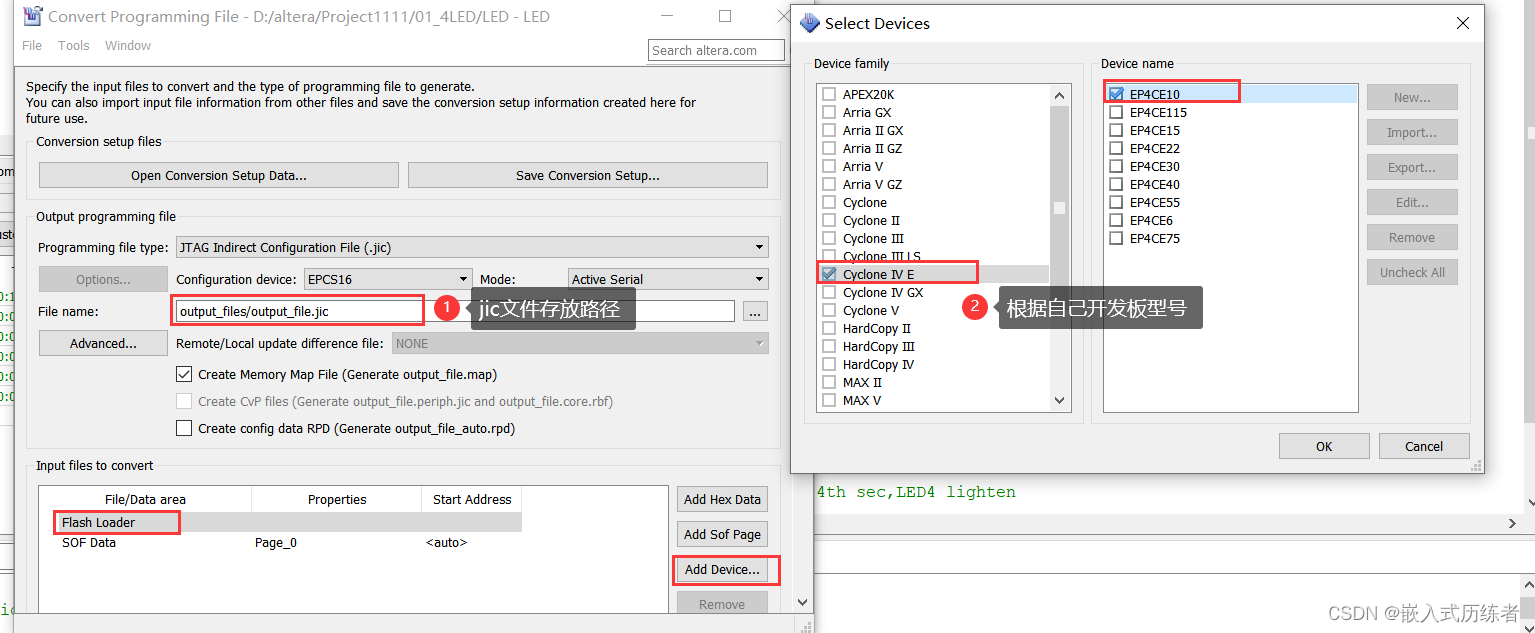

8.3.选中Flash Loader,点击Add Devices,选择自己下载开发板型号

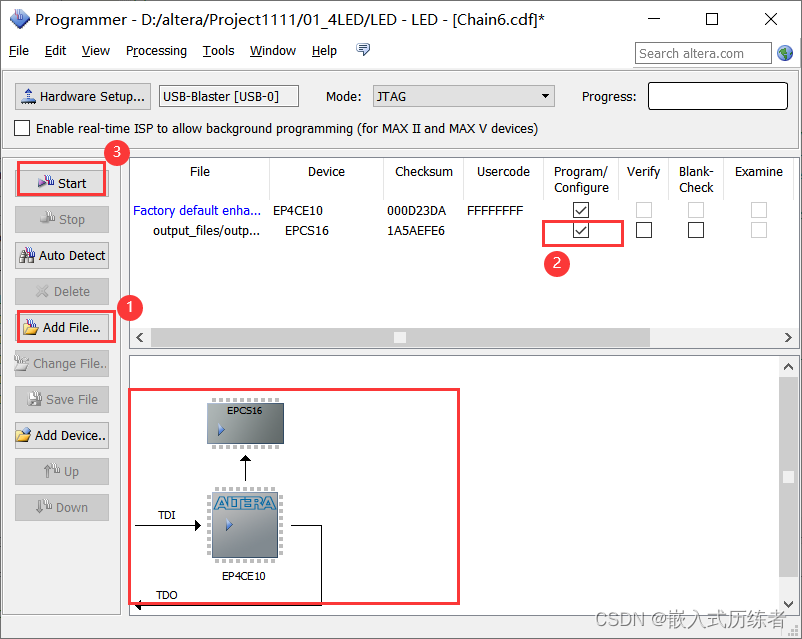

8.5.打开下载界面,和之前下载.sof文件一致的配置,删除其他已有的下载文件(选中文件点击Delete),点击Add File添加jic文件,在图中位置打勾,点击Start下载。

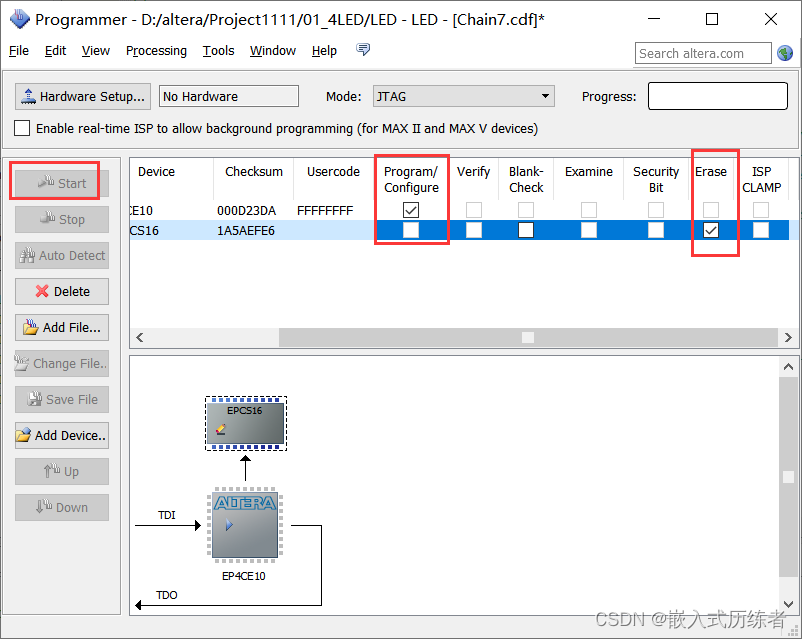

9.擦除 Flash 中已有的程序

OK,欢迎大家的阅读!

本教程详细介绍了如何使用Quartus13.1为黑金AX4010 FPGA开发板创建工程,编写Verilog代码实现每秒依次点亮4个LED的流水灯效果,并进行引脚配置、程序下载及固化到Flash。通过步骤式指导,适合FPGA新手学习。

本教程详细介绍了如何使用Quartus13.1为黑金AX4010 FPGA开发板创建工程,编写Verilog代码实现每秒依次点亮4个LED的流水灯效果,并进行引脚配置、程序下载及固化到Flash。通过步骤式指导,适合FPGA新手学习。

1366

1366

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?