QPSK调制解调 FPGA 实现 verilog 语言

同样支持 FSM,MSK,DBPSK,DQPSK,8PSK,16QAM等信号调制解调FPGA开发

目前只支持用 vivado,modelsim实现,quartus 目前还没有做

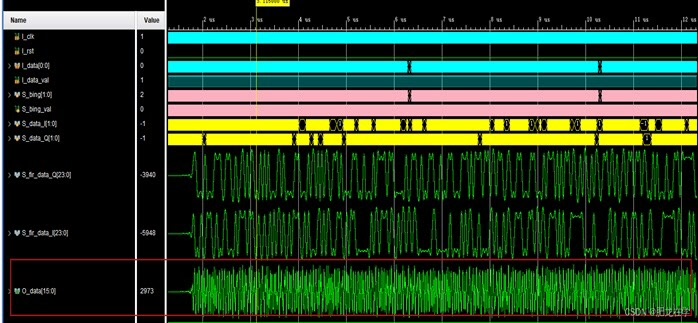

调制分为串并转换,差分编码,上采样(插值),成形滤波,载波相乘等

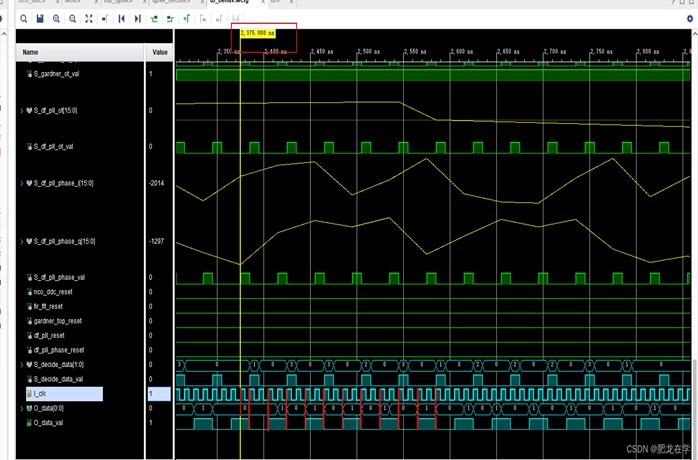

解调分为数字正交下变频,低通滤波,符号同步,载波同步,相差调整,硬判决,差分解码,并串转换等

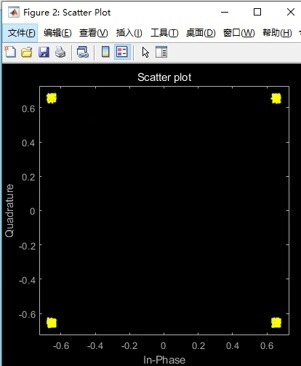

调制解码误码率为 0(无噪声条件下)

ID:12200714258449979

BeyondToday

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1726

1726

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?