QPSK调制解调 FPGA 实现 verilog 语言

同样支持 FSM,MSK,DBPSK,DQPSK,8PSK,16QAM等信号调制解调FPGA开发

目前只支持用 vivado,modelsim实现,quartus 目前还没有做

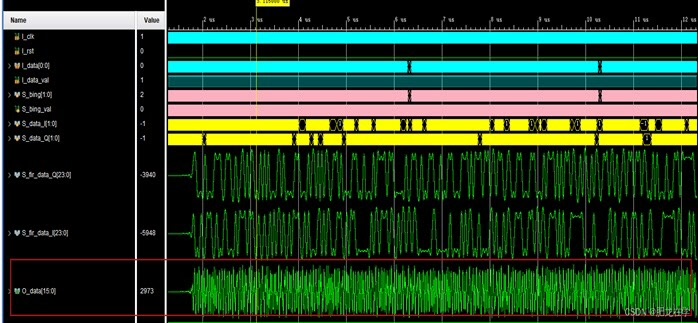

调制分为串并转换,差分编码,上采样(插值),成形滤波,载波相乘等

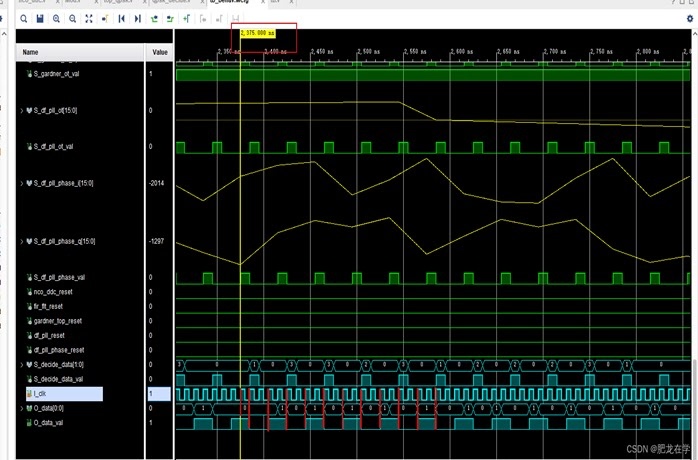

解调分为数字正交下变频,低通滤波,符号同步,载波同步,相差调整,硬判决,差分解码,并串转换等

调制解码误码率为 0(无噪声条件下)

ID:12200714258449979

BeyondToday

QPSK调制解调是FPGA实现中的一种重要技术。在FPGA开发中,我们不仅可以实现QPSK调制解调,还能支持FSM、MSK、DBPSK、DQPSK、8PSK、16QAM等多种信号调制解调方式。

当前,对于QPSK调制解调的FPGA实现,我们主要使用vivado和modelsim两种工具。而对于quartus的支持,目前还没有进行开发。在QPSK调制中,主要包括了串并转换、差分编码、上采样(插值)、成形滤波、载波相乘等关键步骤。

首先是调制部分。调制过程中,我们需要完成串并转换,将串行数据转换为并行数据。同时,对于QPSK调制来说,差分编码也是必不可少的一步。这一步骤可以帮助我们提高抗噪声能力和可靠性。另外,上采样(插值)也是调制过程中的一个关键环节。通过上采样,我们能够增加采样点的数量,从而提高调制信号的质量。最后,成形滤波和载波相乘则能够进一步优化调制效果。

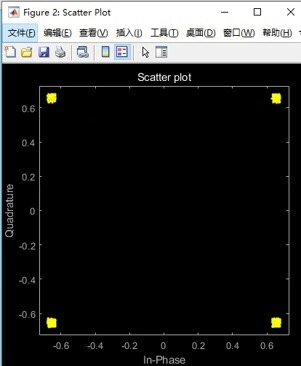

接下来是解调部分。解调过程中,我们需要进行一系列的数字处理步骤。首先是数字正交下变频,该步骤能够将接收到的信号转换到基带频率。然后是低通滤波,通过滤除高频噪声,我们能够获得更加清晰的信号。符号同步和载波同步则可以帮助我们恢复发送方的时钟和载波信息。相差调整则是为了消除解调过程中可能存在的相位差。硬判决是解调的关键一步,通过硬判决,我们可以准确地识别接收到的信号。最后,差分解码和并串转换则是为了将解调后的并行数据转换为串行数据。

QPSK调制解调的误码率可以达到0,在无噪声条件下,可以完美实现信号传输。这为我们的应用提供了更高的可靠性。

综上所述,QPSK调制解调在FPGA实现中具有重要的意义。通过使用vivado和modelsim等工具,我们能够实现多种信号调制解调方式。无论是调制过程中的串并转换、差分编码、上采样、成形滤波、载波相乘,还是解调过程中的数字正交下变频、低通滤波、符号同步、载波同步、相差调整、硬判决、差分解码、并串转换,都能够帮助我们实现高可靠性的信号传输。

【相关代码,程序地址】:http://fansik.cn/714258449979.html

2749

2749

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?